Merancang perangkat elektronik menggunakan modul memori DDR SDRAM cepat membutuhkan perhatian khusus untuk integritas sinyal. Artikel ini berbicara tentang alat pemodelan modern untuk memecahkan masalah seperti itu.Saat ini, hampir semua elektronik modern dilengkapi dengan modul memori. Server, komputer, telepon pintar, konsol game, navigator GPS dan sebagian besar perangkat lain dirancang berdasarkan prosesor dan FPGA. Perangkat semacam itu membutuhkan memori berkecepatan tinggi dengan bandwidth saluran besar atau memori dual-frequency (DDR). Dengan setiap generasi baru DDR SDRAM (memori dinamis sinkron dengan akses acak dan kecepatan transfer data berlipat ganda), kecepatan pertukaran data, kapasitas, konsumsi memori berkurang.

Saat merancang papan sirkuit cetak perangkat dengan memori DDR, sejumlah kesulitan dapat muncul, salah satunya adalah masalah integritas sinyal. Artikel ini membahas masalah memastikan integritas sinyal di perangkat yang menggunakan memori DDR.

Kebisingan dan jitter dari sinyal data digital

Ketika menerima / mentransmisikan sinyal clock bus memori dari pengontrol ke sirkuit mikro, berbagai gangguan dapat terjadi karena jitter yang dimiliki oleh pemancar dan penerima, kehilangan saluran transmisi, kebisingan dan gangguan. Semua ini mengarah pada munculnya jitter dan distorsi bentuk sinyal antarmuka digital.

Setiap energi yang tidak diinginkan yang ditambahkan ke sinyal ideal dapat dianggap sebagai noise. Hal ini dapat disebabkan oleh gangguan dari saluran tetangga, saluran transmisi yang dirancang buruk, impedansi tidak konsisten, dan faktor-faktor lain yang menyebabkan pengaburan bagian depan pulsa. Dengan tidak adanya noise, sinyal aktual identik dengan ideal.

Setiap penyimpangan dari bentuk gelombang ideal mempengaruhi integritasnya. Deviasi waktu (jitter) dan deviasi amplitudo / tegangan (noise) juga memengaruhi kinerja sistem. Jika Anda tidak memastikan integritas sinyal, sistem DDR akan menggunakan informasi yang salah, yang secara signifikan akan meningkatkan intensitas kesalahan bit BER (Bit Error Rate). Pada akhirnya, sistem akan bekerja secara salah dan tidak efisien.

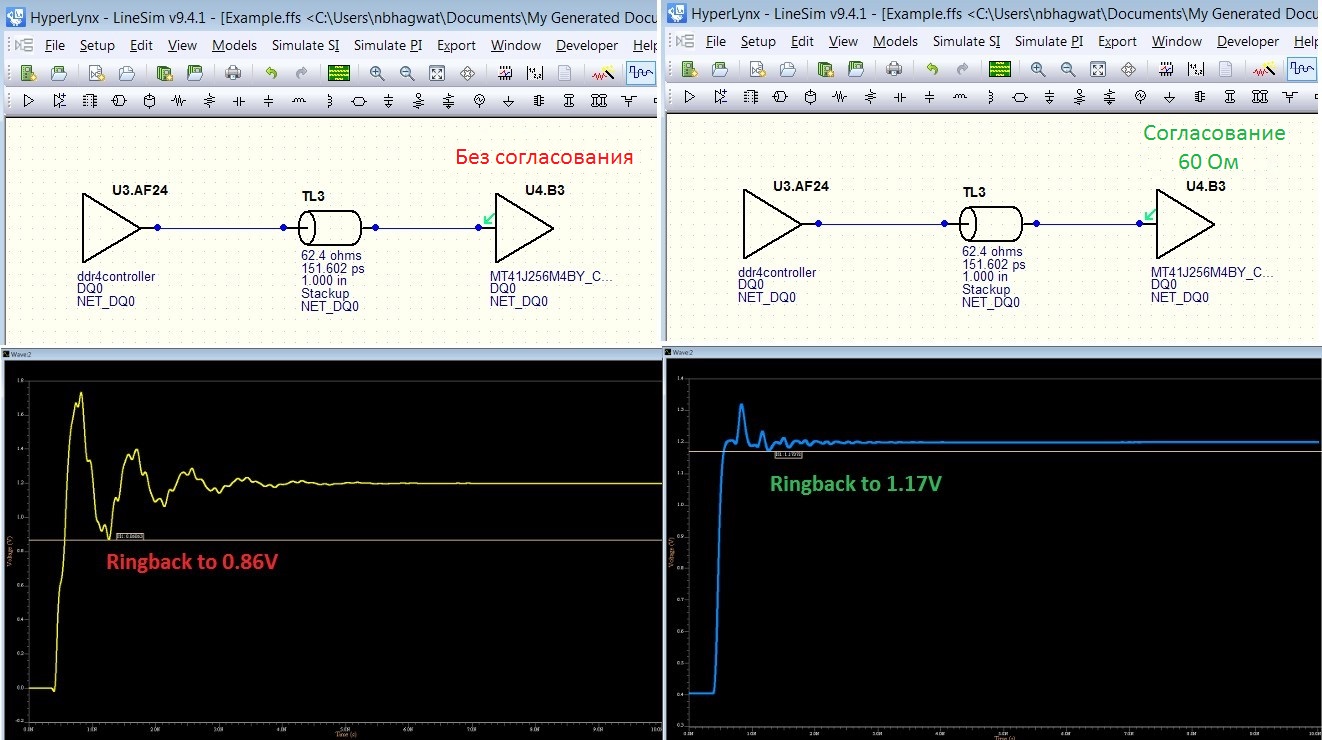

Pertimbangkan contoh spesifik. Jika insinyur menghubungkan pemancar ke penerima yang tidak konsisten yang terletak agak jauh darinya, bentuk gelombang akan serupa dengan yang ditunjukkan pada Gambar 1a: di sini Anda dapat dengan jelas melihat "dering" pada 0,86 V dan emisi dorongan palsu pada 1,75 V pada sinyal 1,2 V. Semua ini dapat menyebabkan kerusakan logika DDR4 dan, jika papan sirkuit dirancang dengan topologi seperti itu, maka dengan 100% kemungkinan kesalahan akan terjadi dalam aliran data, yang, pada gilirannya, dapat menyebabkan operasi sistem yang tidak benar. .

Secara teoritis, adalah mungkin untuk menyelesaikan masalah dengan "dering" dan emisi dengan mengurangi panjang saluran transmisi, tetapi, sayangnya, ini jarang berhasil dalam praktiknya. Cara yang paling efektif adalah mencocokkan penerima / pemancar dengan impedans, akibatnya tingkat kebisingan berkurang, dan bentuk sinyal menjadi jauh lebih baik (lihat Gambar 1b).

Fig. 1. Topologi mengalami masalah dengan kualitas sinyal: a) sebelum koordinasi b) setelah koordinasi

Fig. 1. Topologi mengalami masalah dengan kualitas sinyal: a) sebelum koordinasi b) setelah koordinasiDalam hal ini, muncul pertanyaan tentang peringkat persetujuan mana yang akan digunakan dan bagaimana menghitungnya, karena bahkan perubahan kecil pada peringkat dapat secara signifikan mempengaruhi kinerja sistem. Satu-satunya cara untuk mengatasi masalah ini adalah dengan mensimulasikan, khususnya, menggunakan penyihir rekonsiliasi interaktif yang digunakan dalam HyperLynx.

Masalah Pengaturan Waktu dalam DDRx

Karena bus paralel yang beroperasi pada frekuensi gigahertz, seperti DDR3 / 4, semakin banyak digunakan dalam desain papan sirkuit cetak, masalah integritas sinyal menjadi sangat akut. DDR3 SDRAM, misalnya, berbeda secara signifikan dalam hal kecepatan dan kinerja frekuensi dari DDR2: frekuensi clock maksimum DDR2 adalah 800 MHz, dan frekuensi maksimum DDR3 adalah 1600 MHz. Karena pengurangan tegangan suplai sel, pencipta RAM tipe baru berhasil mengurangi konsumsi energinya sebanyak 15%, yang, mengingat kinerja DDR2 yang mengesankan, dapat disebut sebagai terobosan nyata. DDR3 menggunakan topologi perintah / alamat / kontrol bus "fly-by" jaringan dengan pencocokan intra-modul (ODT). Pada saat yang sama, DDR3 menciptakan masalah baru integritas sinyal, khususnya, yang terkait dengan sirkuit ODT, kecepatan data yang lebih tinggi, dan distorsi waktu.

Terlepas dari kenyataan bahwa ada pengontrol yang melakukan kalibrasi baca / tulis otomatis, mengoptimalkan interval waktu, pengembang perlu memastikan waktu yang tepat. Batas waktu pada antarmuka DDR3 sangat kecil sehingga pendekatan empiris untuk optimasi tidak lagi cukup, dan untuk menjamin pengoperasian antarmuka dengan kecepatan tinggi, diperlukan analisis terperinci dari rangkaian tersebut.

Hubungan temporal yang kompleks seperti itu sulit untuk dianalisis tanpa bantuan alat tambahan. Untuk mengidentifikasi dan menghilangkan kemungkinan masalah secara umum atau untuk menghitung hubungan waktu yang kompleks, insinyur harus melakukan analisis hubungan sebab akibat, yang merupakan tugas yang kompleks dan memakan waktu.

Masalah desain seperti itu sering menyebabkan keterlambatan perencanaan proyek dan, sebagai akibatnya, secara signifikan meningkatkan waktu yang diperlukan untuk produk jadi untuk memasuki pasar. Alat simulasi canggih dan kuat dapat membantu insinyur menemukan dan memperbaiki kesalahan dengan mengoptimalkan sinyal ke level BER yang dapat diterima.

Analisis Integritas Sinyal Sistem DDR SDRAM

Komite Standardisasi Teknik Semikonduktor JEDEC telah menyetujui daftar persyaratan yang harus diikuti ketika mengembangkan produk berkualitas. Sangat penting bahwa DDR SDRAM memenuhi persyaratan ini untuk memastikan operasi yang tepat dan untuk mencegah masalah integritas sinyal. Namun, melakukan semua pengukuran dan perhitungan yang diperlukan seringkali penuh dengan banyak kesulitan.

Terkadang perhitungan ini dapat dihindari sama sekali dengan secara ketat mengikuti petunjuk tata letak yang disediakan oleh vendor pengontrol. Tetapi bagaimana jika rekomendasi semacam itu tidak dapat dilaksanakan karena berbagai keterbatasan dalam proyek tertentu? Apa yang harus dilakukan jika perlu banyak waktu untuk memastikan bahwa proyek memenuhi semua rekomendasi dan persyaratan? Dalam situasi seperti itu, Anda perlu menggunakan alat untuk memverifikasi proyek dengan cepat sebelum memasukkannya ke dalam produksi.

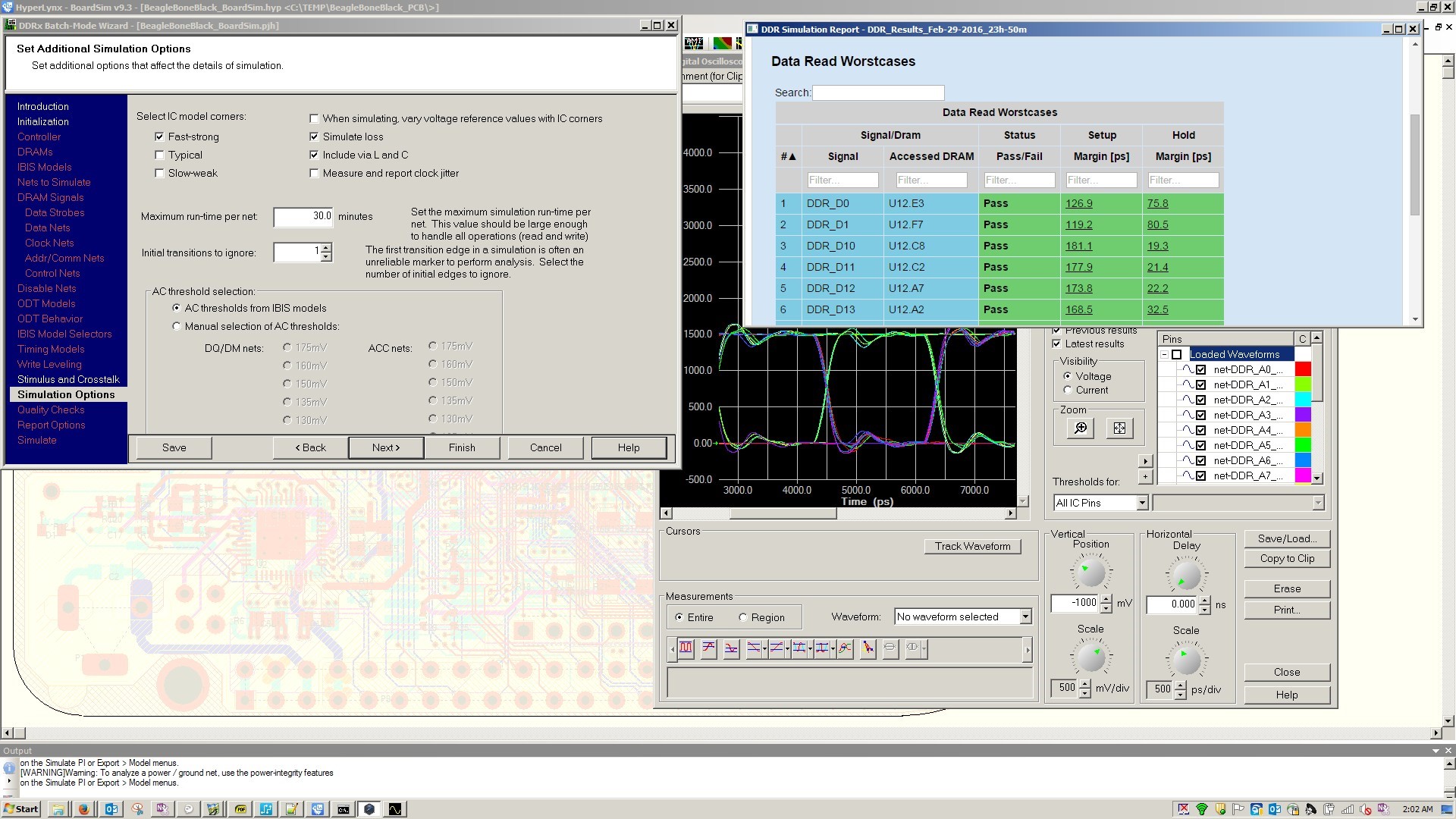

Menggunakan HyperLynx DDR (lihat Gambar 2), Anda dapat mensimulasikan seluruh saluran DDR dalam satu iterasi. Untuk melakukan ini, Anda hanya perlu mengikat model perangkat yang sesuai yang tersedia di situs web produsen. Setelah itu, waktu setup untuk simulasi hanya akan memakan waktu sepuluh menit, yang akan memungkinkan pemodelan lebih lanjut tanpa penundaan.

Fig. 2. Pemodelan dengan HyperLynx DDR Interactive Helper

Fig. 2. Pemodelan dengan HyperLynx DDR Interactive HelperProses pengaturan secara intuitif sederhana, karena semua parameter yang diperlukan untuk mengatur simulasi diminta oleh asisten secara interaktif. Pengguna hanya memasukkan informasi yang relevan, seperti pilihan model IBIS untuk pengontrol dan perangkat memori, kecepatan transfer untuk siklus baca / tulis, ODT, dll. Semua konfigurasi yang dibuat dapat disimpan untuk penggunaan di masa mendatang, yang akan mengurangi waktu setup dalam proyek-proyek mendatang. Simulasi dapat dilakukan sebelum atau setelah pelacakan, membantu menentukan persyaratan untuk tumpukan PCB.

Analisis hasil simulasi

Simulasi mencakup analisis integritas sinyal dan sinkronisasi seluruh bus DDR. Setelah menyelesaikan proses simulasi, laporan dibuat yang mencakup data pada bagian (tidak lulus) dari cek, sesuai dengan informasi konfigurasi dan data yang dimasukkan dalam asisten interaktif. Hasilnya dapat disaring dan diatur dengan baik untuk studi yang cermat tentang masalah waktu dan integritas sinyal dalam siklus baca / tulis data, dalam bus alamat dan komando atau sirkuit diferensial. Semua hasil laporan terkait dengan data simulasi yang sesuai, untuk akses cepat ke alat untuk melihat bentuk gelombang sinyal grafis.

Data simulasi dalam mode batch yang dibuat oleh wizard DDRx dapat disimpan ke disk, yang memungkinkan Anda untuk menggunakan osiloskop HyperLynx untuk mensimulasikan beberapa rangkaian secara bersamaan dan untuk mempelajari secara detail masalah integritas sinyal dalam mode offline.

Kesimpulan

DDR SDRAM membuka kemungkinan baru dalam pengembangan perangkat elektronik. Seperti antarmuka kecepatan tinggi lainnya, penggunaan memori DDR memiliki beberapa fitur. Masalah integritas sinyal harus dipelajari dengan cermat untuk menghindari iterasi yang tidak perlu dan mahal dalam pembuatan produk. Pemodelan adalah cara terbaik untuk menyelesaikan masalah ini, memungkinkan Anda untuk memperhitungkan efek akun di level papan, seperti perubahan impedansi dan penundaan waktu, menyediakan kontrol komprehensif atas antarmuka memori. Alat analisis yang kuat akan membantu memastikan bahwa proyek mematuhi rekomendasi JEDEC dan memastikan bahwa produk akhir akan bekerja dengan kinerja dan keandalan yang tinggi.

HyperLynx DDR dapat digunakan bersama oleh banyak perusahaan desain CAD CAD, termasuk PADS dan Xpedition.

Artikel ini diterbitkan dalam jurnal MODERN ELECTRONICS No. 7, 2018 (www.soel.ru)