Pada awal Oktober, Xilinx

memperkenalkan chip Versal baru, dibangun di atas susunan gerbang yang dapat diprogram (

FPGA ). Logika pengoperasian perangkat semacam itu dapat dimodifikasi setiap saat selama penggunaan. Diharapkan bahwa chip akan mempercepat kerja sistem AI dan menemukan aplikasi di jaringan 5G. Rilis prosesor dijadwalkan untuk akhir 2019.

Selanjutnya, kita berbicara tentang perangkat dan bagaimana itu akan membantu jaringan generasi selanjutnya.

/ Flickr / mike mozart / cc

/ Flickr / mike mozart / ccMasalah jaringan 5G

Teknologi 5G menggunakan frekuensi tinggi - 28 GHz dan lebih tinggi - sehingga sinyal ditransmisikan dengan buruk untuk jarak jauh. Kelebihan penyebarannya sangat terhalang oleh dinding rumah. Di kota, ini dapat menyebabkan penurunan kualitas koneksi.

Para ahli

mengatakan bahwa ini akan menjadi hambatan bagi pekerjaan sejumlah besar perangkat IoT, peningkatan aktif dalam jumlah yang

diperkirakan dari tahun 2020 (tepat ketika jaringan 5G penuh akan dikerahkan).

Perangkat yang terhubung, seperti mobil atau gadget medis yang dapat dipakai, harus berkomunikasi secara real time. Ketidakstabilan koneksi dapat mencegah mereka menilai situasi di sekitar mereka secara memadai atau mentransmisikan data penting (misalnya, tentang keadaan kesehatan manusia) ke server organisasi yang melayani. Perusahaan berencana untuk memecahkan masalah ini dengan mengatur sistem antena terdistribusi khusus, namun, kesulitan muncul dengan ini.

Misalnya, sekarang di New York lebih dari seribu BTS dipasang. Untuk menutupi seluruh kota dengan jaringan 5G,

perlu menginstal setengah juta lainnya . Biaya proyek akan jauh lebih tinggi daripada dalam kasus "standar-G" sebelumnya.

Bagaimana Versal membantu menyelesaikan masalah ini

Perangkat Xilinx akan membantu menyelesaikan masalah dengan stabilitas koneksi Internet menggunakan sistem AI, yang dengannya "disetel" untuk bekerja. Chip Versal akan memproses algoritma pembelajaran mesin di jaringan 5G yang mengoptimalkan pola

radiasi antena seluler. Ini akan menghindari sektor yang buta dan memilih mode transmisi data yang sesuai.

Sistem AI juga akan meningkatkan algoritma

serah terima , yang bertanggung jawab untuk mentransfer sesi dari satu stasiun ke stasiun lainnya. Selain itu, jaringan akan memperbaiki sendiri dan beradaptasi, secara otomatis mengarahkan ulang data jika ada simpul yang gagal. Jadi, pengguna 5G akan dapat dengan bebas bergerak di sekitar gedung atau kota tanpa kegagalan koneksi.

Xilinx sudah memiliki pelanggan untuk chip AI untuk 5G. Prosesor versal akan digunakan untuk jaringan di Olimpiade 2020.

Fitur arsitektur chip

Xilinx memperkenalkan konsep Versal pada bulan Oktober. Microcircuit baru

heterogen , yaitu menggunakan beberapa unit komputasi sekaligus. Unit-unit ini dapat berupa prosesor, coprocessor, sirkuit ASIC dan FPGA terintegrasi.

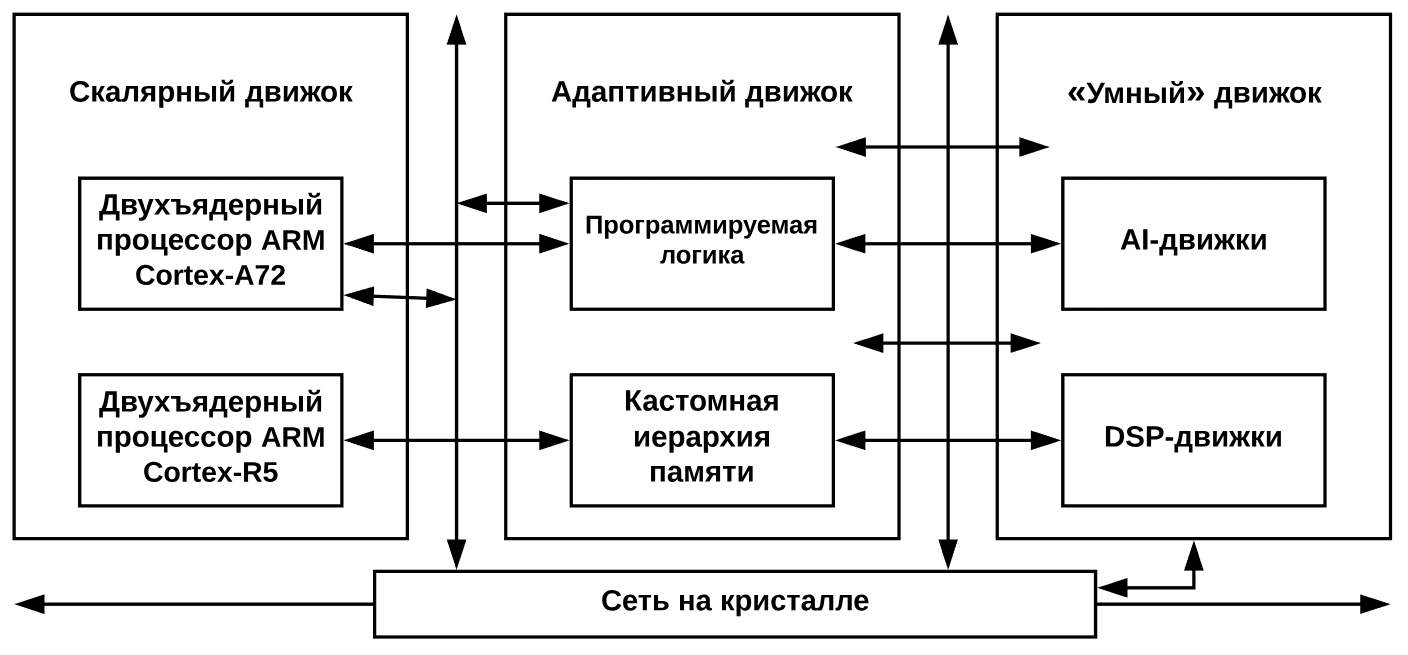

Chip Xilinx baru didasarkan pada versi yang ditingkatkan dari FPGA - arsitektur Adaptive Computer Accelerator Platform (ACAP). Ini terdiri dari empat komponen dasar: mesin

skalar , mesin adaptif, akselerator

vektor (mesin "pintar"), dan jaringan pada chip (NoC - Network-on-Chip) untuk menghubungkan elemen sistem.

Mesin skalar diwakili oleh prosesor dual-core ARM Cortex-A72 dan Cortex-R5. Logika yang dapat diprogram dibangun di atas

elemen logika yang dapat dikonfigurasi dengan

tabel pencarian ,

pemicu , memori, dan blok khusus untuk menghubungkan komponen. Semua ini memungkinkan Anda untuk membangun

hierarki memori , dipertajam untuk tugas komputasi tertentu.

Mesin "pintar" didasarkan pada

arsitektur VLIW , yang diperlukan untuk eksekusi paralel beberapa operasi dalam satu instruksi. Prinsip perhitungan

SIMD juga diterapkan. Struktur seperti itu membantu menyelesaikan masalah MO dan memproses sinyal 5–10 kali lebih cepat daripada sistem klasik. Sedangkan untuk NoC, bandwidth yang dinyatakan adalah 1 Tbps.

Diagram arsitektur ACAP terlihat seperti ini.

Keluarga chip Versal akan diproduksi di TSMC menggunakan teknologi proses

7-nm . Fitur arsitektur lainnya dapat ditemukan dalam dokumen PDF resmi -

Tinjauan arsitektur ASAP dan

ulasan chip Versal .

Sistem ini diprogram dalam C, C ++ dan Python. Menurut pengembang, mereka memilih PL ini, karena menurut

TIOBE , C, C ++ dan Python mereka adalah yang paling populer setelah Java.

Selain itu, bahasa-bahasa ini saling melengkapi. C dan C ++ dikompilasi, yang berarti bahwa kode dapat dijalankan pada bare metal (khususnya, pada FPGA). Python lebih baik daripada orang lain untuk menganalisis data dan bekerja dengan sistem AI. Alasan lain untuk memilih Xilinx adalah dalam studi terpisah pada topik (

PDF ).

Solusi serupa

Chip berbasis FPGA juga sedang dikembangkan oleh perusahaan lain, seperti Intel. Dari produk terbaru perusahaan,

perangkat hybrid Arria dapat dibedakan. Pengembangannya adalah platform dua chip: Xeon E5-2600 v4 dan

Altera Arria 10 .

Menurut Intel, perangkat ini cocok untuk server, pusat data, dan layanan cloud, di mana bebannya sering meningkat secara spasmodik. Prosesor pada FPGA akan membantu memproses data secara paralel, yang akan meningkatkan kinerja sistem secara keseluruhan. Fujitsu, misalnya,

berencana untuk memasok lini server Primergy dengan chip ini pada akhir tahun.

Pelaku pasar lainnya - AMD, ARM, Qualcomm, Samsung dan lainnya - menciptakan organisasi nirlaba

HSA Foundation pada 2012. Perhitungan heterogen dipopulerkan di sana: mereka mengembangkan standar industri, membantu pengembang memasuki pasar dan mensponsori program pendidikan.

Xilinx

percaya bahwa dengan pengembangan sistem AI dan penyebaran jaringan 5G, permintaan untuk platform FPGA akan meningkat. CEO Xilinx Victor Peng

mencatat bahwa satu-satunya penghambat produksi chip secara massal adalah persaingan dari CPU dan GPU, yang mencegah solusi FPGA dari “menangkap” pasar. Tapi, mungkin, lompatan permintaan (jika itu terjadi) tidak diharapkan

sebelum 2020 .

PS Materi tambahan dari blog korporat VAS Experts:

PPS Beberapa artikel segar dari blog kami di Habré: