Selamat siang, pembaca yang budiman! Saya diminta untuk menulis tentang UHCI - well, saya menulis.

Anda mungkin menemukan artikel ini berguna jika, misalnya, Anda tidak memiliki keterampilan menulis yang cukup untuk driver dan membaca dokumentasi untuk perangkat keras. Contoh sederhana: Anda ingin menulis OS untuk mini-PC, sehingga beberapa Windows atau distribusi Linux lainnya tidak mengunduh perangkat keras, dan Anda menggunakan semua kekuatannya secara eksklusif untuk keperluan Anda sendiri.

Apa itu UHCI?

Saya pikir, agar tidak menyemprot lagi pada topik apa dan mengapa, tinggalkan saja tautan ke artikel saya sebelumnya tentang EHCI.

Aduk di siniUHCI - Universal Host Controller Interface, beroperasi sebagai perangkat PCI, tetapi, tidak seperti EHCI menggunakan port, bukan MMIO (Memory-Mapped-IO).

Ketentuan untuk digunakan selanjutnya

- Driver USB (USBD) - driver USB itu sendiri

- HC (Host Controller) - pengendali host, atau hanya UHCI kami

- Host Controller Driver (HCD) - driver yang menghubungkan perangkat keras dan USBD

- Perangkat USB - perangkat USB itu sendiri

Jenis-jenis Transfer Data

Isochronous - transmisi isosynchronous, yang memiliki frekuensi transfer data tertentu. Ini dapat digunakan, misalnya, untuk mikrofon USB, dll.

Interrupt - Kecil, transfer data spontan dari suatu perangkat. Jenis transmisi interupsi mendukung perangkat yang memerlukan interval layanan yang dapat diprediksi tetapi tidak selalu menyediakan aliran data yang dapat diprediksi. Biasa digunakan untuk perangkat seperti papan ketik dan perangkat penunjuk yang mungkin tidak menyediakan data untuk jangka waktu yang lama, tetapi memerlukan respons cepat ketika mereka memiliki data untuk dikirim.

Kontrol - Jenis pengiriman informasi tentang status perangkat, status dan konfigurasi. Jenis transfer Kontrol digunakan untuk menyediakan saluran kontrol dari Host ke perangkat USB. Transmisi kontrol selalu terdiri dari fase pengaturan dan nol atau lebih fase data diikuti oleh fase status. Sangat penting bahwa kontrol transfer ke titik akhir yang diberikan diproses dalam mode FIFO. Jika kontrol dilewatkan ke titik akhir yang sama, interleaving dapat menyebabkan perilaku yang tidak terduga.

Jenis transfer array data secara massal. Digunakan, misalnya, di perangkat MassStorage.

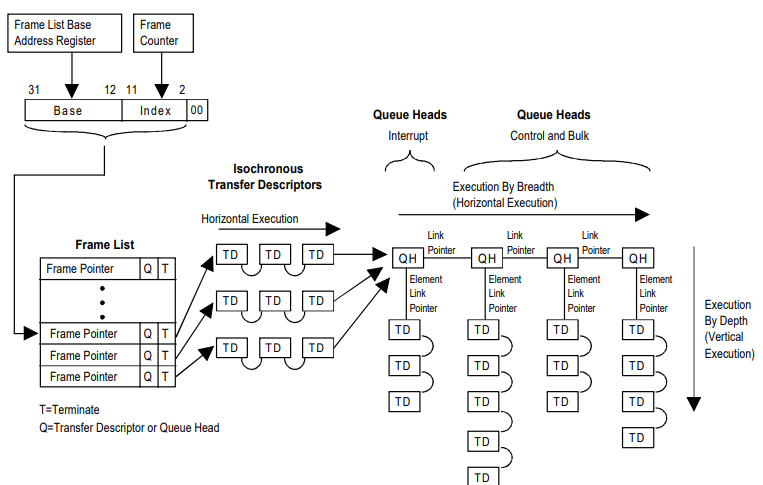

Ini adalah bagaimana distribusi waktu 1ms terlihat seperti - pemrosesan satu frame.

Distribusi waktu

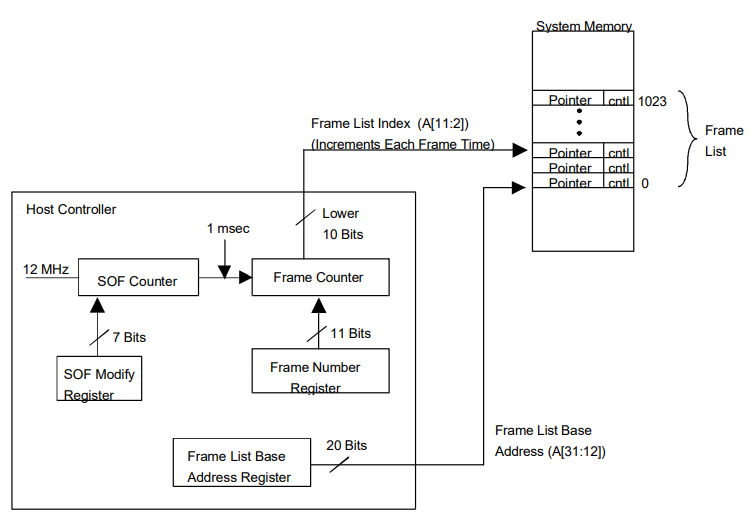

Pengontrol host mendukung pengiriman data real-time dengan menghasilkan paket Start Of Frame (SOF) setiap 1 ms. Paket SOF dihasilkan ketika penghitung SOF di pengontrol host kedaluwarsa (Gambar 3). Pengontrol host menginisialisasi penghitung SOF untuk waktu bingkai 1 ms. Perubahan kecil dapat dibuat untuk nilai ini (dan karenanya periode waktu bingkai) dengan memprogram register perubahan SOF. Fitur ini memungkinkan Anda untuk membuat perubahan kecil pada periode waktu bingkai, jika perlu, untuk mempertahankan sinkronisasi waktu nyata di seluruh sistem USB.

Pengontrol host menyertakan nomor bingkai di setiap paket SOF. Nomor bingkai ini secara unik menentukan periode bingkai secara real time. Kondisi akhir bingkai (EOF) terjadi pada akhir interval waktu 1 ms ketika pengendali host memulai waktu bingkai berikutnya, menghasilkan paket SOF lain dengan nomor bingkai yang sesuai. Selama periode frame, data ditransmisikan sebagai paket informasi. Periode waktu frame diberlakukan secara ketat oleh pengontrol host, dan paket data dalam frame saat ini tidak dapat melampaui EOF (lihat Bab 11 dalam spesifikasi USB). Pengendali host mendukung sinkronisasi pengiriman data antara frame secara real time, menghubungkan nomor frame untuk melakukan entri tertentu dalam daftar frame. Penghitung bingkai pengontrol host menghasilkan nomor bingkai (nilai 11-bit) dan memasukkannya ke dalam setiap paket SOF. Penghitung diprogram melalui register dan setiap periode frame bertambah. Pengontrol host menggunakan 10 bit lebih rendah dari jumlah frame sebagai indeks dalam daftar frame dengan 1024 frame, yang disimpan dalam memori sistem. Jadi, karena penghitung bingkai mengontrol pemilihan entri dari daftar bingkai, pengontrol host memproses setiap entri dalam daftar dalam periode bingkai yang diberikan. Pengontrol host memperluas ke entri berikutnya dalam daftar bingkai untuk setiap bingkai baru. Ini memastikan bahwa transmisi isochronous dilakukan dalam bingkai tertentu.

Gambar 3:

Struktur UHCI

Semuanya persis sama dengan EHCI. Contoh permintaan ke HC:

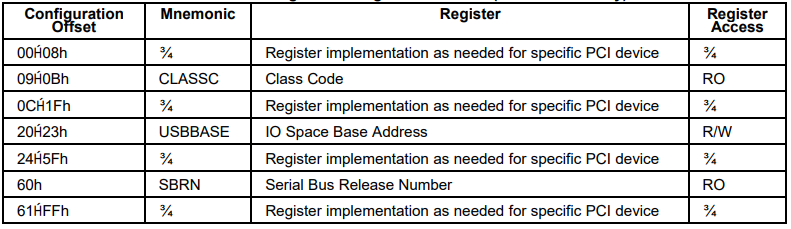

Konfigurasikan dan akses UHCI

Jadi, seperti yang saya katakan sebelumnya, UHCI bekerja melalui port, jadi dari PCI kita perlu mencari tahu basis register UHCI.

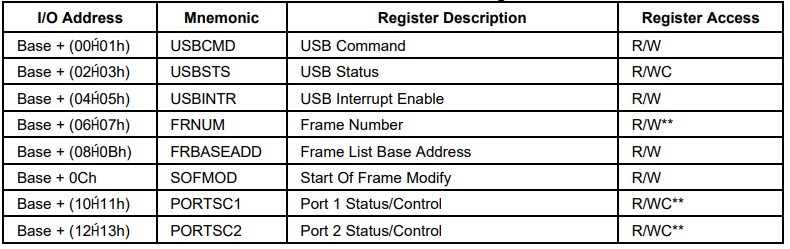

Pada offset 0x20 ada 4 byte - IO Base. Mengenai Basis IO, kita dapat menggunakan register berikut:

Register UHCI

- USBCMD adalah register untuk mengendalikan HC. Bit:

- Bit 6 adalah bendera yang berhasil dikonfigurasikan dan diinisialisasi oleh perangkat.

- Bit 1 - Reset HC. Setel untuk mengatur ulang HC.

- Bit 0 - Run / Stop. Menampilkan status HC. 1 - bekerja, 0 - tidak.

- USBSTS - Status Register. Bit:

- Bit 5 - HC Dihentikan. Terjadi kesalahan, atau pengontrol berhasil menyelesaikan HC Reset.

- Bit 4 - Kesalahan Proses Pengontrol Host. Bit diatur ke 1 ketika kesalahan kritis telah terjadi dan HC tidak dapat melanjutkan antrian dan TD.

- Bit 3 - Kesalahan Sistem Host. Kesalahan PCI.

- Bit 1 - Interupsi Kesalahan. Menunjukkan bahwa telah terjadi kesalahan dan HC menghasilkan interupsi.

- Bit 0 - Interrupt. Menunjukkan bahwa HC menghasilkan interupsi.

- USBINTR - Daftar pengaturan interupsi. Bit:

- Bit 2 - IOC - Interrupt on complete - menghasilkan interrupt pada akhir transaksi.

- FRNUM - Jumlah bingkai saat ini (Ambil & 0x3FF untuk nilai yang benar).

- FLBASEADD - Frame List Base Address - alamat dari daftar frame.

- PORTSC - Status port dan kontrol - status dan register kontrol port. Bit:

- Bit 9 - Port Reset - 1 - port untuk mengatur ulang.

- Bit 8 - menunjukkan bahwa perangkat berkecepatan rendah terhubung ke port

- Bit 3 - Menunjukkan bahwa port on state telah berubah

- Bit 2 - Menunjukkan apakah port diaktifkan

- Bit 1 - menunjukkan bahwa status perangkat terhubung ke port

- Bit 0 - menunjukkan bahwa perangkat terhubung ke port.

Struktur

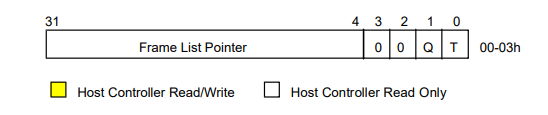

Pointer daftar penunjuk

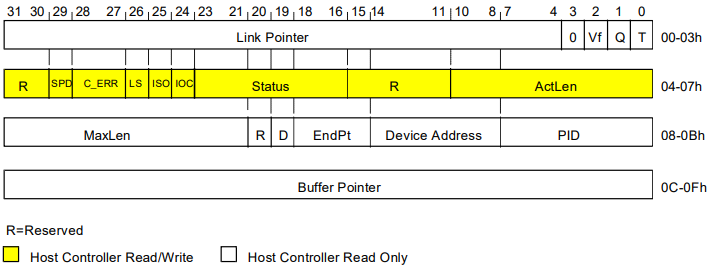

Descrptor transfer

KONTROL DAN STATUS TD

. Bit:

- Bit 28-27 - penghitung kesalahan, mirip dengan EHCI.

- Bit 26 - 1 = Perangkat berkecepatan rendah, 0 = Perangkat berkecepatan penuh.

- Bit 25 - 1 = TD sinkron

- Bit 24 - IOC

- Bit 23-16 - Status:

- Bit 23 - Menunjukkan bahwa itu adalah TD aktif

- Bit 22 - Stalled

- Bit 21 - Kesalahan Penyangga Data

- Bit 20 - Babble Terdeteksi

- Bit 19 - NAK

- Bit 10-0: Jumlah byte yang dikirimkan oleh pengontrol host.

Token TD

- Bits 31:21 - Max Packet Len, mirip dengan EHCI

- Bit 19 - Data Toggle, Mirip dengan EHCI

- Bit 18:15 - Nomor Titik Akhir

- Bit 18:14 - alamat perangkat

- Bits 7: 0 - PID. Dalam = 0x69, Keluar = 0xE1, Pengaturan = 0x2D

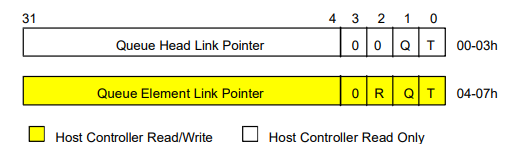

Kepala antrian

Kode

Inisialisasi dan konfigurasi HC:

PciBar bar; PciGetBar(&bar, id, 4); if (~bar.flags & PCI_BAR_IO) {

Permintaan titik akhir dan kontrol: