Pendahuluan

Proyek kami mengimplementasikan sistem deteksi tepi waktu-nyata berdasarkan pengambilan bingkai gambar dari kamera OV7670 dan streaming ke monitor VGA setelah menerapkan filter skala abu-abu dan operator Sobel. Desain kami dibangun di atas papan FPGA Cyclone IV yang memungkinkan kami untuk mengoptimalkan kinerja menggunakan fitur-fitur canggih dari perangkat keras tingkat rendah dan komputasi paralel yang penting untuk memenuhi persyaratan sistem waktu-nyata.

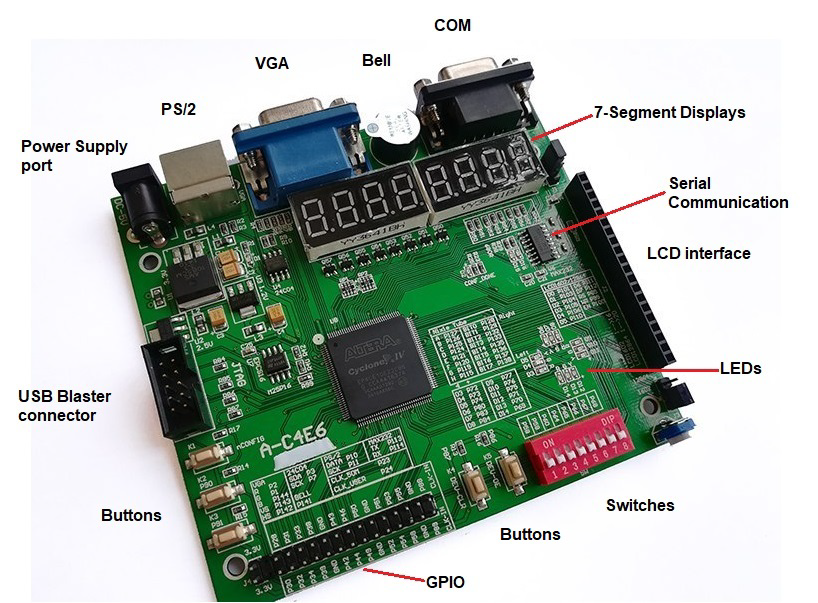

Kami menggunakan papan pengembangan ZEOWAA FPGA yang didasarkan pada Siklon IV (EP4CE6E22C8N). Kami juga menggunakan Quartus Prime Lite Edition sebagai lingkungan pengembangan dan Verilog HDL sebagai bahasa pemrograman. Selain itu, kami menggunakan antarmuka VGA bawaan untuk menggerakkan monitor VGA, dan GPIO (Pin Umum untuk Input dan Output) untuk menghubungkan perangkat keras eksternal dengan papan kami.

Arsitektur

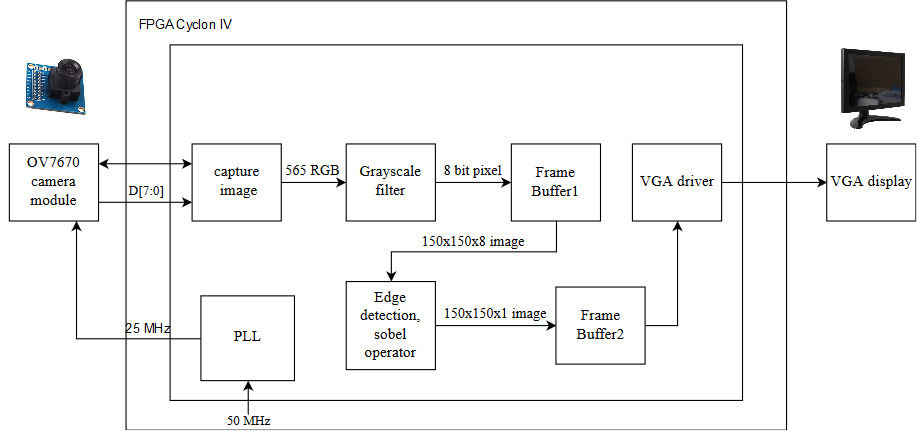

Desain kami dibagi menjadi 3 bagian utama:

- Membaca piksel data dari kamera.

- Menerapkan algoritme deteksi tepi kami (konverter skala abu-abu dan operator Sobel).

- Menampilkan gambar akhir dengan berinteraksi dengan monitor VGA.

Juga, ada penyimpanan memori antara antara membaca / menulis data dan mengoperasikan data ini. Untuk tujuan ini, kami menerapkan dua buffer yang berfungsi sebagai ruang sementara untuk piksel sebelum digunakan.

Perhatikan bahwa setelah kami mengambil piksel dari kamera, kami tidak menyimpannya langsung ke buffer memori menengah. Sebagai gantinya, kami mengonversinya menjadi skala abu-abu lalu kami menyimpannya di buffer. Ini karena menyimpan piksel abu-abu 8-bit membutuhkan lebih sedikit memori daripada menyimpan piksel berwarna 16-bit. Kami juga memiliki buffer lain yang menyimpan data setelah menerapkan operator Sobel untuk membuatnya siap ditampilkan di monitor.

Berikut adalah detail tentang implementasi arsitektur kami:

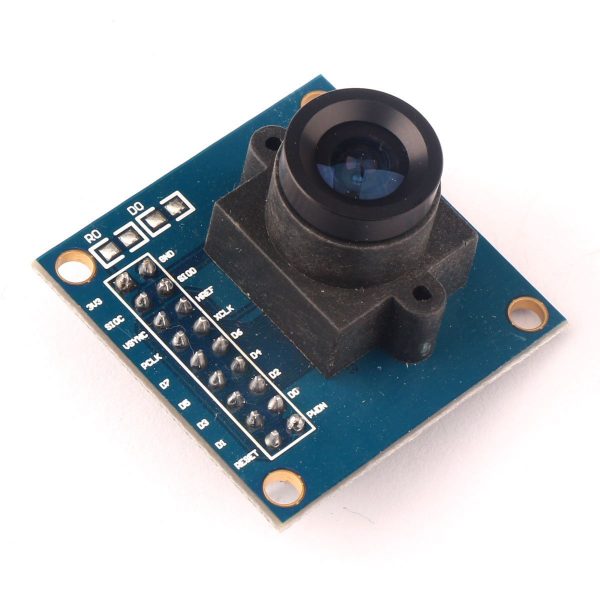

Kamera

Kami menggunakan kamera OV7670 yang merupakan salah satu modul kamera termurah yang kami temukan. Selain itu, kamera ini dapat bekerja pada 3.3V dan tidak memerlukan protokol komunikasi yang sulit seperti I2c atau SPI untuk mengekstrak data gambar. Ini hanya membutuhkan antarmuka SCCB yang mirip dengan antarmuka I2c untuk mengatur konfigurasi kamera dalam hal format warna (RGB565, RGB555, YUV, YCbCr 4: 2: 2), resolusi (VGA, QVGA, QQVGA, CIF, QCIF) dan banyak pengaturan lainnya.

Video terdiri dari bingkai yang sedang diubah pada tingkat tertentu. Satu bingkai adalah gambar yang terdiri dari baris dan kolom piksel di mana setiap piksel diwakili oleh nilai warna. Dalam proyek ini, kami menggunakan konfigurasi default kamera di mana ukuran frame adalah resolusi VGA 640 x 480 (0,3 Megapixels), dan format warna piksel adalah RGB565 (5 bit untuk Merah, 6 bit untuk Biru, 5 bit untuk Hijau ) dan laju perubahan frame adalah 30 fps.

Di bawah ini, koneksi kamera ke FPGA menggunakan GPIO yang ada di papan pengembangan:

| Sematkan di kamera | pin di FPGA | Deskripsi | Sematkan di kamera | pin di FPGA | Deskripsi |

|---|

| 3.3V | 3.3V | Catu Daya (+) | GND | GND | Level Pasokan Tanah (-) |

| Sdioc | GND | Jam SCCB | SDIOD | GND | Data SCCB |

| VSYNC | P31 | Sinkronisasi vertikal | Href | P55 | Sinkronisasi horizontal |

| PCLK | P23 | Jam Pixel | Xclk | P54 | Jam Sistem Input (25 MHz) |

| D7 | P46 | Bit data ke-8 | D6 | P44 | Bit data ke-7 |

| D5 | P43 | Bit data ke-6 | D4 | P42 | Bit data ke-5 |

| D3 | P39 | Bit data ke-4 | D2 | P38 | Bit 3 data |

| D1 | P34 | Bit 2 data | D0 | P33 | Bit data pertama |

| RESET (Aktif Rendah) | 3.3V | Setel ulang pin | PWDN | GND | Matikan pin |

Perhatikan bahwa kami tidak menggunakan antarmuka SCCB untuk konfigurasi. Jadi, kami meletakkan kabel yang sesuai di tanah untuk mencegah sinyal mengambang yang dapat memengaruhi data.

Untuk menyediakan jam 25MHz untuk kamera kami menggunakan Phase-Locked Loop (PLL) yang merupakan sistem kontrol frekuensi loop tertutup untuk menyediakan jam yang dibutuhkan dari 50MHz yang disediakan dari papan. Untuk mengimplementasikan PLL, kami menggunakan alat katalog IP internal di dalam perangkat lunak Quartus.

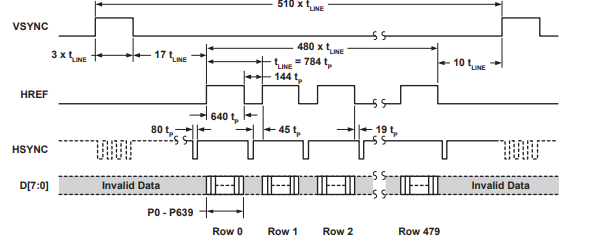

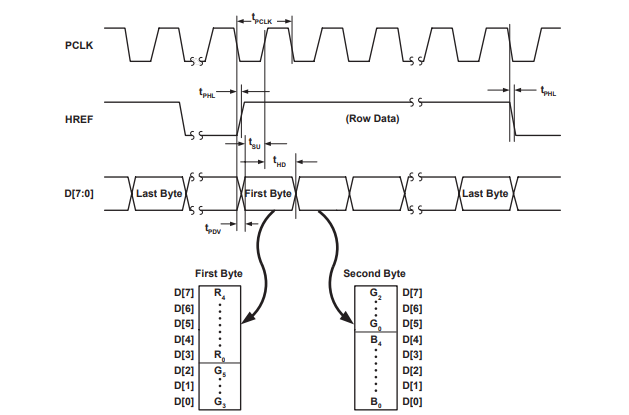

Kamera ini menggunakan sinyal sinkronisasi vertikal (VSYNC) untuk mengontrol proses pengiriman frame dan sinyal sinkronisasi horisontal (HREF) untuk mengontrol pengiriman setiap baris frame. Kamera ini hanya menggunakan 8 baris data (D0-D7) untuk mentransfer bit yang mewakili nilai warna piksel saat kamera membagi nilai 16-bit RGB pixel menjadi 2 (8-bit) bagian dan mengirim masing-masing secara terpisah.

Gambar-gambar di bawah ini dari lembar data modul kamera OV7670 menggambarkan sinyal sinkronisasi vertikal dan horizontal.

Pengubah skala abu-abu

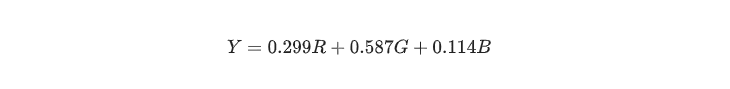

Untuk menghasilkan gambar skala abu-abu dari gambar berwarna aslinya, banyak faktor yang harus dipertimbangkan, karena gambar mungkin kehilangan kontras, ketajaman, bayangan, dan struktur. Selain itu, gambar harus menjaga pencahayaan relatif ruang warna. Beberapa teknik linear dan non-linear digunakan untuk mengubah gambar warna menjadi skala abu-abu. Oleh karena itu, untuk mencapai tujuan kami, kami menggunakan konversi kolorimetri (pelestarian luminance perceptual) ke skala abu-abu yang ditunjukkan dalam persamaan berikut:

Untuk meningkatkan kinerja dalam hal perhitungan, lebih cepat menggunakan operator shift. Oleh karena itu, persamaan di atas dapat direduksi menjadi sebagai berikut:

Akibatnya, setelah mengambil nilai piksel (565 RGB) dari kamera, dapat segera dikonversi menjadi nilai piksel abu-abu 8-bit yang menerapkan rumus konversi. Gambar berskala abu-abu lebih mudah disimpan dalam memori dan cukup cepat untuk melayani fungsionalitas sistem waktu-nyata kita karena kerumitannya mendekati logaritmik dan FPGA dapat membuatnya lebih cepat dengan mengakses memori secara paralel. Setelah itu, gambar yang disimpan siap untuk menerapkan algoritma deteksi tepi.

Kami memiliki 2 buffer, yang pertama digunakan untuk menyimpan piksel setelah mengubahnya menjadi skala abu-abu dan ukurannya (8-bit x 150 x 150) dan yang kedua digunakan untuk menyimpan piksel setelah menerapkan operator Sobel dan ambang untuk nilai output dan ukurannya (1-bit x 150 x 150). Sayangnya, 150 x 150 buffer tidak menyimpan seluruh gambar dari kamera tetapi hanya menyimpan sebagian saja.

Kami telah memilih ukuran buffer kami sebagai 150 x 150 karena keterbatasan memori cyclone IV karena hanya memiliki 276.480 Kbit sementara dua buffer kami mengambil 202.500 Kbit (150 x 150 x 9) yang setara dengan 73,24% dari memori asli siklon IV dan sisa memori digunakan untuk menyimpan algoritma dan arsitektur. Selanjutnya, kami mencoba (170 x 170) sebagai ukuran untuk buffer kami yang mengambil 94,07% dari memori yang tidak meninggalkan cukup ruang untuk mengimplementasikan algoritma.

Buffer kami adalah True Dual-port RAM yang dapat membaca dan menulis dalam siklus clock yang berbeda secara bersamaan. Di sini, kami menciptakan implementasi alih-alih menggunakan alat katalog IP di dalam perangkat lunak Quartus untuk lebih fleksibel dalam penerapannya. Kami juga mengintegrasikan kedua buffer hanya dalam satu modul alih-alih memiliki modul yang berbeda.

Operator sedan

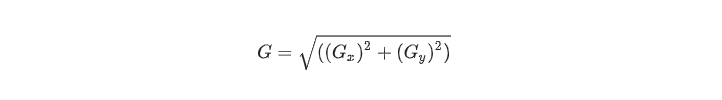

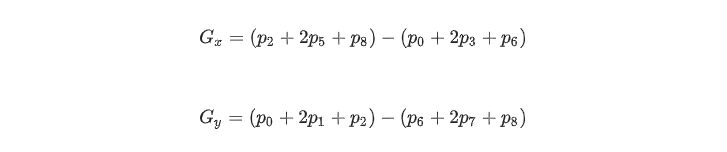

Kami menggunakan operator deteksi tepi derivatif pertama yang merupakan operator gradien area matriks yang menentukan perubahan luminansi antara piksel yang berbeda. Untuk lebih tepatnya, karena ini adalah metode yang mudah dan efisien dalam hal penggunaan memori dan kompleksitas waktu, kami menggunakan operator gradien Sobel yang menggunakan kernel 3x3 yang berpusat pada piksel yang dipilih untuk mewakili kekuatan tepi. Operator Sobel adalah besarnya gradien yang dihitung oleh:

Di mana Gx dan Gy dapat direpresentasikan menggunakan masker konvolusi:

Perhatikan bahwa piksel yang lebih dekat ke tengah topeng diberi bobot lebih. Juga, G x dan G y dapat dihitung sebagai berikut:

Di mana p i adalah pixel yang sesuai dalam array berikut, dan nilai p i adalah nilai skala abu-abu 8-bit:

Ini adalah praktik umum untuk memperkirakan besarnya gradien operator Sobel dengan nilai absolut:

Perkiraan ini lebih mudah untuk diterapkan dan lebih cepat untuk dihitung yang lagi-lagi berfungsi fungsionalitas kami dalam hal waktu dan memori.

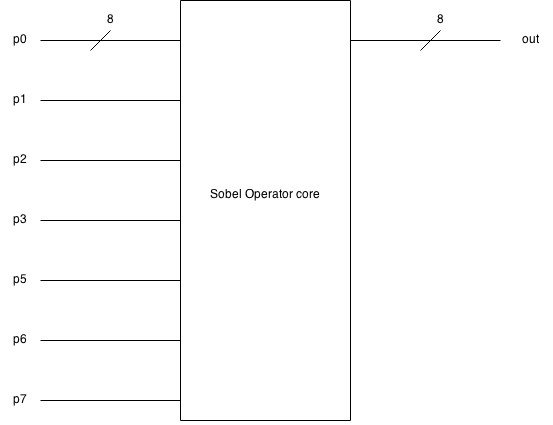

Berikut adalah diagram blok operator Sobel yang mengambil 9 (8-bit) piksel sebagai input dan menghasilkan (8 bit) nilai piksel:

Dan di sini adalah diagram blok terinci dari implementasi operator Sobel.

Monitor Vga

Papan pengembangan kami memiliki antarmuka VGA built-in yang memiliki kemampuan untuk hanya menampilkan 8 warna pada monitor VGA karena hanya memiliki 3-bit untuk mengontrol warna melalui satu bit untuk Merah, satu untuk Hijau dan satu untuk Biru. Ini membuat debugging kami lebih sulit karena mencegah kami untuk menampilkan gambar dari kamera langsung ke monitor. Jadi, kami menggunakan ambang untuk mengubah piksel menjadi nilai 1-bit sehingga dimungkinkan untuk menampilkan gambar.

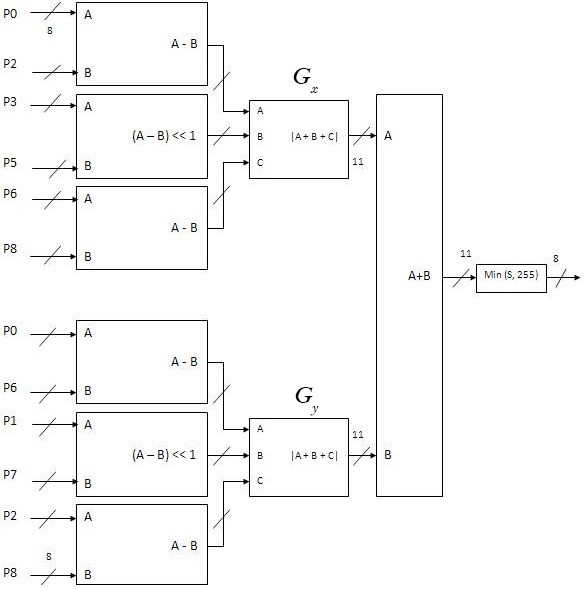

Antarmuka VGA berfungsi seperti kamera karena mengoperasikan piksel demi piksel dari sudut kiri atas ke sudut kanan bawah. Menggunakan sinkronisasi vertikal dan horizontal, kita dapat menyinkronkan sinyal yang mengontrol aliran piksel.

Sinyal sinkronisasi vertikal digunakan untuk mewakili indeks baris sedangkan sinyal sinkronisasi horizontal digunakan untuk mewakili indeks kolom. Kedua sinyal juga menggunakan teras depan, pulsa sinkronisasi, dan teras belakang sebagai sinyal sinkronisasi untuk memisahkan baris lama dari baris baru dalam sinyal sinkronisasi horizontal, dan frame lama dari bingkai baru dalam sinyal sinkronisasi vertikal.

Kami menggunakan antarmuka sinyal VGA standar (640 x 480 @ 60 MHz). Semua spesifikasi standar sinyal dijelaskan di sini .

Pengujian

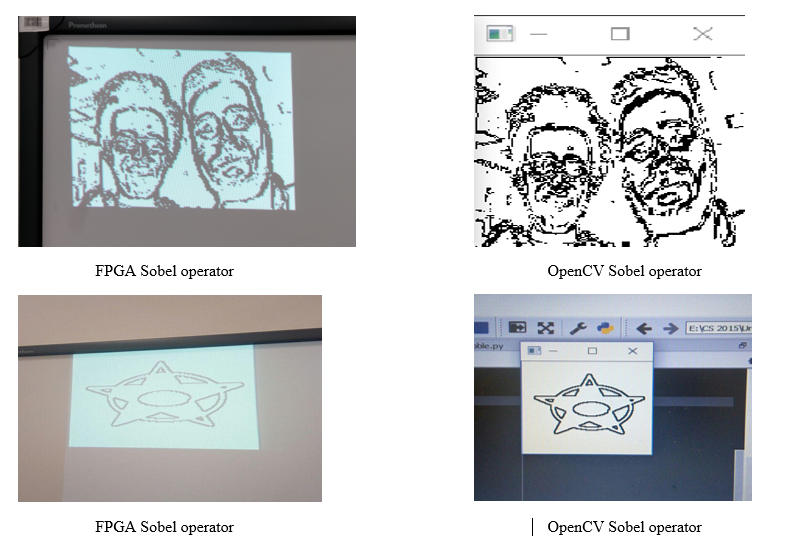

Sebelum menyatukan semuanya dan menguji sistem waktu-nyata. Kami pertama-tama harus menguji setiap bagian secara terpisah. Pada awalnya, kami memeriksa nilai dan sinyal yang datang dari kamera dengan menampilkan nilai piksel tertentu. Kemudian, dengan bantuan OpenCV menggunakan bahasa pemrograman Python, kami dapat menerapkan filter Sobel pada beberapa gambar untuk membandingkan hasilnya dengan algoritma kami dan memeriksa kebenaran logika kami. Selain itu, kami menguji buffer dan driver VGA kami dengan menampilkan beberapa gambar statis pada monitor VGA setelah menerapkan operator dan thresholding Sobel. Selanjutnya, dengan mengubah nilai ambang, keakuratan gambar akan terpengaruh.

Kode python yang kami gunakan:

Hasil

Sebagai hasil dari implementasi kami, kami mendapatkan sistem deteksi tepi waktu nyata yang menghasilkan gambar 150x150 setelah menerapkan filter skala abu-abu dan operator Sobel. Sistem yang diimplementasikan menyediakan 30 fps. Kamera beroperasi pada clock 25MHz dan sistem, secara umum, memenuhi tenggat waktu nyata tanpa jeda yang nyata. Selain itu, nilai ambang batas dapat memengaruhi jumlah detail dan noise pada gambar akhir.

Berikut ini adalah perbandingan antara operator Sobel pada FPGA dan operator sobel OpenCV:

Di bawah ini adalah video ilustratif dari hasilnya:

Inilah tautan repositori di Github yang memiliki semua kode sumber.

Perbaikan di masa depan

Karena kami menggunakan FPGA Cyclone IV, kami terbatas pada kapasitas memorinya dan jumlah gerbang logika. Oleh karena itu, sebagai peningkatan di masa mendatang, kami dapat menggunakan sumber memori eksternal atau kami dapat mengimplementasikan pekerjaan kami di papan lain sehingga kami dapat menampilkan semua piksel dari gambar yang diterima dari kamera.

Selain itu, meskipun operator Sobel cepat dan mudah diimplementasikan, operator ini sangat sensitif terhadap kebisingan. Untuk menghilangkan noise yang dihasilkan, kita dapat menggunakan filter noise seperti filter median non-linier yang bekerja dengan baik dengan sistem kita jika kita memiliki cukup memori untuk mengimplementasikan buffer ketiga. Ini akan menghasilkan gambar yang lebih halus dengan fitur tajam dihapus.

Oleh karena itu, kami menggunakan antarmuka VGA bawaan dari FPGA yang hanya dapat menghasilkan gambar 3-bit. Jadi, kami tidak dapat menampilkan gambar grayscaled karena perlu 8 bit untuk ditampilkan. Akibatnya, mengimplementasikan antarmuka lain atau menggunakan papan yang lebih kuat akan meningkatkan fleksibilitas menampilkan gambar.

Kesimpulan

Kami dapat menggunakan pengetahuan dan pemahaman kami tentang konsep-konsep penting dalam sistem tertanam sebagai state-machine, paralelisme komputasi, dan interfacing perangkat keras-perangkat lunak untuk menciptakan aplikasi deteksi tepi yang efisien yang memenuhi tujuan kami.

Pengakuan

Proyek ini dibangun oleh tim yang terdiri dari dua siswa: Hussein Youness dan Hany Hamed pada tahun pertama sarjana Ilmu Komputer di Universitas Innopolis di Rusia.

Proyek ini merupakan bagian dari kursus Arsitektur Komputer Musim Gugur 2018 di Innopolis University .