Dalam komentar pada

artikel saya

tentang mengendalikan LED RGB menggunakan blok mikrokontroler UDB PSC, disarankan untuk memberi tahu secara singkat di awal artikel tentang apa itu UDB. Seperti yang telah saya catat dalam artikel ini, saya tidak dapat menulis tentang UDB secara singkat, tetapi Anda dapat mentransfer dokumentasi perusahaan ke dalamnya untuk membiasakan pembaca domestik dengan alat yang sangat kuat untuk mengimplementasikan fungsi firmware.

Tapi pertama-tama, mari kita lihat apa itu PSoC. PSoC adalah keluarga chipset Cypress untuk mengimplementasikan sistem on-chip. Keluarga yang berbeda memiliki inti prosesor yang berbeda (untuk PSoC 3 itu adalah MCS-51, untuk PSoC 4 itu adalah Cortex M0, untuk PSoC 5LP itu adalah Cortex M3, dan untuk PSoC 6 itu dua sekaligus: Cortex M0 + dan Cortex M4) dan satu set logika yang dapat diprogram. Apalagi, logika ini bukan murni digital, ada hal-hal analog di sana. Selain satu set ADC yang berbeda, ada juga switch analog. Anda bahkan dapat secara pemrograman menyambungkan kaki melalui sirkuit analog, namun, resistansi sirkuit akan diukur dalam kilogram. Ada amplifier operasional di dalam PSoC yang dapat diprogram secara programatis, yang berarti Anda dapat membuat blok analog yang berbeda.

Omong-omong, PSoC dapat ditenagai oleh tegangan mulai dari 2,7 hingga 5,5 volt. Artinya, Anda tidak perlu memikirkan segala jenis stabilisator baik dengan daya baterai atau dengan daya USB.

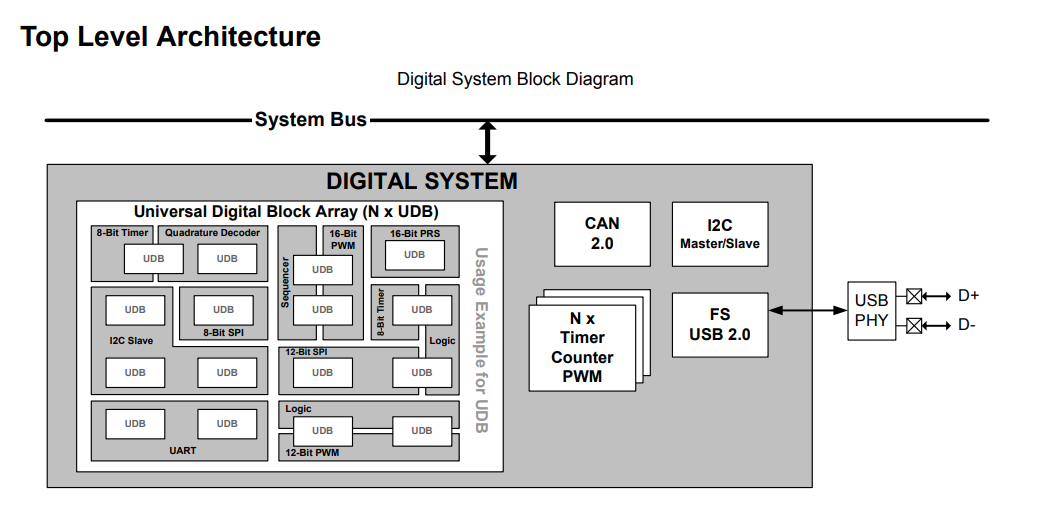

Tetapi saya menulis tentang hal-hal analog murni untuk kata merah. Sekarang kita akan fokus pada hal-hal digital. Sebagian besar pengontrol modern memiliki unit periferal yang kuat yang menyediakan beragam fungsi. Namun dalam praktiknya, dalam setiap pengembangan perangkat lunak tertentu, blok ini tidak sepenuhnya digunakan, tetapi hanya sebagian. Dan di PSoC, alih-alih sekelompok yang baik, logika program diimplementasikan, mirip dengan logika FPGA klasik. Dengan demikian, dimungkinkan untuk mengimplementasikan blok-blok yang dibutuhkan di dalamnya, dengan memasukkannya dalam mode-mode yang diperlukan. Dan sumber daya tidak boleh dihabiskan untuk mode yang tidak digunakan, memberikannya untuk implementasi beberapa jenis barang sendiri.

Dan di sini beberapa kesalahpahaman sering muncul. Banyak pengembang terbiasa dengan kenyataan bahwa ada dua jenis Programmable Logic Integrated Circuits (FPGAs): CPLD dan FPGA. Oleh karena itu, banyak yang telah mendengar tentang PSoC, percaya bahwa ada semacam kotak-CPLD yang dapat diprogram di Veriolg. Bahkan ya dan tidak. Sejumlah PLD tertentu (tanpa "C", hanya PLD) benar-benar ada, dan Anda benar-benar dapat memprogramnya di Verilog. Tapi sungguh, PLD ini adalah bagian dari blok UDB. Dan UDB yang merupakan elemen utama dari logika yang dapat diprogram yang diimplementasikan dalam PSoC. Blok ini sangat orisinal dan hanya menyediakan peluang terluas bagi pengembang. Pertimbangkan gambar dari dokumentasi hak milik yang menjelaskan esensi dari penggunaan blok UDB.

Karena saya mempelajari semuanya menggunakan keluarga PSoC 5LP sebagai contoh, saya akan menerjemahkan dokumentasinya. Tetapi sebelum Anda mulai, saya akan mengatakan beberapa kata tentang harga pengontrol ini. Jika Anda pergi ke Ali Express dan melihat papan tempat memotong roti untuk mereka, Anda mendapatkan perasaan sedih. Terus terang, dibandingkan dengan STM32-DISCOVERY mereka masih belum apa-apa, tetapi dibandingkan dengan prototipe STM32F103C8T6, mereka agak mahal. Pertama-tama, ini disebabkan oleh fakta bahwa mock-up perusahaan tidak hanya memiliki satu, tetapi dua pengendali seperti itu. Fungsi JTAG diimplementasikan pada PSoC 5LP, bahkan jika pengontrol target dan PSoC 4 (yang terakhir biasanya tidak memiliki port USB).

Tetapi membagi harga dengan dua, kita masih mendapatkan bahwa itu lebih tinggi dari STM32F103, yang serupa dalam inti prosesor. Namun demikian, jika kita menambahkan CPLD paling sederhana ke STM32 yang sama dari luar, maka total harga akan keluar untuk PSoC. Dan kami akan menambahkan kaki yang hilang ke koneksi kedua kasing ini (PSoC memiliki semua koneksi di dalamnya). Dan juga harga papan sentimeter persegi. Jadi ternyata jika Anda hanya perlu bekerja dengan inti prosesor, PSoC benar-benar tidak perlu. Jika Anda perlu membawa beberapa fungsionalitas ke tingkat firmware atau perangkat keras, maka Anda memerlukan PSoC. Di atasnya, sistem akan keluar lebih murah dan lebih mudah.

Sebenarnya, saya punya ide manik untuk mencoba membuat dukungan perangkat keras untuk kernel RTOS MAX kami. Untuk melakukan ini, saya mempelajari metodologi untuk mengembangkan aplikasi Bare Metal untuk Altera V SoC (sayangnya, ternyata fitur arsitektur di sana sedemikian rupa sehingga OS dapat diperlambat, tetapi Anda tidak dapat mempercepatnya - satu permintaan ke perangkat keras datang dengan latensi gila). Untuk ini, saya mulai menguasai PSoC. Saya belum mencapai kernel overclocking (hanya ada pemikiran umum), tetapi saya sangat menyukai gagasan pemrograman UDB. Tentu saja, saya sekarang tertarik untuk membawa ide ini ke jumlah maksimum programmer dalam negeri. Oleh karena itu, kami melanjutkan ke terjemahan bagian yang sesuai dari dokumentasi hak milik Cypress di UDB. Penomoran bab dan gambar dipertahankan sesuai dengan dokumen asli.

Isi umum dari siklus “UDB. Apa ini? "

Bagian 1. Pendahuluan. Pld. (Artikel saat ini)

Bagian 2. Datapath.Bagian 3. Datapath FIFO.Bagian 4. Datapath ALU.Bagian 5. Datapath. Hal-hal kecil yang bermanfaat.Bagian 6. Modul manajemen dan status.Bagian 7. Pengaturan waktu dan reset modul kontrolBagian 8. Mengatasi UDBUDB. Apa ini Bagian 1

21. Blok digital universal

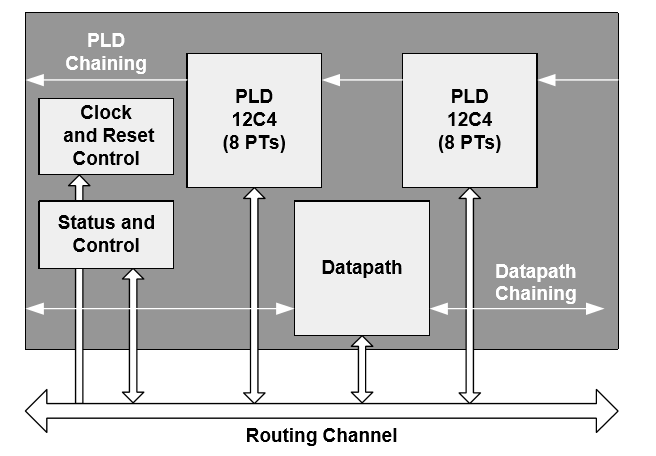

Dalam bab ini, kita akan melihat bagaimana Universal Digital Blocks (UDBs) memungkinkan pengembangan fungsi perangkat digital yang dapat diprogram. Arsitektur UDB memberikan keseimbangan antara rincian konfigurasi dan implementasi yang efisien. UDB terdiri dari kombinasi logika non-komutasi mirip dengan matriks logika yang dapat diprogram (PLM, PLD Inggris), logika terstruktur (mesin operasional, selanjutnya disebut sebagai Datapath) dan skema pelacakan yang fleksibel.

21.1 Fitur

- Untuk fleksibilitas optimal, setiap UDB berisi komponen-komponen berikut:

• Datapath 8-bit berdasarkan ALU (Unit Aritmatika dan Logika, ALU) dengan repositori instruksi 8-kata, beberapa register dan buffer FIFO;

• dua PLD, yang masing-masing memiliki 12 input, delapan syarat penghubung (Ketentuan Produk, PT) dan empat keluaran macrocell;

• register manajemen dan status;

• modul jam dan reset. - PSoC 5LP berisi larik hingga 24 UDB.

- Pelacakan fleksibel antara elemen array UDB.

- Elemen UDB dapat dipisah atau dirantai untuk membuat fungsi yang lebih besar.

- Implementasi yang fleksibel dari sejumlah fungsi digital, termasuk timer, penghitung, modulator lebar pulsa (termasuk PWM dengan generator deadband), UART, bus I2C, bus SPI, dan verifikasi / pembangkitan CRC.

21.2 Diagram Blok

Gambar 21-1 menunjukkan UDB sebagai konstruksi yang mengandung dua blok logis dasar, PLD, Datapath, dan fungsi kontrol, status, jam, dan reset.

Gambar 21-1. Diagram blok UDB.

Gambar 21-1. Diagram blok UDB.21.3 Cara kerjanya

Komponen utama UDB adalah:

- PLD (2). Data dari sumber daya jejak dimasukkan ke input dari blok ini. Mereka menerapkan logika kombinasional dan gertakan data, yang memungkinkan Anda untuk mengimplementasikan mesin negara hingga, mengontrol operasi blok Datapath, mengonfigurasi kondisi input dan mengontrol output.

- Datapath. Blok ini berisi ALU yang dapat diprogram secara dinamis, empat register, dua buffer FIFO, pembanding, dan pembuatan kondisi.

- Manajemen dan status (Status dan Kontrol). Modul-modul ini menyediakan mekanisme untuk interaksi mikroprogram dari prosesor pusat (CPU) dan sinkronisasi dengan operasi UDB. Register kontrol bekerja pada elemen internal, dan register status membaca keadaan elemen eksternal.

- Kontrol Jam dan Atur Ulang Modul-modul ini menyediakan pemilihan waktu dan mengaktifkan, serta mengatur ulang pemilihan dalam UDB.

- Sinyal Rantai. PLD dan Datapath memiliki sinyal yang memungkinkan Anda untuk rantai blok yang berdekatan dalam rantai untuk membuat fungsi bit yang lebih tinggi.

- Tracing Channel UDB terhubung ke saluran jejak melalui matriks switching yang dapat diprogram untuk komunikasi antara blok dalam UDB yang sama dan untuk komunikasi dengan UDB lain dalam array.

- Antarmuka Bus Sistem (Antarmuka Bus Sysytem). Semua register dan RAM di setiap UDB diproyeksikan ke ruang alamat sistem, dan akses ke sana dapat diperoleh dengan menggunakan prosesor pusat atau melalui akses memori langsung (Akses Memori Langsung Inggris, DMA) dalam bentuk 8-bit dan 16-bit data.

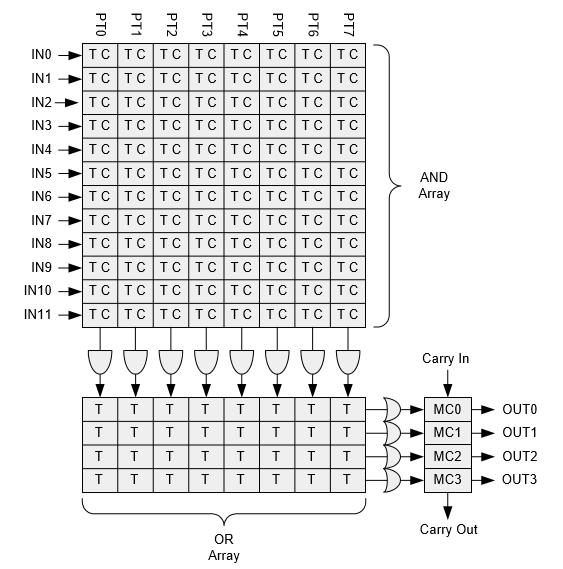

21.3.1. Pld

Setiap UDB memiliki dua PLD 12C4. Blok PLD yang ditunjukkan pada Gambar 21-1 dapat digunakan untuk mengimplementasikan mesin negara, memproses data I / O, dan membuat logika tabel (Eng. Lookup Table, LUT). Selain itu, PLD dapat dikonfigurasi untuk melakukan fungsi aritmatika, mengatur urutan Datapath, dan menghasilkan status. Logika umum dapat disintesis dan diproyeksikan ke blok PLD. Bagian ini memberikan gambaran umum arsitektur PLD.

PLD memiliki 12 input yang mengirimkan informasi ke 8 istilah penghubung dalam sebuah array AND. Dalam setiap istilah konjungtif, Anda dapat memilih input langsung (benar, T) atau terbalik (komplemen, C). Output dari kata penghubung pergi ke input dari array ATAU. Huruf 'C' dalam 12C4 menunjukkan bahwa ketentuan OR konstan untuk semua input, dan setiap input OR dapat mendapatkan akses terprogram ke istilah konjungtif apa pun. Struktur ini memberikan fleksibilitas maksimum dan memastikan bahwa semua input dan output dapat dipindahkan.

Gambar 21-2. Struktur PLD 12C4.

Gambar 21-2. Struktur PLD 12C4.21.3.1.1 PLD Makro

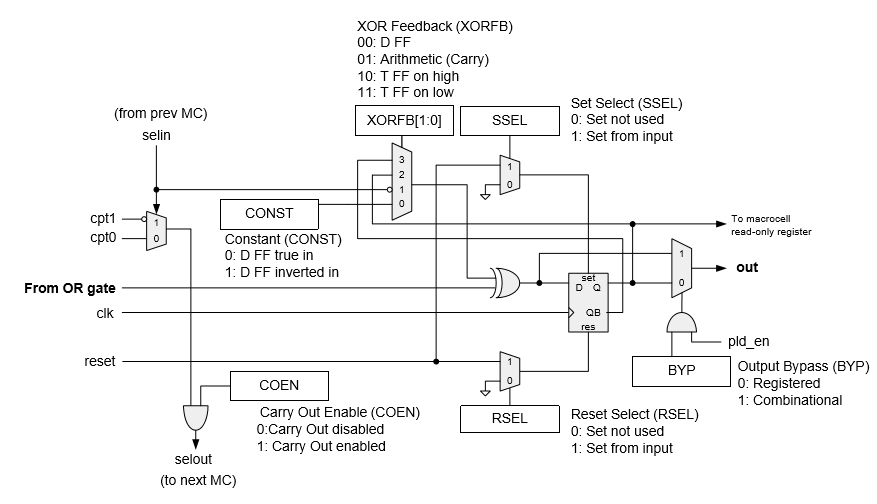

Arsitektur macrocell ditunjukkan pada Gambar 21-3. Output mengontrol array jejak dan dapat di-latch atau Raman. Untuk penguncian, pemicu D dengan input langsung atau terbalik atau pemicu T dengan level input tinggi atau rendah digunakan. Pemicu output dapat diatur atau diatur ulang selama inisialisasi atau secara tidak sinkron selama operasi normal, oleh sinyal eksternal dari saluran jejak.

Gambar 21-3. Arsitektur Macrocell.PLD Macro Cell Register Read-Only

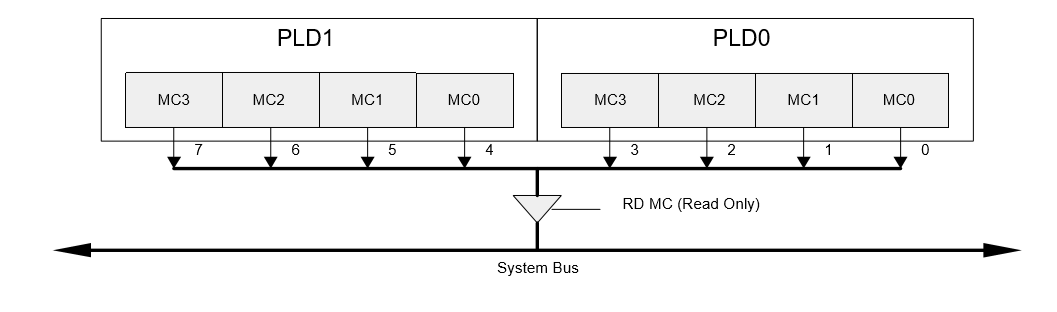

Gambar 21-3. Arsitektur Macrocell.PLD Macro Cell Register Read-OnlySelain mengendalikan larik jejak, output macrocell dari kedua PLD diproyeksikan ke ruang alamat dalam bentuk register read-only 8-bit, yang dapat diakses menggunakan CPU atau DMA.

Gambar 21-4. Register macrocell PLD hanya baca.

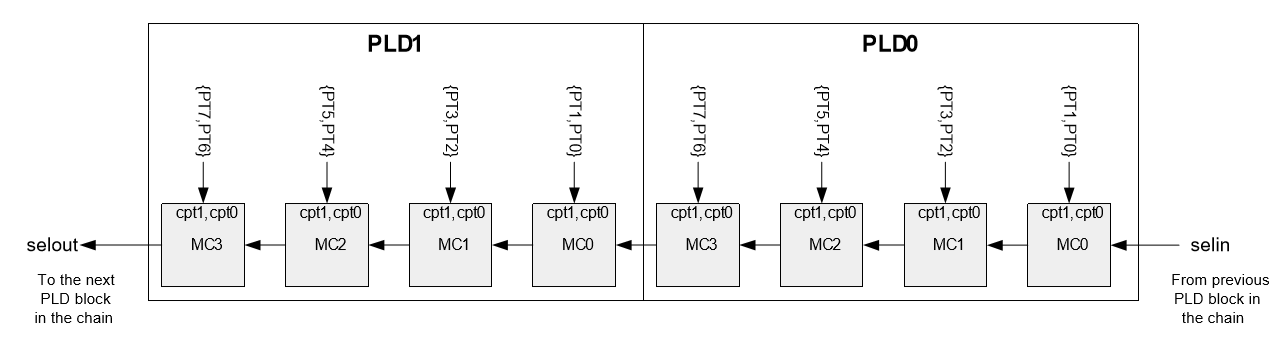

Gambar 21-4. Register macrocell PLD hanya baca.21.3.1.2 rantai hyphenation PLD

PLD diikat bersama dalam menangani UDB. Seperti yang ditunjukkan pada Gambar 21-5, input rantai selin diteruskan dari UDB sebelumnya ke sirkuit, melalui masing-masing sel makro di kedua PLD, kemudian diteruskan ke UDB berikutnya sebagai output dari rantai selout. Untuk mendukung penempatan fungsi aritmatika yang efisien, dihasilkan istilah konjungtif khusus (PT), yang digunakan dalam sel-sel makro bersama-sama dengan rantai tanda hubung.

Gambar 21-5. Rantai hyphenation PLD dan input term konjungtif khusus.

Gambar 21-5. Rantai hyphenation PLD dan input term konjungtif khusus.21.3.1.3 Konfigurasi PLD

Setiap PLD muncul di depan CPU atau DMA dalam bentuk RAM dengan akses 16-bit. AND array memiliki 12 × 8 × 2 bit atau 24 byte untuk pemrograman, dan array OR memiliki 4 × 8 bit atau 4 byte untuk pemrograman. Selain itu, setiap sel makro memiliki satu byte konfigurasi, dengan total 32 byte konfigurasi per PLD. Karena setiap UDB memiliki 2 PLD, konfigurasi total masing-masing UDB adalah 64 byte.

Lain kali kita akan mempertimbangkan Automational Automata (Datapaths).