Kami terus mempertimbangkan UDB berdasarkan dokumentasi Cypress. Dan kali ini kita akan mempelajari secara rinci Datapath, sebuah otomat operasional.

Isi umum dari siklus “UDB. Apa ini? "

Bagian 1. Pendahuluan. Pld.Bagian 2. Datapath. (Artikel saat ini)

Bagian 3. Datapath FIFO.Bagian 4. Datapath ALU.Bagian 5. Datapath. Hal-hal kecil yang bermanfaat.Bagian 6. Modul manajemen dan status.Bagian 7. Pengaturan waktu dan reset modul kontrolBagian 8. Mengatasi UDB21.3.2 Mesin operasional (Datapath)

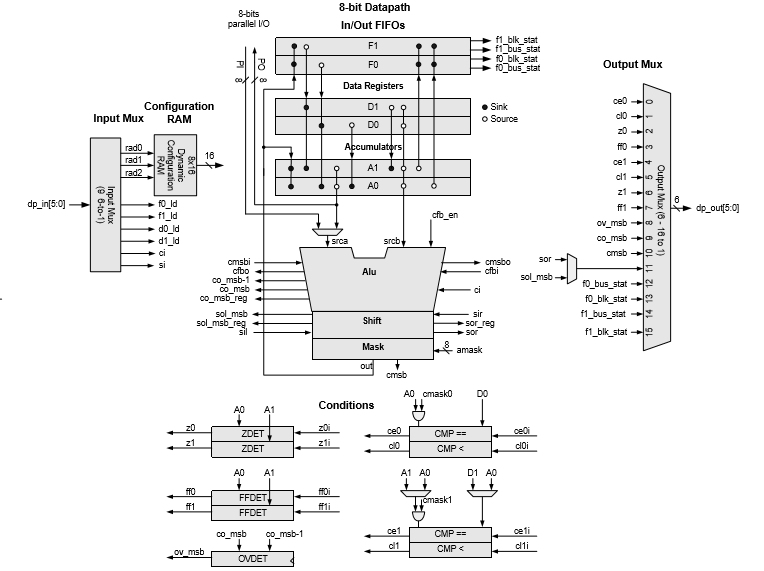

Datapath yang ditunjukkan pada Gambar 21-6 berisi 8-bit, ALU tunggal dan sirkuit terkait untuk membandingkan dan menghasilkan flag kondisi. Blok datapath dari UDB yang berdekatan dapat dirantai bersama untuk meningkatkan kedalaman bit. Datapath termasuk konfigurasi RAM kecil dinamis yang dapat secara dinamis memilih operasi yang akan dilakukan dalam siklus tertentu.

Datapath dioptimalkan untuk mengimplementasikan fungsi-fungsi tertanam yang khas seperti penghitung waktu, penghitung, PWM, PRS, CRC, register geser, dan generator deadband. Menambahkan fungsi penjumlahan dan pengurangan menyediakan dukungan untuk operasi delta-sigma digital.

Gambar 21-6. Datapath tingkat atas.

21.3.2.1 Ikhtisar

Bab-bab berikut memberikan tinjauan umum tentang fitur-fitur utama Datapath.

Konfigurasi dinamisKonfigurasi dinamis - kemampuan untuk mengubah pekerjaan dan komunikasi internal Datapath di setiap siklus di bawah kendali sequencer. Ini diimplementasikan menggunakan memori konfigurasi (RAM konfigurasi), yang menyimpan delapan konfigurasi unik. Alamat input dari memori ini dapat diteruskan dari blok yang terhubung ke sumber daya jejak, biasanya dari logika PLD, pin I / O, atau dari Datapath lain.

AluALU dapat melakukan delapan fungsi tujuan umum: increment, decrement, add, kurangi, dan juga melakukan operasi logis AND, OR, XOR dan PASS. Pilihan fungsi ditentukan oleh memori konfigurasi untuk setiap siklus. Operasi shift independen (kiri, kanan, permutasi nibble), serta operasi masking tersedia pada output ALU.

Konstruksi BersyaratSetiap Datapath memiliki dua pembanding bertopeng bitwise yang dapat dikonfigurasi untuk memilih beberapa input register Datapath sebagai argumen. Kondisi yang dapat diidentifikasi lainnya mungkin semua nol, semua, dan melimpah. Kondisi ini membentuk output utama Datapath dan dapat diteruskan ke jalur jejak digital atau input fungsi lainnya.

CRC / PRS TertanamDatapath memiliki dukungan bawaan untuk perhitungan CRC siklus tunggal dan generasi sekuen pseudo-acak (Eng. Pseudo Random Sequence, PRS) dengan kedalaman bit yang diberikan dan polinomial penghasil. Untuk mencapai kedalaman bit lebih dari 8 bit, sinyal dapat dirantai antara Datapath. Fitur ini dikendalikan secara dinamis, yang artinya dapat bergantian dengan fungsi lain.

Nomor Bit Tinggi KustomJumlah bit yang paling signifikan (English Most Significant Bit, MSB) dari fungsi aritmatika dan fungsi shift dapat diatur secara terprogram. Ini memberikan dukungan untuk fungsi CRC / PRS panjang variabel, dan, bersama dengan masking output ALU, memungkinkan implementasi timer dengan panjang sewenang-wenang, penghitung, dan blok geser.

Input / Output Buffer FIFOSetiap Datapath memiliki dua buffer FIFO 4-byte, yang masing-masing dapat dikonfigurasi untuk berfungsi sebagai buffer input (CPU atau DMA menulis data ke FIFO, Datapath membaca FIFO), atau sebagai buffer output (Datapath menulis ke FIFO, dan CPU atau DMA membaca dari itu). Buffer FIFO ini menghasilkan status yang dapat diteruskan untuk berinteraksi dengan urutan, interupsi, atau permintaan DMA.

RantaiDatapath dapat dikonfigurasi untuk kondisi rantai dan sinyal dalam suatu rantai ke Datapath yang berdekatan. Shift, transfer, capture, dan sinyal kondisional lainnya dapat digabungkan dalam rantai untuk menciptakan fungsi aritmatika dengan kedalaman bit yang lebih tinggi, serta fungsi shift dan fungsi CRC / PRS.

Multiplexing waktuDalam aplikasi oversampling atau di mana kecepatan clock tinggi tidak diperlukan, satu ALU di Datapath dapat secara efektif dibagi antara dua set register dan generator kondisi. Output dari ALU dan register geser terkunci dan dapat digunakan sebagai input dalam siklus berikutnya. Contoh penggunaan termasuk dukungan untuk fungsi 16-bit dalam satu (8-bit) Datapath, atau operasi generasi CRC bergantian dengan operasi pergeseran data.

Input DatapathDatapath memiliki empat jenis input: konfigurasi, kontrol, serta input data (serial dan paralel). Input konfigurasi memilih alamat RAM dari konfigurasi dinamis. Input kontrol memuat register data dari FIFO dan mengunduh output baterai ke FIFO. Input data serial mencakup shift dan carry input. Port input data paralel memungkinkan Anda menerima hingga 8 bit data dari sumber jejak.

Output DatapathTotal ada 16 sinyal yang dihasilkan dalam Datapath. Beberapa dari mereka adalah sinyal kondisional (misalnya, perbandingan), yang lain adalah sinyal status (misalnya, status FIFO), dan sisanya adalah sinyal data (misalnya, output register geser). 16 sinyal ini di-multiplexing menjadi 6 output Datapath dan dialihkan ke trace matrix. Secara default, output disinkronkan dengan frekuensi clock, yang menciptakan perpipaan dengan penundaan 1 siklus clock. Juga, (keluaran) mereka dapat dialihkan ke mode asinkron (kombinatorial) (lihat catatan penerjemah).

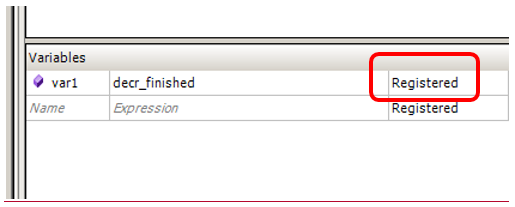

Catatan PenerjemahSaya mencari untuk waktu yang lama tentang apa waktu dari output Datapath. Pengalaman saya mengatakan bahwa semuanya ada di sana secara serempak. Ternyata ini bukan keadaan keluaran, tapi pengaturan editor ini berdasarkan variabel. Ini akan memaksa editor untuk menghasilkan kode Verilog berikut:

Ini akan memaksa editor untuk menghasilkan kode Verilog berikut:/* ==================== Assignment of Registered Variables ==================== */ always @ (posedge clock) begin : register_assignments var1 <= (decr_finished); end

Jika Anda beralih ke mode kombinatorial kode akan menjadi seperti ini:

kode akan menjadi seperti ini: assign var1 = (decr_finished);

Tetapi semua ini berlaku untuk variabel yang dihasilkan dari output Datapath. Dan outputnya sendiri selalu asinkron. Dan namanya (dalam contoh ini decr_finished ) dapat digunakan tanpa memasukkan variabel tambahan.Register Kerja DatapathSetiap modul Datapath memiliki enam register kerja 8-bit. CPU atau DMA memiliki akses baca dan tulis ke semua register.

Tabel 21-1Pada artikel selanjutnya, kita akan mulai berurusan dengan FIFO.