Kami terus menerjemahkan dokumentasi milik Cypress ke blok UDB. Apalagi semuanya bertepatan dengan sangat baik. Untuk melanjutkan

artikel praktis tentang UDB, Anda harus menggunakan FIFO, dan pada bagian teoretis kita sampai pada deskripsi mereka. Karena itu, kami mulai mempelajarinya secara rinci.

Isi umum dari siklus “UDB. Apa ini? "

Bagian 1. Pendahuluan. Pld.Bagian 2. Datapath.Bagian 3. Datapath FIFO. (Artikel saat ini)

Bagian 4. Datapath ALU.Bagian 5. Datapath. Hal-hal kecil yang bermanfaat.Bagian 6. Modul manajemen dan status.Bagian 7. Pengaturan waktu dan reset modul kontrolBagian 8. Mengatasi UDB21.3.2.2 Datapath FIFO

Mode dan Konfigurasi FIFO

Setiap buffer FIFO memiliki beberapa mode operasi dan konfigurasi yang tersedia:

Tabel 21-2. Mode dan konfigurasi FIFO.

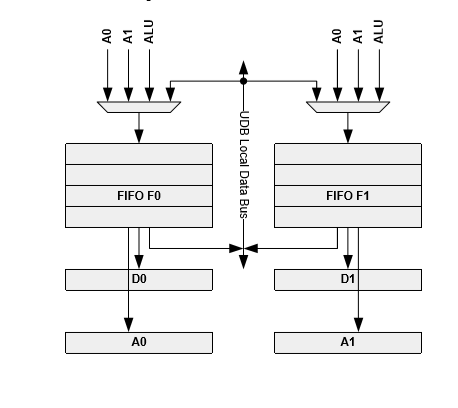

Gambar 21-7 menunjukkan opsi konfigurasi yang memungkinkan untuk pasangan FIFO, tergantung pada mode Input / Output yang dipilih untuk masing-masing FIFO. Jika satu FIFO dalam mode input dan yang lainnya dalam mode output, kami mendapatkan konfigurasi RX / TX. Contoh khas di mana konfigurasi seperti itu diperlukan adalah pengendali bus SPI. Konfigurasi

Dual Capture (kedua FIFO dikonfigurasikan untuk output) memberikan tangkapan independen dari pasangan A0 dan A1 atau dua penangkapan independen dari register A0 atau A1. Akhirnya, dalam mode

Penyangga Ganda (keduanya pada input), dimungkinkan untuk menggunakan pasangan register atau dua register independen untuk memuat atau membandingkan.

Gambar 21-7. Konfigurasi FIFO.

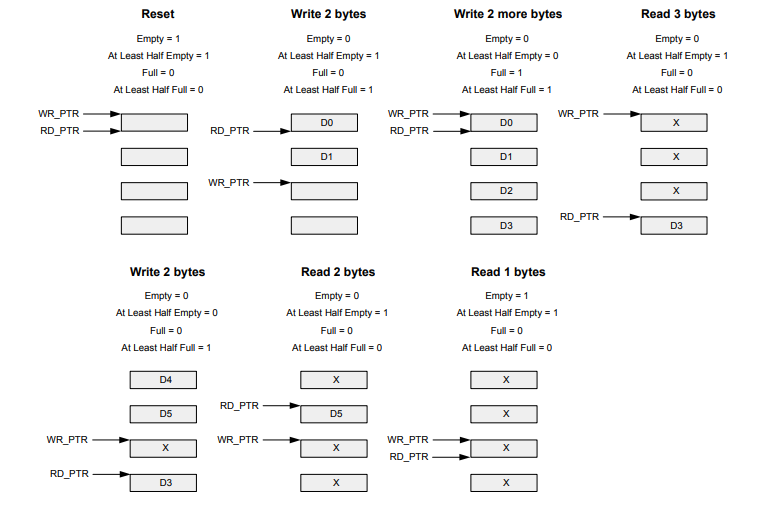

Gambar 21-8 menunjukkan secara detail sumber dan penerima FIFO.

Gambar 21-8. Sumber dan penerima FIFO.

Ketika FIFO beroperasi dalam mode buffer input, sumbernya adalah bus sistem, dan penerima adalah register Dx dan Ax. Saat bekerja dalam mode buffer output, sumbernya adalah register Ax dan ALU, dan penerima adalah bus sistem. Pilihan multiplexer diatur secara statis di register konfigurasi UDB CFG15, seperti yang ditunjukkan pada tabel untuk F0_INSEL [1: 0] atau F1_INSEL [1: 0]:

Tabel 21-3. Satu set multiplexer FIFO dalam register konfigurasi UDB.

Status FIFO

Setiap FIFO menghasilkan dua sinyal status, "bus" dan "blok," yang ditransmisikan ke sumber daya jejak UDB melalui multiplexer output Datapath. Status bus dapat digunakan untuk mengganggu atau meminta DMA baca / tulis ke FIFO. Negara "blok" terutama dimaksudkan untuk melewati negara FIFO ke entitas UDB internal. tujuan bit status tergantung pada arah yang dikonfigurasi (Fx_INSEL [1: 0]), dan bit level FIFO. Bit level FIFO (Fx_LVL) diatur dalam register Kontrol Bantu di ruang register yang berfungsi. Opsi status ditunjukkan pada tabel berikut:

Tabel 21-4. Opsi status FIFO.

Ilustrasi Pekerjaan FIFO

Gambar 21-9 menunjukkan urutan khas membaca dan menulis, serta generasi status yang terkait dengan operasi ini. Dalam gambar, membaca dan menulis terjadi pada waktu yang berbeda, tetapi mereka dapat dilakukan secara bersamaan.

Gambar 21-9 Operasi Penerima FIFO.

Mode Cepat FIFO (FIFO CEPAT)

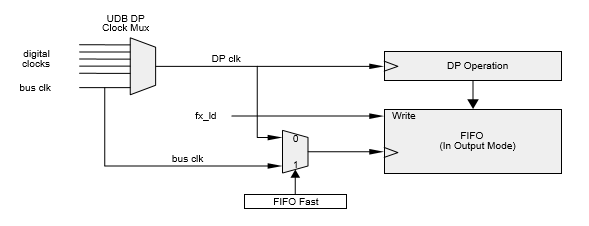

Ketika FIFO dalam mode buffer output, operasi boot FIFO biasanya menggunakan frekuensi clock dari Datapath yang dipilih untuk mencatat sinyal tulis. Seperti ditunjukkan pada Gambar 21-10, ketika memilih Mode Cepat FIFO (FIFO FAST), Anda dapat memilih frekuensi bus untuk operasi khusus ini. Ketika digunakan bersama dengan mode

Level / Edge = Edge , operasi ini mengurangi penundaan transmisi dari baterai ke FIFO dari periode jam Datapath ke periode jam bus, karena frekuensi bus bisa jauh lebih tinggi. Ini memungkinkan CPU atau DMA untuk membaca hasil FIFO yang diterima dengan penundaan minimal.

Seperti yang ditunjukkan pada Gambar 21-10, operasi boot cepat dilakukan terlepas dari jam Datapath saat ini, namun, menggunakan kecepatan jam bus dapat meningkatkan konsumsi daya.

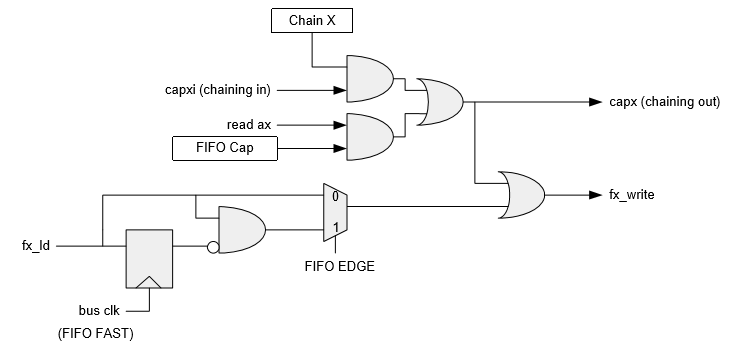

Gambar 21-10. Penerima konfigurasi cepat FIFO.

Mode Perekaman Tepi / Tingkat FIFO (Diferensial / Tingkat)

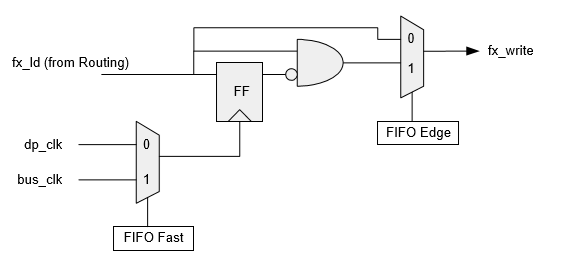

Ada dua mode perekaman di FIFO dari Datapath. Dalam mode pertama, data ditransfer secara sinkron dari baterai ke FIFO. Sinyal kontrol dari catatan ini (FX_LD) biasanya dihasilkan oleh mesin negara atau oleh kondisi yang disinkronkan dengan pencatatan jam kerja Datapath. Menulis ke FIFO akan dilakukan dalam setiap siklus di mana sinyal kontrol beban input adalah '1'. Dalam mode kedua, FIFO digunakan untuk menangkap nilai baterai sebagai respons terhadap tepi positif sinyal FX_LD. Dalam mode ini, format sinyal dari sinyal arbitrer (namun, periode harus sama dengan setidaknya satu siklus clock Datapath). Contoh dari mode ini adalah menangkap nilai baterai menggunakan input dari kaki eksternal sebagai pemicu. Batasan mode ini adalah bahwa parameter input harus kembali ke nilai '0' setidaknya satu siklus sebelum perbedaan positif lain terdeteksi.

Gambar 21-11 menunjukkan implementasi mode deteksi diferensial pada input FX_LD. Mode kedua FIFO di UDB dikendalikan oleh bit yang sama, mengubah opsi ini. Perhatikan bahwa deteksi diferensial clock pada frekuensi yang sama dengan frekuensi FIFO yang dipilih.

Gambar 21-11. Deteksi diferensial untuk penerima rekaman FIFO internal.

Mode Pengambilan Perangkat Lunak FIFO

Persyaratan umum dan penting adalah untuk memungkinkan CPU dan DMA untuk membaca isi baterai dengan andal selama operasi normal. Ini dilakukan menggunakan penangkapan perangkat lunak dan diaktifkan menggunakan bit konfigurasi Cap FIFO. Bit ini berlaku untuk kedua FIFO di UDB, tetapi hanya berfungsi ketika FIFO dalam mode buffer output. Saat menggunakan penangkapan perangkat lunak, F0 harus membaca dari A0, dan F1 dari A1.

Seperti yang ditunjukkan pada Gambar 21-12, membaca baterai memulai penulisan ke FIFO dari baterai. Sinyal dihubungkan dalam suatu rantai sehingga membaca byte tertentu secara bersamaan menangkap nilai baterai semua UDB dalam rantai. Ini memungkinkan prosesor 8-bit untuk berhasil membaca 16 bit atau lebih secara bersamaan. Data yang dikembalikan saat membaca baterai harus diabaikan, dan nilai yang ditangkap dapat segera dibaca dari FIFO.

Sinyal FX_LD yang dilacak, yang menghasilkan beban FIFO, dikirim ke istilah OR bersama dengan sinyal tangkapan program. Ketika penangkapan perangkat keras dan perangkat lunak digunakan pada saat yang sama, hasilnya bisa tidak dapat diprediksi. Sebagai aturan, fungsi-fungsi ini harus saling eksklusif, namun, penangkapan perangkat keras dan perangkat lunak dapat digunakan secara bersamaan dalam kondisi berikut:

- Mode jam pengambilan FIFO diatur ke FIFO FAST.

- Mode perekaman FIFO diatur ke FIFO EDGE.

Di bawah kondisi yang dijelaskan di atas, penangkapan perangkat keras dan lunak pada dasarnya bekerja sama, dan selama siklus jam bus apa pun, sinyal-sinyal ini dapat memicu tangkapan.

Anda juga disarankan untuk menghapus target FIFO dalam kode program (register ACTL) sebelum penangkapan program dimulai. Berkat ini, petunjuk baca dan tulis FIFO akan diatur ke kondisi yang diketahui.

Gambar 21-12. Konfigurasi Pengambilan Perangkat Lunak.

Catatan Penerjemah:

Untuk waktu yang lama saya tidak bisa mengerti arti bagian ini. Kemudian untuk waktu yang lama saya yakin bahwa bagian itu ditulis untuk PSoC3, inti delapan-bit yang tidak dapat mengakses lebih dari byte. Tetapi ketika membuat bagian kedelapan dari terjemahan , ternyata bahkan di PSoC5LP, untuk semua inti prosesor ARM 32-bit, akses ke register UDB yang berfungsi dapat dilakukan dalam mode delapan-bit atau enam belas-bit. Dilihat oleh dokumen, tidak ada lagi. Di sinilah fungsi yang dijelaskan berguna.

Bit Kontrol FIFO

Register Kontrol Bantu, yang dapat digunakan untuk mengontrol FIFO selama operasi normal, berisi 4 bit.

Bit FIFO0 CLR dan FIFO1 CLR digunakan untuk mengatur ulang atau menghapus FIFO. Ketika salah satu dari bit-bit ini diberikan nilai '1', FIFO yang terkait diatur ulang. Bit harus dikembalikan ke nilai aslinya ('0') agar FIFO dapat terus bekerja. Jika nilai bit tetap sama dengan satu, FIFO yang sesuai akan dinonaktifkan dan akan berfungsi sebagai buffer byte tunggal tanpa status. Data dapat ditulis ke FIFO, data dapat segera dibaca dan dapat ditimpa setiap saat. Arah data dengan bit konfigurasi FX INSEL [1: 0] masih dapat diatur.

FIFO0 LVL dan FIFO1 LVL bit menentukan tingkat di mana FIFO akan memiringkan bit status

"bus" (ketika bus membaca atau menulis ke FIFO). Artinya, status status

"bus" tergantung pada arah yang diberikan, seperti yang ditunjukkan pada tabel di bawah ini.

Tabel 21-5. Bit Kontrol Level FIFO

Operasi Asinkron FIFO

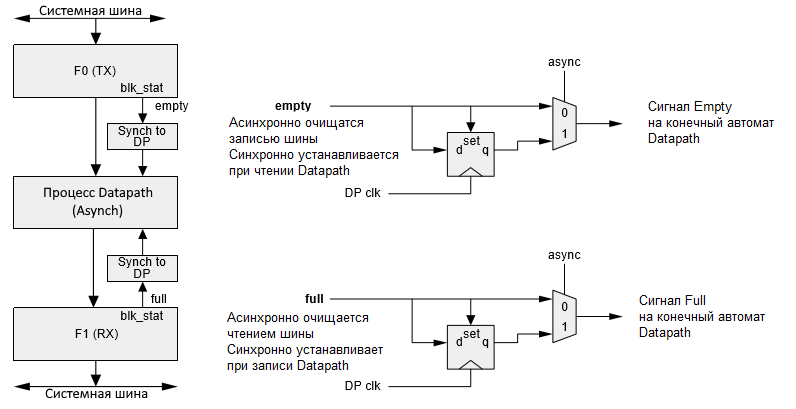

Gambar 21-13 menunjukkan prinsip operasi FIFO asinkron. Sebagai contoh, bayangkan F0 beroperasi dalam mode buffer input, dan F1 dalam mode buffer output, yang merupakan konfigurasi khas register TX dan RX.

Gambar 21-13. Operasi FIFO asinkron.

Di sisi TX, mesin negara Datapath menggunakan bendera

Kosong untuk menentukan apakah ada byte yang tersedia untuk menerima. Nilai

Kosong diatur secara sinkron dengan mesin status Datapath, dan dihapus secara asinkron karena penulisan dari bus. Setelah dibersihkan, statusnya kembali disinkronkan dengan mesin status Datapath.

Di sisi RX, mesin RX state menggunakan

Full untuk menentukan apakah ada ruang kosong untuk menulis ke FIFO. Nilai

penuh diatur secara sinkron dengan mesin status Datapath, dan dihapus secara asinkron karena membaca oleh bus. Setelah dibersihkan, statusnya kembali disinkronkan dengan mesin status Datapath.

Satu FIFO ASYNCH bit digunakan untuk mengaktifkan metode sinkronisasi ini, setelah aktivasi metode ini diterapkan untuk kedua FIFO.

Ini hanya berlaku untuk status

Blokir , karena diasumsikan bahwa status

Bus secara alami disinkronkan oleh proses interupsi.

Tabel 21-6.

Blokir opsi sinkronisasi status FIFO.

FIFO meluap selama operasi

Untuk implementasi operasi baca dan tulis internal (Datapath) dan eksternal (CPU atau DMA) yang aman, sinyal status FIFO harus digunakan. Tidak ada perlindungan bawaan terhadap kondisi pengosongan dan luapan. Jika FIFO penuh dan operasi penulisan berikutnya dilakukan (overflow), data baru menimpa awal FIFO (data yang saat ini sedang diproduksi adalah yang berikutnya dalam antrian baca). Jika FIFO kosong dan pembacaan berikutnya dilakukan (mengosongkan atau menipis), nilai baca tidak terdefinisi. Pointer FIFO tetap akurat terlepas dari underflow dan overflow.

FIFO Clock Inversion

Setiap FIFO memiliki bit kontrol Fx CK INV, yang bertanggung jawab untuk polaritas jam FIFO Mengenai polaritas jam Datapath. Secara default, FIFO bekerja dengan polaritas yang sama dengan pencatatan jam kerja Datapath. Ketika bit ini adalah 1, FIFO beroperasi dengan polaritas terbalik relatif terhadap Datapath. Ini memberikan dukungan protokol untuk bertukar data di kedua front, seperti SPI.

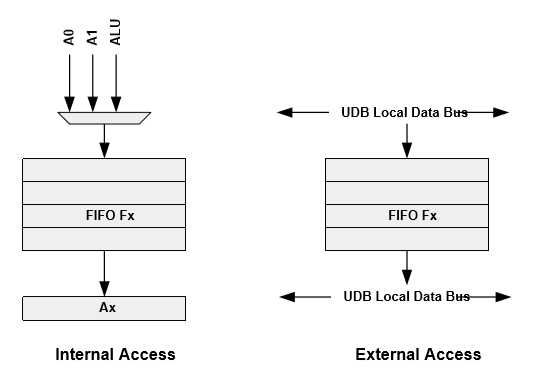

Kontrol FIFO dinamis

Biasanya, FIFO dikonfigurasi secara statis baik dalam mode buffer input atau dalam mode buffer output. Atau, setiap FIFO dapat dikonfigurasi untuk beroperasi dalam mode di mana arah dikendalikan secara dinamis (di bawah pengaruh sinyal eksternal). Satu bit konfigurasi per FIFO (Fx DYN) bertanggung jawab untuk mengaktifkan mode ini. Gambar 21-14 menunjukkan konfigurasi yang tersedia dalam mode dinamis FIFO.

Gambar 21-14. Mode FIFO dinamis.

Dalam mode Akses Internal, Datapath dapat membaca dan menulis ke FIFO. Dalam konfigurasi ini, untuk memilih sumber operasi tulis di FIFO, bit Fx INSEL harus diatur ke 1. Fx INSEL = 0 (sumber bus CPU) dalam mode ini tidak benar, hanya dapat mengambil nilai 1, 2 atau 3 (A0, A1 atau ALU ) Perlu dicatat bahwa membaca memiliki akses hanya ke baterai yang sesuai, arah register data dalam mode ini tidak tersedia.

Dalam mode Akses Eksternal, CPU atau DMA dapat membaca atau menulis ke FIFO.

Konfigurasi secara dinamis beralih antara akses eksternal dan internal dengan meneruskan sinyal dari Datapath. Untuk ini, sinyal input Datapath d0_load dan d1_load digunakan. Perlu dicatat bahwa dalam mode kontrol dinamis, d0_load dan d1_load tidak tersedia untuk penggunaan normal ketika memuat register D0 / D1 dari F0 / F1. Sinyal Dx_load dapat dipicu oleh sinyal jejak, termasuk konstanta.

Pertimbangkan contoh di mana, dimulai dengan akses eksternal (dx_load == 1), CPU atau DMA dapat menulis satu atau lebih byte data ke FIFO. Kemudian, ketika beralih ke akses internal (dx_load == 0), Datapath dapat melakukan operasi pada data. Setelah itu, ketika beralih ke akses eksternal, CPU atau DMA dapat membaca hasil perhitungan.

Karena Fx INSEL harus selalu 01, 10 atau 11 (A0, A1 atau ALU), yang sesuai dengan "mode buffer output" selama operasi normal, sinyal status FIFO memiliki definisi berikut (tergantung pada parameter Fx LVL):

Tabel 21-7. Status FIFO.

Karena Datapath dan CPU dapat menulis dan membaca dari FIFO, sinyal-sinyal ini tidak lagi dianggap sebagai status blok dan bus. Sinyal blk_stat digunakan untuk status tulis, dan sinyal bus_stat untuk status baca

21.3.2.3 Status FIFO

Ada empat sinyal status FIFO, dua untuk setiap FIFO: fifo0_bus_stat, fifo0_blk_stat, fifo1_bus_stat dan fifo1_blk_stat. Arti dari sinyal-sinyal ini tergantung pada arah FIFO tertentu, yang ditentukan oleh konfigurasi statis. Status FIFO dijelaskan secara rinci di bagian

21.3.2.2 Datapath FIFO .

Pada bagian selanjutnya, kita akan beralih ke analisis Unit Logika Aritmatika (ALU).