"CVAX - ketika kamu mendapatkan cukup mencuri yang terbaik."

"CVAX - ketika kamu mendapatkan cukup mencuri yang terbaik."Prasasti yang ditinggalkan oleh insinyur Amerika untuk rekan Soviet di topologi mikroprosesor.

Rekayasa terbalik microchip adalah sakit kepala bagi produsen dari tahun-tahun pertama keberadaan mikroelektronika. Semua elektronik Soviet pada satu titik dibangun di atasnya, dan sekarang mereka melakukan hal yang sama di Kerajaan Surgawi, dan tidak hanya di dalamnya, dalam skala yang jauh lebih besar. Faktanya, reverse engineering benar-benar legal di Amerika Serikat, Uni Eropa, dan banyak tempat lainnya, dengan tujuan (saya kutip hukum Amerika) tentang "mengajar, menganalisis, atau mengevaluasi konsep atau teknik yang diterapkan dalam kerja topeng atau sirkuit".

Penggunaan hukum yang paling umum untuk rekayasa balik adalah pengadilan paten dan berlisensi. Spionase industri juga umum, terutama karena sirkuit listrik (terutama yang analog) sering merupakan kekayaan intelektual utama dan jarang dipatenkan - hanya untuk menghindari pengungkapan IP dan partisipasi di pengadilan paten sebagai penuduh. Tentu saja, dalam situasi di mana Anda perlu melindungi kekayaan intelektual Anda tanpa mematenkannya, pengembang dan produsen berusaha mencari cara untuk mencegah penyalinan perkembangan mereka.

Bidang lain yang tidak kalah pentingnya (atau bahkan lebih) untuk melindungi microchip dari rekayasa balik adalah untuk memastikan keamanan informasi yang tersimpan dalam memori. Informasi tersebut dapat berupa firmware FPGA (yaitu, lagi-lagi, properti intelektual pengembang), dan, misalnya, kode PIN dari kartu bank atau kunci enkripsi untuk flash drive yang aman. Semakin berharga informasi yang kita percayai dunia di sekitar kita, semakin penting untuk melindungi informasi ini di semua tingkat sistem pemrosesan, dan tingkat perangkat keras tidak terkecuali.

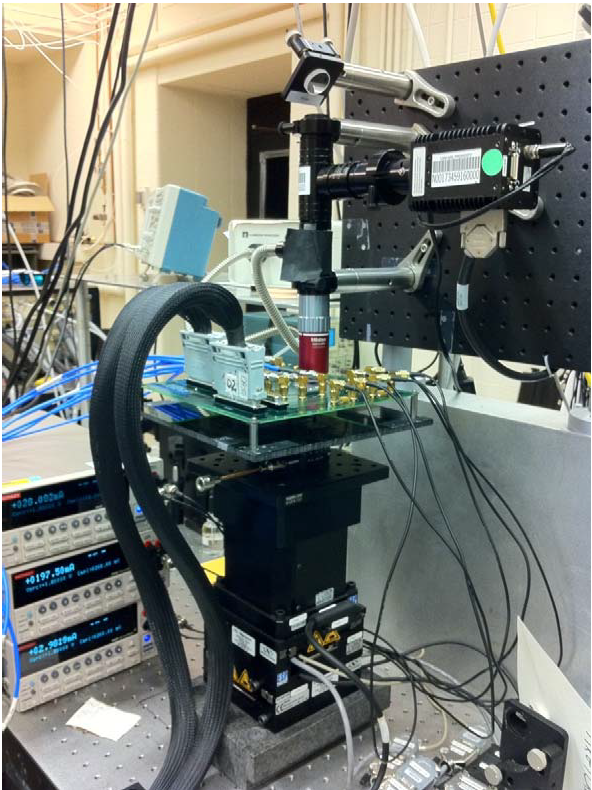

Hal pertama yang pertama: hal penting untuk dipahami. Berbicara tentang rekayasa balik dan perlindungan terhadap penyalinan data, harus dipahami bahwa metode perlindungan yang benar-benar stabil tidak ada, dan semua yang nyata adalah membuat prosesnya begitu lama dan / atau mahal sehingga menjadi tidak ekonomis secara ekonomi.Bertahun-tahun yang lalu, pekerjaan seorang insinyur balik atau bajak laut mikroelektronika jauh lebih mudah daripada sekarang. Lihat, misalnya, pada gambar ini (terima kasih kepada

BarsMonster untuk masa kecil kita yang bahagia dan foto-foto yang bagus): dengan pemahaman dasar tentang teknologi, memulihkan sirkuit listrik darinya adalah masalah beberapa jam.

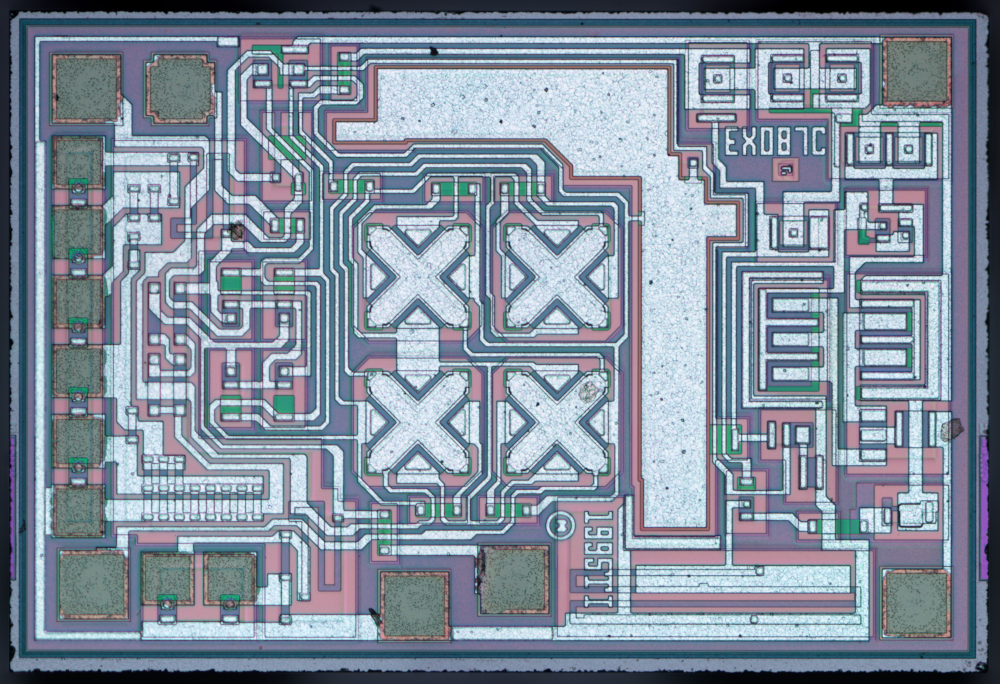

Gambar 2. Cuplikan dari topologi op-amp OPA134PA. Sumber - zeptobars.comDi sini , omong-omong, ada contoh rekayasa balik chip TL431 yang dibuat oleh Ken Shirriff dari foto BarsMonster. Dan inilah terjemahan bahasa Rusia. Blog Ken memiliki banyak hal keren jika Anda tertarik dengan topik reverse engineering amatir.Dan di sini (hati-hati, lalu lintas!) Adalah laporan dari rekayasa terbalik chip Zilog Z80-CTC, dibuat pada tahun 1979, hampir segera setelah rilis chip. Sekarang ini adalah dokumen historis yang unik, dan kemudian informasi yang bernilai komersial luar biasa dan diperoleh (dilihat dari beberapa referensi standar militer), mungkin dalam proses sertifikasi sirkuit mikro untuk aplikasi khusus.

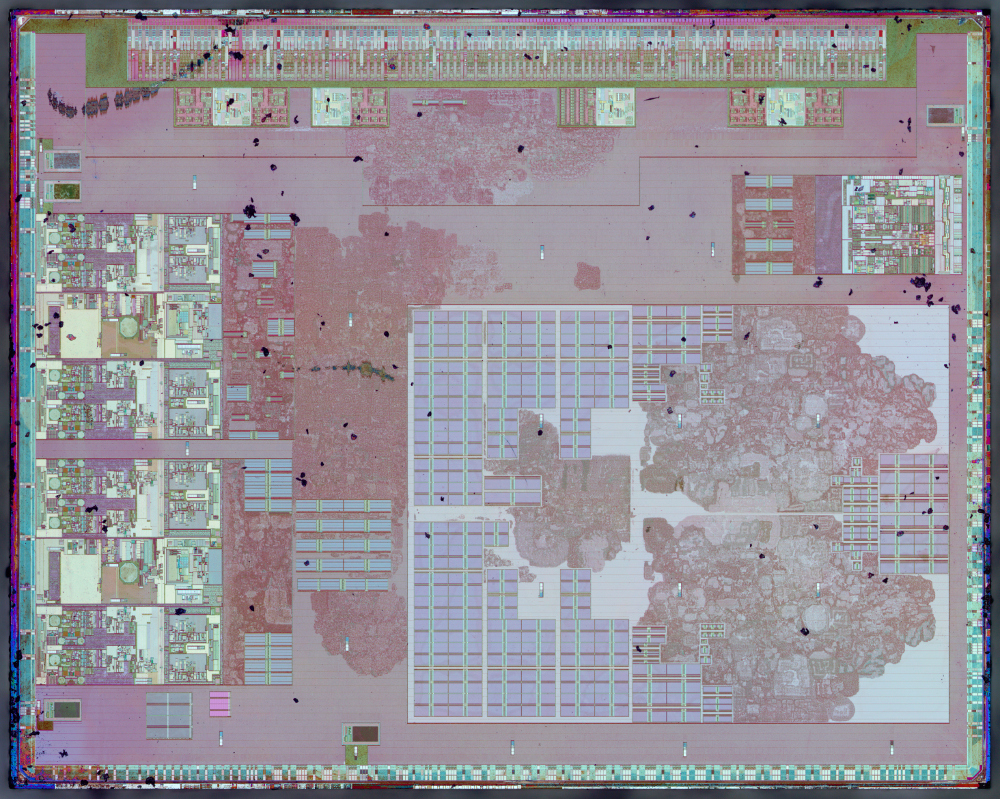

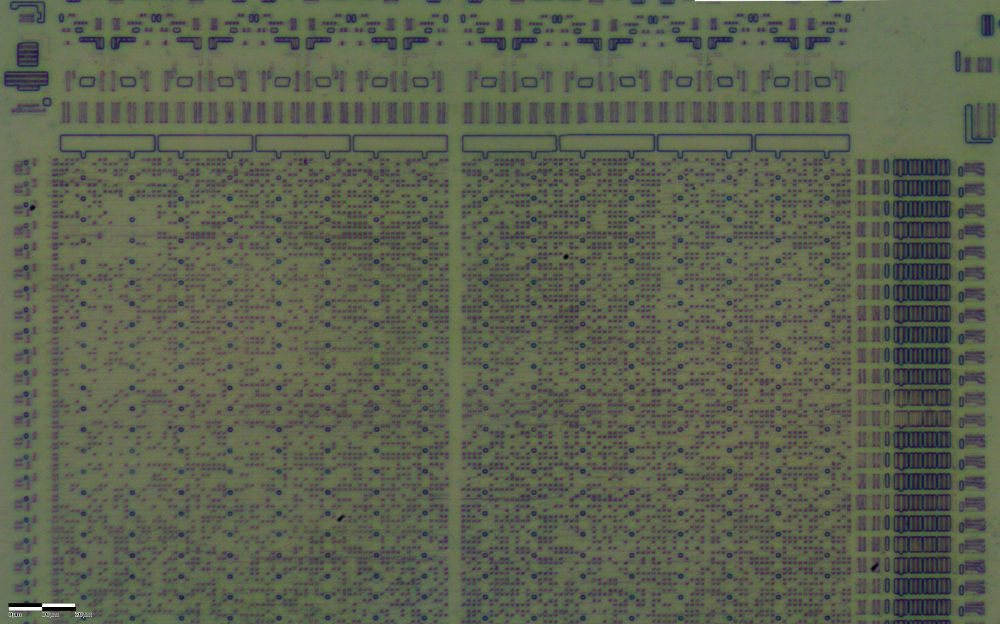

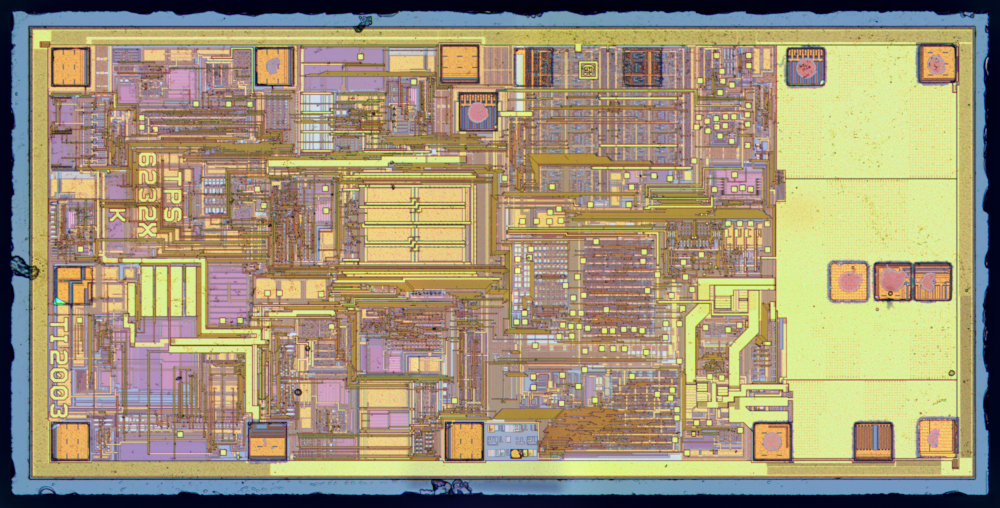

Gambar 2. Cuplikan dari topologi op-amp OPA134PA. Sumber - zeptobars.comDi sini , omong-omong, ada contoh rekayasa balik chip TL431 yang dibuat oleh Ken Shirriff dari foto BarsMonster. Dan inilah terjemahan bahasa Rusia. Blog Ken memiliki banyak hal keren jika Anda tertarik dengan topik reverse engineering amatir.Dan di sini (hati-hati, lalu lintas!) Adalah laporan dari rekayasa terbalik chip Zilog Z80-CTC, dibuat pada tahun 1979, hampir segera setelah rilis chip. Sekarang ini adalah dokumen historis yang unik, dan kemudian informasi yang bernilai komersial luar biasa dan diperoleh (dilihat dari beberapa referensi standar militer), mungkin dalam proses sertifikasi sirkuit mikro untuk aplikasi khusus.Tetapi kita hidup pada tahun 2019, dan bukan pada tahun 1979, dan sekarang membalikkan skema lengkap dari mikroprosesor Intel baru adalah masalah berbulan-bulan atau bertahun-tahun, bahkan dengan tingkat otomatisasi proses yang baik (belum lagi fakta bahwa bahkan dengan resolusi yang dapat diterima kita dapat menembak topologi dengan standar desain 14 -10-7 nm adalah tugas yang sangat sulit). Apa itu Intel? Bandingkan jumlah pekerjaan pada rekayasa balik atau analisis amplifier dari gambar di atas dan prosesor Baikal-T1, yang dilakukan sesuai dengan proses pembuatan 28 nm yang sangat populer dan relatif terjangkau. Rekayasa balik penuh dari produk besar semacam itu sangat jarang, sering kali menarik untuk melihat beberapa blok yang spesifik dan relatif kecil. Misalnya, untuk mengetahui apakah mereka melanggar paten Anda, atau membandingkan keputusan Anda dengan produk-produk pesaing dan mencoba memahami mengapa itu lebih baik atau lebih buruk. Atau, untuk mengetahuinya, pengembang chip sendiri yang mengimplementasikan fungsi ini atau itu, atau meminjam blok IP Anda.

Gambar 3. Cuplikan dari topologi prosesor Baikal-T1. Sumber - zeptobars.com

Gambar 3. Cuplikan dari topologi prosesor Baikal-T1. Sumber - zeptobars.comDi sini kita beralih ke bagian penting berikutnya dalam sejarah reverse engineering. Pada zaman kuno, seluruh chip dikembangkan dari awal hingga akhir dalam satu perusahaan, kadang-kadang bahkan oleh kekuatan tim yang sangat kecil atau penyendiri yang cemerlang seperti Bob Widlar. Sirkuit mikro modern penuh dengan blok IP, penjualan dan pembeliannya merupakan pasar besar, yang, tentu saja, juga memiliki kendali hak cipta, spionase industri, dan pembajakan. Oleh karena itu, adalah mungkin dan perlu untuk melihat masalah perlindungan terhadap penyalinan yang tidak sah tidak hanya dari sudut pandang pengembang produk akhir, tetapi juga dari sudut pandang pengembang IP, yang bagi siapa pengembang produk juga dapat menjadi bajak laut.

Dalam kasus peretasan, struktur internal penyusup biasanya tidak menarik untuk menerima data, dan rekayasa balik sebagian dilakukan (jika sama sekali) untuk menemukan kerentanan dan mengeksploitasi kerentanan ini, baik menggunakan koneksi langsung atau menggunakan metode lain. Tugas pengembang terhadap peretasan adalah untuk mencegah penggunaan titik-titik yang berpotensi lemah dan, jika perlu, untuk menghancurkan data sensitif ketika mencoba meretas.

ORANG YANG BERTINDAK

Untuk memulai, mari cari tahu siapa yang dapat melindungi desain chip dari itu. Entitas berikut terlibat dalam rantai dari ide ke aplikasi, memiliki berbagai jenis akses ke informasi tentang isi dari rangkaian mikro.

- Pengembang blok IP. Ia memiliki semua informasi, semua file yang diperlukan, metode pengukuran, dll. dll.

- Pengembang chip. Dalam kasus Soft IP, Verilog / VHDL memiliki kode blok, dalam kasus Hard IP, dapat memiliki topologi atau kotak hitam. Jika ada bagian yang dapat diprogram atau perangkat lunak dalam unit, unit ini juga memiliki akses ke sana.

- Pabrik Memiliki akses ke file topologi GDSII, tetapi tidak memiliki akses ke bagian chip yang bergantung pada perangkat lunak (misalnya, untuk PROM firmware).

- Pengepakan dan pengujian produksi. Ini memiliki akses ke chip, serta untuk menguji metode dan kartu firmware untuk satu kali memori yang dapat diprogram. Jarang ada yang membela dengan sengaja dari mereka, tetapi mereka harus ada dalam daftar, karena beberapa metode yang sesuai untuk perlindungan dari pabrik tidak bekerja melawan mereka.

- Pesaing / cracker. Ini hanya memiliki akses ke produk jadi dan dokumentasi pengguna.

Dalam kasus yang paling sederhana, perancang chip (2) ingin melindungi dirinya dari penyalinan oleh pesaing (5) atau membuat chip dengan memori yang dilindungi dari pembacaan yang tidak sah. Dalam yang sedikit lebih rumit, pengembang IP (1) ingin memastikan bahwa pengembang mematuhi chip (2) dari perjanjian lisensi. Juga terjadi bahwa pengembang chip (2) tidak mempercayai pabrik (3) dan mencurigai bahwa hal itu dapat mendorong pemalsuan pada shift malam.

Saya menulis secara terperinci tentang apa IP dalam sirkuit terintegrasi beberapa waktu lalu, jadi saya tidak akan mengulangi artikel ini. Ada juga sedikit tentang bagaimana pengembang IP melindungi kekayaan intelektual mereka. Singkatnya, untuk melindungi topologi, pabrik biasanya berpartisipasi sebagai pihak ketiga, dan pembeli tidak menerima topologi yang tepat, dan teknik kebingungan yang serupa dengan kode lainnya digunakan untuk mengamankan kode Verilog.ALAT

Alat analisis microchip apa yang ada? Tingkat pertama adalah sedikit asam untuk pertama-tama membuka kasing sirkuit mikro, dan kemudian menghapus lapisan satu per satu, dan mikroskop optik biasa dengan kamera. Itu tidak mahal, mudah untuk bekerja dengan mereka, dan untuk analisis rangkaian sederhana yang dibuat menggunakan bukan teknologi terbaru, ini sudah cukup.

Untuk skema yang lebih besar, ada sistem CAD khusus yang memungkinkan satu atau lain cara untuk mengotomatiskan pemulihan data dari topologi - memberikan insinyur reverse dengan antarmuka yang lebih nyaman untuk bekerja daripada hanya menggambar garis dalam editor grafis. Otomasi juga disederhanakan oleh fakta bahwa semua sirkuit digital modern dibangun dari perpustakaan, dan setelah membalik elemen perpustakaan rekayasa untuk merakit sirkuit adalah masalah waktu (atau kekuatan pemrosesan yang tersedia).

Tingkat berikutnya, tidak dapat diakses oleh amatir, tetapi hadir di laboratorium khusus adalah mikroskop elektron pemindaian (SEM). Ia menggunakan berkas elektron terfokus alih-alih berkas cahaya. Resolusi SEM dapat mencapai 1 nm dan bahkan sedikit lebih rendah, yang cukup untuk menganalisis setiap sirkuit terintegrasi modern.

FIB adalah analog dari SEM, hanya menggunakan balok ion yang lebih berat daripada sinar elektron. Sebenarnya, FIB adalah Beam Ion Terfokus. Perbedaan utama antara FIB dan SEM adalah bahwa dengan bantuannya Anda tidak hanya dapat menganalisis rangkaian mikro, tetapi juga memodifikasinya, misalnya membuat potongan (untuk melihat bagian melintang dari rangkaian mikro atau melepaskan bagian) atau bahan semprot (untuk membuat koneksi di sana dimana tidak). FIB secara luas digunakan oleh pengembang dan produsen sirkuit mikro untuk bekerja dengan sampel uji, karena dibutuhkan banyak waktu untuk memperbaiki kesalahan dalam menggunakannya, tetapi masih jauh lebih cepat dan lebih murah daripada memulai kembali batch eksperimental. Untuk insinyur balik, ini juga merupakan cara unik untuk sampai ke bagian-bagian kristal yang, menurut niat pengembang, tidak boleh tersedia. Dan, ketika merancang chip yang dilindungi dari peretasan, ini juga harus diingat.

Gambar 4. Penampang dari sirkuit mikro yang dibuat menggunakan FIB. Sumber - SERESSA-2015 (hati-hati, banyak lalu lintas di pdf dari tautan).

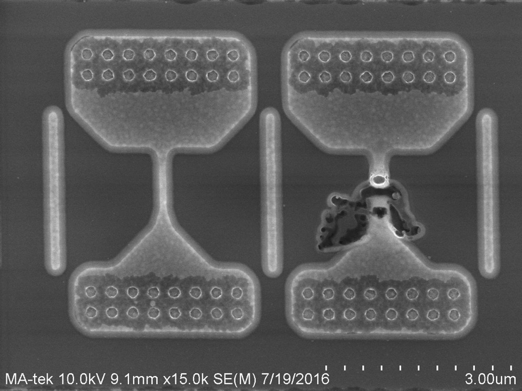

Gambar 4. Penampang dari sirkuit mikro yang dibuat menggunakan FIB. Sumber - SERESSA-2015 (hati-hati, banyak lalu lintas di pdf dari tautan). Gambar 5. Dibuat oleh FIB modifikasi chip, mengubah beberapa koneksi.

Gambar 5. Dibuat oleh FIB modifikasi chip, mengubah beberapa koneksi.Alat lain yang sangat diperlukan untuk insinyur balik adalah seperangkat laser. Kipas dapat menggunakan laser kuat yang dapat digunakan untuk membuka sirkuit mikro dalam wadah plastik dan mendapatkan akses ke kristal. Untuk laser profesional, tergantung pada panjang gelombang, beberapa bagian dari desain sirkuit mikro mungkin transparan dan yang lain tidak transparan. Ini memungkinkan Anda untuk menggunakan laser, misalnya, untuk secara pasif membuka passivasi dan insulasi, sehingga nantinya Anda dapat dengan mudah bergabung dengan garis logam tanpa risiko korslet dengan tetangganya. Parameter lain akan memungkinkan Anda untuk memotong logam atau membakar masing-masing transistor. Yang ketiga adalah untuk menginduksi arus dalam transistor dengan menukar sel cache atau semacam garis logis. Opsi terakhir secara universal digunakan sebagai simulasi efek murah dari partikel bermuatan berat, tetapi pada prinsipnya, kegagalan fungsi dalam rangkaian mikro yang berfungsi juga dapat berguna untuk mengkompromikan informasi yang terkandung di dalamnya. Misalnya, mungkin menarik untuk menulis ulang beberapa flag dalam file register atau sedikit memperbaiki operasi generator angka acak.

Gambar 6. Penampilan laser untuk mempelajari efek dari kegagalan tunggal pada sirkuit mikro. Sumber - SERESSA-2015.

Gambar 6. Penampilan laser untuk mempelajari efek dari kegagalan tunggal pada sirkuit mikro. Sumber - SERESSA-2015. Gambar 7. Contoh sensitivitas bagian dari rangkaian mikro terhadap satu kesalahan dan kegagalan yang diperoleh dengan menggunakan kartu laser. Sumber - SERESSA-2015.

Gambar 7. Contoh sensitivitas bagian dari rangkaian mikro terhadap satu kesalahan dan kegagalan yang diperoleh dengan menggunakan kartu laser. Sumber - SERESSA-2015.Di laboratorium rekayasa balik canggih, Anda dapat menemukan banyak alat menarik lainnya; misalnya, sinyal digital hingga beberapa puluh MHz dapat dipantau secara real time dengan menempatkan sepotong kecil lithium niobate pada saluran yang sesuai dan sekali lagi menerangi dengan laser.

KASUS 1: PABRIK YANG TIDAK DAPAT DIANDALKAN

Apa yang bisa menjadi alasan untuk tidak mempercayai pabrik tempat Anda membuat kristal? Di dunia yang ideal, tentu saja, Anda tidak akan terlibat dengan pabrik yang tidak Anda percayai, tetapi terkadang pertimbangan komersial memaksa Anda mengambil risiko. Ini dapat diminimalkan dengan dua cara utama:

- Yang disebut perpecahan fabrikasi atau, dengan cara sederhana, produksi di dua pabrik. Tetapi tidak secara paralel (seperti yang biasanya dilakukan untuk meminimalkan risiko kekurangan jika terjadi penundaan produksi yang tak terduga), tetapi bagian dari operasi di satu pabrik dan sebagian di yang lain. Ini agak merepotkan bagi semua peserta dalam proses (dan tentu saja tidak setiap pabrik akan menyetujui ini), tetapi ini akan memaksa pabrik yang tidak dapat diandalkan untuk setidaknya membalikkan sisa desain chip dan membuat topeng yang hilang dengan sendirinya. (yang, idealnya, harus membuat permainan tidak bernilai lilin). Kerugian utama dari pendekatan ini adalah bahwa lapisan atas chip adalah metalisasi, yang rekayasa baliknya cukup sederhana. Pembuatan fabrikasi, bagaimanapun, dapat benar-benar efektif dalam kombinasi dengan beberapa pengetahuan teknologi dalam logam, yang tidak dapat direproduksi oleh pabrik yang tidak dapat diandalkan. Sebagai contoh, jika pabrik kedua pilihan Anda mampu membuat memori non-volatile (MRAM, memristor atau sesuatu seperti itu) di lapisan metalisasi atas, yang tanpanya seluruh desain kehilangan artinya.

- Jika Anda tidak memiliki pengetahuan teknologi, maka cara yang sederhana dan dapat diandalkan adalah membuat chip tidak berarti tanpa pemrograman lebih lanjut. Blok yang dapat diprogram dapat dibuat secara independen menggunakan memori konfigurasi, atau dalam bentuk blok berdasarkan pada FPGA tertanam (ada IP seperti itu di pasaran). Memori konfigurasi sebagai cara perlindungan memungkinkan Anda untuk memastikan bahwa pabrik tidak bisa hanya mengambil dan memproduksi chip Anda melewati Anda. Tetapi Anda dapat membaca memori konfigurasi, bukan? Ya, tetapi keberadaan memori konfigurasi memaksa pabrik yang tidak dapat diandalkan, alih-alih cara sederhana untuk meningkatkan volume produksi, untuk melakukan rekayasa balik yang sama dengan semua penyerang lainnya.

Secara terpisah, saya perhatikan bahwa kedua metode perlindungan yang dijelaskan dari pabrik yang tidak dapat diandalkan membantu melawan penyalinan yang tidak sah, tetapi keduanya tidak menyelamatkan dari "bookmark" yang populer di kalangan sempit. Selain itu, sedikit lebih jauh saya akan berbicara tentang bagaimana cara penandaan topologi sendiri.

KASUS 2: PERLINDUNGAN MEMORI

Kehadiran blok yang dapat diprogram dan memori konfigurasi dalam chip adalah atribut yang hampir tak terpisahkan dari setiap desain modern, baik digital maupun analog. Dengan penurunan standar desain, penyebaran parameter dari chip ke chip meningkat, dan tuning digital adalah cara termudah dan paling dapat diandalkan untuk mengatasinya. Dan sirkuit digital (misalnya mikrokontroler) biasanya menyimpan data secara langsung pada chip dan dapat memiliki struktur memori multi-level, bagian-bagian yang berbeda memiliki tingkat akses dan perlindungan yang berbeda. Oleh karena itu, tampaknya logis untuk pertama-tama menggunakan alat yang sudah kita miliki untuk meningkatkan keamanan dan ketahanan terhadap retakan, dan kedua, ide untuk berpikir dengan hati-hati tentang jenis memori yang digunakan.

Firmware dengan koneksi logam (Mask ROM). Biasanya sepertinya ada atau tidak adanya kontak antara dua garis logam, sedikit lebih jarang - seperti ada atau tidak adanya transistor di antara mereka. Yang paling oak digunakan dalam kristal matriks dasar (BMC) - tidak hanya di industri pertahanan kuno, seperti yang mungkin Anda pikirkan, tetapi juga dalam solusi yang cukup modern, misalnya, dalam chip tambahan di dalam prosesor Xeon. Selain itu, dengan menggunakan memori seperti itu, dibuat rangkaian mikrokontroler (terutama mikrokontroler), karena mem-flash memori di pabrik dengan mengubah satu penutup lebih murah daripada firmware universal setiap kristal yang diproduksi di piring atau dalam kasing. Masker ROM mudah dibaca dengan mikroskop dan etsa yang akurat. Di rumah, Anda bisa mengatasinya.

Gambar 8. ROM firmware dengan interkoneksi logam pada chip FTDI FT232RL palsu. Sumber - zeptobars.com

Gambar 8. ROM firmware dengan interkoneksi logam pada chip FTDI FT232RL palsu. Sumber - zeptobars.com

Perlu juga dicatat di sini bahwa dimungkinkan untuk mem-flash memori tidak hanya dengan lapisan kontak antara logam, tetapi juga dengan ada dan tidak adanya logam (mudah dibaca secara optik), ada atau tidak adanya doping (mudah dibaca secara optik), atau, misalnya, tegangan ambang transistor yang dikendalikan oleh tingkat doping (buruk) baca secara optis). Jadi, pada prinsipnya, mask ROM tidak kehilangan semuanya jika Anda benar-benar ingin menyembunyikan isinya.

Memori pada jumper yang terbakar (ROM Fuse). Ini memungkinkan satu rekaman (termasuk rekaman oleh pengguna pada perangkat yang sudah jadi) dan jumlah pembacaan yang tidak terbatas, sangat mudah untuk diproduksi dan diprogram, dan karenanya populer untuk semua jenis memori konfigurasi dan firmware.

Gambar 9. Dua status ROM Fuse. Sumber - semiengineering.com

Gambar 9. Dua status ROM Fuse. Sumber - semiengineering.comSeperti yang Anda lihat, keadaan jumper fusible biasa (Fuse) sangat mudah dilihat melalui mikroskop, yaitu, sangat tidak mungkin untuk melindungi diri dari membuka kristal bersamanya. Yah dan, selain yang lainnya, jumper burn-out klasik cukup besar (beberapa mikron persegi) dan karenanya tidak cocok untuk sejumlah besar memori.

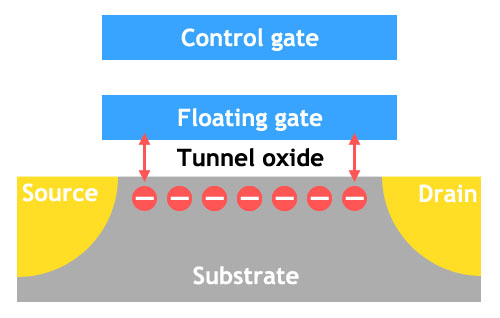

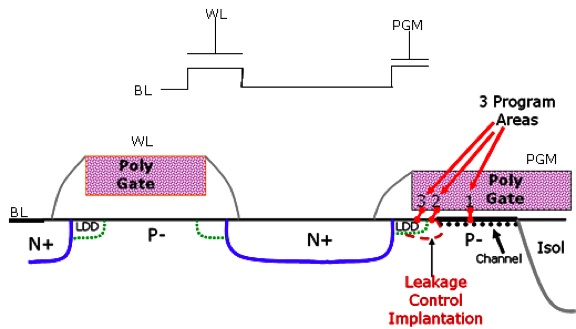

Memori flash dan opsi EPROM dan EEPROM lainnya berdasarkan transistor gerbang mengambang.

Gambar 10. Skema perekaman flash. Sumber - techreport.com

Gambar 10. Skema perekaman flash. Sumber - techreport.comPrinsip pengoperasian jenis memori ini cukup sederhana: gerbang "mengambang" terletak di lapisan tebal dielektrik. Muatan listrik dapat ditempatkan di rana ini dengan penerowongan, menerapkan tegangan tinggi untuknya. Dan kemudian, jika Anda tidak menerapkan tegangan tinggi, muatannya dapat disimpan dalam rana "mengambang" untuk waktu yang sangat lama.

Bagaimana dengan keamanan? , EEPROM . ? .

, EEPROM , ( ). , , , , , . : EEPROM, . , - , . , ( ), . , , , , . , , , , , , .

/ , , .

— , . , , , , , .

MRAM , , , . , , . MRAM, , , , , . ? . , MRAM — , - fabless- .

-

antifuse ROM . , , . ? . , , FIB, , . , , , . , — .

11. antifuse . . .

11. antifuse . . ., , . — FIB , , , . , , . ? , , . , Cypress:

It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.: , . , , , ( ), , , , ( ). , , .

, , ( ) (, , ). , , , FIB . , , , , .

, . , X, 100*X, :

0 — 800*X

1,2,4, …, 64, 128 — 701*X

3, 6, 7, …, 160, 192 — 602*X

….

255 — 8*X

, , 256 . , — 701*X — . , ? - — ; . , , , , ?

3:

Tetapi bagaimana jika chip Anda tidak mengandung memori konfigurasi atau hanya mengandung beberapa bit, yang tidak ada artinya untuk disembunyikan. Mengapa Jadi itu jauh lebih murah (bukan dengan mengurangi biaya masker untuk litografi, tetapi dengan proses pengemasan dan pengujian yang lebih sederhana), dan untuk sebagian besar keripik sederhana, harga merupakan keunggulan kompetitif yang serius.

Berbicara tentang pengujian. Proses menolak kristal pada wafer dan mem-flash memory konfigurasi sering dilakukan oleh pihak luar, terutama oleh perusahaan kecil, karena peralatan yang sesuai biasanya tidak terjangkau untuk startup, dan kualitas harus dipastikan. Jadi, jika produksi pihak ketiga mutakhir dengan metode pengujian Anda dan memiliki firmware memori konfigurasi, maka akan lebih baik bagi Anda untuk sepenuhnya mempercayai orang-orang ini. Atau memiliki metode perlindungan tambahan terhadap rekayasa balik yang tidak terikat pada memori konfigurasi.

Jadi apa yang harus dilakukan jika memori konfigurasi bukan pilihan untuk perlindungan, atau jika itu tidak cukup?

Kelemahan utama dari kedua mikroskop optik dan SEM adalah sangat sulit untuk membedakan antara jenis doping silikon. Artinya, keberadaan paduan terlihat, tetapi tipenya tidak. Oleh karena itu, ketika menganalisis topologi dan ekstraksi rangkaian, jenis doping dipulihkan dari konteks dan logika tersirat dari sirkuit (n-channel transistor terhubung ke ground, p-channel transistor terhubung ke daya, dll., Dll). Setelah menggambar topologi dari rangkaian mikro Anda sehingga tidak bertepatan dengan opsi yang paling mungkin secara intuitif, Anda dapat merusak darah seorang insinyur terbalik. Terutama jika Anda menggunakan beberapa skema berbeda yang menyamar sebagai sama. Dengan ketangkasan tertentu, Anda tidak hanya dapat menyulitkan analisis sirkuit Anda, tetapi juga membuat perangkat (atau setidaknya dimodelkan, tetapi lebih menyenangkan jika diproduksi) menggunakan topologi yang dipulihkan melakukan sesuatu yang spesifik, dari mempersingkat tanah dengan kekuatan untuk mengeluarkan kata-kata cabul ke semua output. Omong-omong, perilaku deterministik dari desain yang dicuri secara keliru dapat berguna tidak hanya untuk membakar osiloskop ke bajak laut, tetapi juga untuk memastikan bahwa ketika nanti Anda menerima pengguna chip Anda yang kecewa, Anda dapat dengan jelas menunjukkan kepada mereka bahwa mereka membeli gadungan.

Gambar 12. Bagian tiga struktur tidak bisa dibedakan dengan mikroskop. Yang kiri adalah pMOSFET, yang tengah adalah hubung singkat, yang kanan adalah dioda bias terbalik (celah).

Gambar 12. Bagian tiga struktur tidak bisa dibedakan dengan mikroskop. Yang kiri adalah pMOSFET, yang tengah adalah hubung singkat, yang kanan adalah dioda bias terbalik (celah). Gambar 13. Topologi tiga sel perpustakaan digital tidak dapat dibedakan dengan mikroskop. Yang kiri adalah inverter, yang di tengah adalah koneksi langsung dari input dan output, yang kanan adalah unit logis dari output.

Gambar 13. Topologi tiga sel perpustakaan digital tidak dapat dibedakan dengan mikroskop. Yang kiri adalah inverter, yang di tengah adalah koneksi langsung dari input dan output, yang kanan adalah unit logis dari output.Setiap sel pada gambar di atas terlihat hampir seperti inverter yang paling biasa, tetapi sebenarnya bisa menjadi inverter, repeater, atau generator dari unit logis nol atau logis. Hanya kontak kami untuk difusi dari input dan output yang memberikan “inverter” kami. Namun, dengan mengabaikannya, kita mendapatkan yang benar-benar tidak dapat dibedakan dari sirkuit reguler dengan imbalan ketidakmampuan untuk mengimplementasikan koneksi input dan output (tetapi kita dapat menggunakan dua inverter untuk tujuan ini). Namun, dengan kemampuan untuk membalikkan atau tidak membalikkan sinyal menggunakan sel yang sama, pertarungan melawan penyerang jauh lebih menarik, karena tidak ada yang menyulitkan upaya untuk menangani masalah desain yang tidak dikenal seperti inverter tambahan di suatu tempat di jam atau sirkuit on / off.

Meski tidak, itu terjadi. Topologi tangan yang dibangun dengan baik biasanya dibaca dengan baik. Contoh yang bagus adalah dalam blog Ken Schirriff yang sudah disebutkan.

Gambar 14. Unit logika aritmatika (ALU) dari chip Intel 8008. Digit terpisah ditampilkan.

Gambar 14. Unit logika aritmatika (ALU) dari chip Intel 8008. Digit terpisah ditampilkan.Pada topologi ALU Intel 8008, delapan sirkuit identik terlihat sempurna - dengan jumlah bit. Memahami bahwa ini adalah ALU, Anda dapat dengan mudah mengembalikan skema topologi. Jika beberapa elemen di dalamnya salah, ini akan sedikit mempersulit pekerjaan Anda, tetapi tidak lebih. Dan semua karena topologi cocok dengan ide dasar antarmuka antara bagian-bagian penyusunnya. Untuk membingungkan penyerang begitu banyak sehingga ia meninggalkan upaya reverse engineering, perlu untuk membuat topologi tidak dapat diprediksi dan tidak berulang. Cara termudah adalah tidak membuat blok apa pun secara manual, tetapi untuk menghasilkan seluruh netlist chip menggunakan CAD. Pelacak otomatis, meskipun menghemat banyak waktu untuk membuat topologi (dibandingkan dengan pekerjaan manual), melakukan pekerjaan yang sangat baik untuk menciptakan pengaturan elemen yang tidak intuitif dan di tempat-tempat koneksi yang benar-benar gila. Dan semakin besar desainnya, topologi yang disintesis secara keseluruhan, semakin sulit untuk membalikkan insinyur.

Tapi ini cara termudah. Ada opsi yang lebih menarik. Sebagai contoh, gunakan satu set sel bunglon sebagai satu set generator nol logis dan satu untuk input multiplexer, sambil menyadari fungsi logis sewenang-wenang. Sebenarnya, ini adalah bagaimana elemen-elemen FPGA, LUT (Look-Up Table) diatur.

Gambar 15. Implementasi LUT tiga input. Sumber

Gambar 15. Implementasi LUT tiga input. SumberDengan meletakkan beberapa LUT tersebut di tempat yang berbeda di sirkuit dan membawa beberapa sinyal ke input "sel memori", kami akan menyelesaikan beberapa masalah sekaligus:

- Jika manuver kami tetap tidak terpecahkan, maka kami akan dapat mengatur bagaimana tepatnya rangkaian engine reverse-engine akan berperilaku. Opsi - apa saja, hanya dibatasi oleh imajinasi Anda.

- Menggunakan sinyal sewenang-wenang dari blok lain sebagai "input" untuk sel-sel menghasilkan nol logis dan satu akan mempersulit proses pemisahan visual dari desain menjadi blok.

- Bahkan jika reverse engineer menyadari bahwa kami menggunakan LUT yang dilindungi seperti itu, ia harus memilah-milah banyak opsi untuk mengembalikan fungsionalitas sirkuit sesuai dengan topologi, sehingga bahkan jumlah sel terlindung yang relatif kecil dapat membuat rekayasa balik memakan waktu yang tidak perlu. Favorit saya adalah merakit mesin negara pada LUT yang mengontrol transisi sirkuit mikro dari satu mode operasi ke mode operasi lainnya.

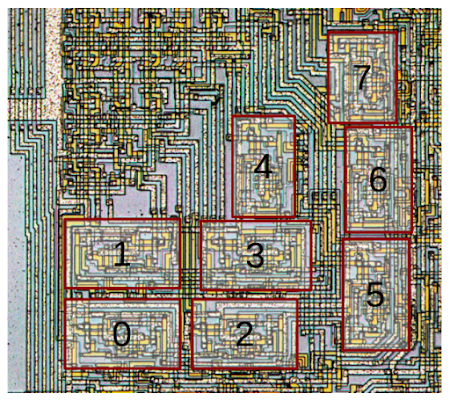

DIAGRAM UJI

Insinyur yang baik sangat menyukai pengujian chip mereka secara komprehensif. Dan dengan "komprehensif" maksud saya - kira-kira dengan cara yang sama seperti pada konverter TI DC / DC pada gambar di bawah ini. Lusinan bantalan kontak kecil, yang dapat Anda sambungkan sebelum memotong pelat menjadi kristal yang terpisah, untuk memeriksa semua parameter yang diperlukan, status jalur internal yang penting, memutuskan apakah chip tersebut cocok atau tidak, dan jika perlu, cari tahu penyebab masalahnya.

Gambar 16. Topologi Texas Instruments TPS 62321. Sumber - zeptobars.com

Gambar 16. Topologi Texas Instruments TPS 62321. Sumber - zeptobars.comCakupan yang baik dengan bantalan uji untuk peluncuran uji dan prototipe sangat penting, tetapi untuk produksi serial, sering dimatikan (dengan koreksi satu atau dua masker atau jumper yang dapat dibakar) untuk meminimalkan efek pada perilaku produk. Jadi, apa yang saya bicarakan? Test pad kontak adalah bantuan besar Anda untuk seorang penyerang, karena Anda tidak hanya menunjukkan poin-poin penting dalam desain sendiri, tetapi juga memberikan akses mudah ke mereka. Jumper yang terbakar dengan mudah dipulihkan pada FIB, dan voila! Idealnya, keamanan membutuhkan pelepasan seluruh test pad dari chip serial. Jika opsi ini tidak rasional (misalnya, Anda juga perlu pengujian pada pelat dalam produksi serial), maka setidaknya pastikan bahwa mekanisme untuk memutus situs pengujian tidak dapat dipulihkan, misalnya, terletak langsung di bawah platform dan ditarik sehingga celahnya tidak dapat terhubung dengan mudah.

Saya bahkan tidak ingin memulai tentang kenyataan bahwa semua desain digital modern memiliki JTAG bawaan untuk pengujian, yang memungkinkan Anda untuk secara langsung melihat status pemicu pada sebuah chip. Kesesuaian pengujian adalah salah satu karakteristik utama dari desain apa pun, dan inilah fakta yang membuatnya sangat penting untuk secara aman dan permanen menonaktifkan semua antarmuka uji sebelum chip meninggalkan dinding pabrik.

Insinyur yang baik masih suka menempatkan sirkuit uji di pinggiran chip untuk revisi berikutnya. Biasanya ini adalah skema yang cukup penting, jika tidak mengapa buang waktu dan upaya mengatur pengujian mereka? "Sirkuit penting yang membentuk kekayaan intelektual Anda dan sangat penting untuk berfungsinya chip?" Dipisahkan dengan cermat dari keseluruhan desain? Terima kasih banyak! " - insinyur balik akan memberitahu Anda untuk hadiah kerajaan seperti itu. Jika Anda tidak ingin yang pengujian membantu penyerang mempelajari dan menyalin desain Anda, pastikan bahwa mereka tidak masuk ke kristal untuk produksi massal atau dihancurkan setelah pengujian di atas piring selama proses pemotongan piring menjadi kristal.

PRAKTEK KECIL

Untuk sekali lagi menunjukkan bagaimana ini bekerja,

contoh membuka mikrokontroler PIC12C508A yang dijelaskan dalam disertasi Sergei Skorobogatov, dipertahankan pada tahun 2004 di Cambridge. Terjemahan singkat dan agak gratis:

Hal ini diperlukan untuk membuka kasing dan menemukan pada chip memori pelindung terhapus oleh radiasi ultraviolet. Ini dilakukan dengan cukup mudah dengan melihat baris yang menuju pin pemrograman chip. Kemudian Anda menutupi memori utama dengan bahan buram untuk UV, dan setelah lima hingga sepuluh menit paparan, Anda dapat mempertimbangkan memori sebagai programmer biasa. Pilihan lain - setelah menemukan memori perlindungan penyalinan, cukup potong jalur logam yang mengarah ke sana, yang pada chip ini karena beberapa alasan terletak jauh dari garis lain - sejauh ini Anda dapat memotongnya tidak hanya dengan FIB, tetapi hanya dengan jarum. Gambar 17. Dan ini adalah garis yang sangat disayangkan. Memang, itu terletak di tengah-tengah ruang kosong, tidak dilindungi dengan cara apa pun, itu bisa dipotong.

Gambar 17. Dan ini adalah garis yang sangat disayangkan. Memang, itu terletak di tengah-tengah ruang kosong, tidak dilindungi dengan cara apa pun, itu bisa dipotong.KESIMPULAN

Tentu saja, tidak mungkin untuk memahami besarnya, karena teknologi dan rekayasa terbalik dari sirkuit mikro, dan perlindungan terhadapnya, tidak tinggal diam dan terus ditingkatkan. Topik keamanan informasi adalah salah satu kunci dalam desain untuk Internet of things, sehingga pengembang menaruh banyak perhatian padanya, dan membalikkan insinyur tidak dapat mengharapkan ekstraksi semudah lima belas atau dua puluh tahun yang lalu. Namun demikian, kita harus selalu ingat bahwa sistem yang terlindungi dengan buruk berarti potensi kerugian, kerugian besar atau bahkan nyawa orang, dan perlindungan terhadap akses yang tidak sah dan rekayasa balik harus menjadi bagian dari sistem di semua tingkatan operasi, tidak termasuk yang "besi". .