Meskipun 14 tahun telah berlalu sejak

SSD SATA pertama diperkenalkan, banyak konsumen masih mengacu pada solid-state drive dengan cukup banyak skeptisisme. Alasan utama ketidakpercayaan adalah terbatasnya sumber daya kerja memori flash, karena degradasi bertahap dari struktur semikonduktor chip, sebagai akibatnya perangkat cepat atau lambat kehilangan kemampuan mereka untuk merekam dan menyimpan informasi. Spesifikasi teknis terperinci sering kali hanya memperburuk situasi: sulit bagi pembeli untuk memahami apakah TBW 500 TB yang disebutkan dalam deskripsi Western Digital Blue 3D NAND SATA SSD untuk dua terabyte banyak atau sedikit? Berapa banyak drive seperti itu akan bertahan dalam kondisi operasi nyata dan dapatkah dipercaya dengan file yang paling berharga? Mari kita coba memahami masalah ini bersama-sama dan membicarakan tentang seberapa kuat memori flash modern.

Sebenarnya, jawaban untuk "pertanyaan utama kehidupan, alam semesta dan semua itu" diterima kembali pada bulan Desember 2014, ketika orang-orang dari publikasi jaringan

TechReport menyelesaikan pengujian SSD konsumen, yang berlangsung total satu tahun. Dengan menggunakan produk HyperX, Corsair, Kingston, dan Samsung sebagai contoh, mereka telah membuktikan dengan meyakinkan bahwa kehidupan nyata SSD melebihi 1 petabyte dubbing. Volume seperti itu hampir tidak terpikirkan tidak hanya untuk pengguna rata-rata, tetapi bahkan untuk pembuat konten profesional: drive akan menjadi usang secara moral jauh lebih awal daripada sumber dayanya habis.

Namun, ada satu nuansa signifikan: empat tahun lalu, chip MLC NAND digunakan, mampu menyimpan 2 bit informasi di setiap sel dan diproduksi menggunakan teknologi proses 25-nanometer. Pada saat itu, itu adalah kompromi yang baik antara SLC (sel tingkat tunggal) yang sangat andal dan TLC yang lebih luas dan murah (sel tiga tingkat): chip dengan sel dua-bit memberikan kepadatan penyimpanan data yang dapat diterima, menahan hingga 5.000 siklus penulisan / penghapusan (dalam rata-rata, angka ini mencapai 3 ribu). Apa yang tidak dapat dikatakan tentang saudara-saudara terdekat mereka: untuk semua keuntungan, yang mencakup kapasitas tinggi dan biaya rendah, TLC jauh lebih tangguh, karena hampir tidak mengambil bar 1.500.000 siklus pemrograman / penghapusan, meskipun fakta bahwa kebanyakan mikrokontroler planar hampir tidak dapat menahan seribu.

Penyebab utama dalam situasi ini adalah transisi ke proses 15-nanometer yang digunakan dalam produksi chip. Untuk memahami mengapa ini terjadi, ingat saja bagaimana memori NAND bekerja. Pengkodean bit informasi terjadi dengan mengubah muatan pada gerbang mengambang karena tunneling kuantum elektron melalui lapisan dielektrik, karena kekuatan medan listrik yang tinggi.

Rangkaian transistor gerbang mengambangDari sudut pandang fisika, kita berhadapan dengan tidak lebih dari fenomena kerusakan seperti longsoran salju yang dapat dibalikkan. Dipercepat dalam medan listrik, elektron menerima energi kinetik yang cukup untuk ionisasi dampak dari molekul dielektrik, menghasilkan sepasang partikel elementer yang membawa muatan berlawanan, yang juga dipercepat oleh medan listrik, dan proses berulang, sementara jumlah pembawa muatan meningkat secara eksponensial (oleh karena itu namanya ) Mudah ditebak bahwa proses tersebut menyebabkan keausan bertahap lapisan dielektrik, sebagai akibatnya, kemungkinan kebocoran muatan ke sel tetangga meningkat, yang, pada gilirannya, menyebabkan kerusakan atau bahkan hilangnya data sama sekali. Dan transisi ke teknologi proses baru hanya memperburuk situasi: penurunan ketebalan dielektrik mengarah pada fakta bahwa sel-sel gagal jauh lebih awal.

Namun, jika masalahnya hanya ini, konsumen biasa, dan pengguna korporat, tidak akan melihat perbedaan antara MLC dan TLC, dan dalam spesifikasi teknis untuk SSD kita akan melihat angka yang jauh lebih mengesankan. Pada kenyataannya, gambar yang sangat berbeda muncul di depan mata kita, dan arsitektur chip flash dan spesifik pekerjaan mereka adalah alasan untuk ini: sel-sel individual digabungkan menjadi halaman, dan halaman menjadi blok, sementara merekam informasi hanya mungkin dilakukan di halaman kosong, dan penghapusannya dilakukan blok demi blok.

Apa artinya ini dalam praktik? Misalkan kita memiliki sebagian blok yang terisi dan kami ingin menulis data baru untuk itu. Jika volumenya kurang dari ruang kosong yang tersisa, perekaman terjadi secara instan, tanpa manipulasi tambahan. Jika tidak ada cukup ruang, algoritme multi-tahap yang rumit ikut berperan. Perhatikan situasi pada diagram di bawah ini.

Ini adalah bagaimana data ditulis ke memori flashData baru yang ingin kami rekam menempati dua halaman dalam satu blok, tetapi hanya satu yang benar-benar gratis: meskipun halaman lama (disorot dengan warna kuning) telah dihapus oleh pengguna sebelumnya, pada kenyataannya, informasi yang direkam tidak hilang. Untuk membersihkan ruang untuk data baru, pengontrol memulai prosedur yang dikenal sebagai pengumpulan sampah, menghapus data yang tidak perlu dan mendistribusikan kembali yang sudah ada. Untuk melakukan ini, semua halaman, kecuali yang tidak perlu, disalin ke blok kedua, gratis, sementara yang pertama dihapus sepenuhnya. Kemudian halaman yang sebenarnya ditransfer kembali ke blok pertama, dihapus dari blok kedua, dan hanya setelah itu data baru mengambil tempat yang selayaknya.

Pada contoh di atas, untuk merekam dua halaman, kami harus menulis ulang 2 blok dua kali, masing-masing enam halaman. Bahkan, proses "Pengumpulan Sampah" akan terlihat jauh lebih rumit dan, sebagai akibatnya, jumlah siklus penulisan ulang akan jauh lebih besar. Gambaran nyata hanya dapat diperkirakan dengan mengetahui koefisien Amplifikasi Tulis, yang menunjukkan berapa kali beban aktual pada memori flash melebihi yang dihitung. Indikator ini dapat sama dengan kesatuan hanya ketika merekam informasi pada disk yang benar-benar bersih, hanya diformat, dalam semua kasus nilainya akan bervariasi dari 2 hingga 25. Selain itu, bahkan pada pandangan pertama, drive yang identik dapat berbeda secara signifikan, jadi tergantung pada model pengontrol yang digunakan dan fitur-fitur firmware. Dengan demikian, toleransi kesalahan SSD ditentukan tidak hanya oleh jenis memori flash, tetapi juga oleh seberapa banyak pengembang dapat mengoptimalkan kinerja lapisan FTL (Flash Translation Layer).

Mengapa peningkatan dramatis dalam kepadatan penyimpanan tidak memengaruhi keandalan memori NAND 3D?

Jadi, sekarang kita tahu bagaimana memori flash bekerja dan faktor apa yang menentukan keandalan drive SSD. Sudah waktunya untuk mencari tahu apa manfaat transisi dari chip "flat" ke yang tiga dimensi yang disediakan. Pertama-tama, 3D NAND berbeda dari pendahulunya karena penggunaan "perangkap biaya" (Charge Trap Flash) alih-alih jendela mengambang yang sudah dikenal. Jika dalam yang terakhir, polisilikon dengan dopan digunakan untuk menyimpan muatan, maka dalam CTF merupakan daerah terisolasi dari bahan non-konduktif, paling sering SiN - silikon nitrida. Pendekatan seperti itu memungkinkan untuk meminimalkan kemungkinan kebocoran muatan dan, sebagai hasilnya, meningkatkan stabilitas sel.

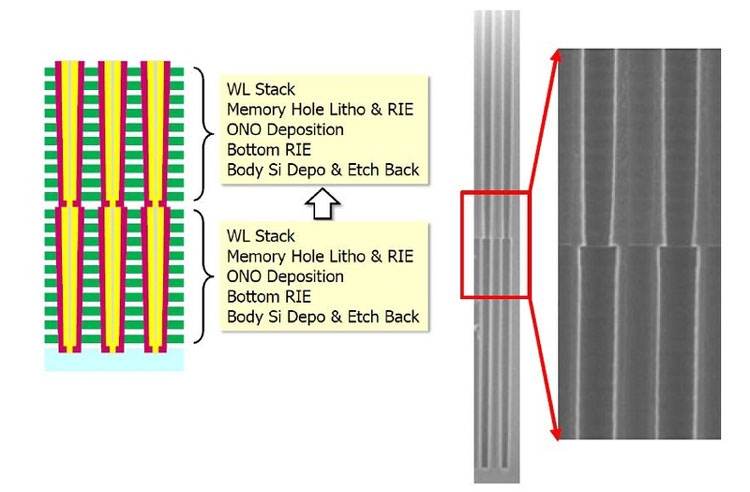

Arsitektur chip memori tiga dimensi juga telah mengalami perubahan signifikan dibandingkan pendahulunya, karena sekarang setiap sel memiliki struktur silindris: lapisan luar adalah gerbang kontrol, dan bagian dalam adalah isolator. Karena sel-sel sekarang terletak satu di atas yang lain, mereka membentuk tumpukan, di dalamnya melewati saluran yang terbuat dari silikon polikristalin. Sangat mudah untuk memahami bahwa jumlah lapisan dalam sebuah chip menentukan jumlah sel dalam tumpukan.

Perangkat sel chip NAND 3DStruktur ini memungkinkan untuk mengurangi gangguan antar sel dan dengan demikian menyederhanakan algoritma perekaman: karena tidak perlu memeriksa keadaan pengisian, perekaman dalam sel dimulai dalam satu langkah. Nuansa penting lainnya: untuk produksi 3D NAND, proses run-in digunakan, meskipun faktanya kepadatan pengepakan sel mampu meningkat secara signifikan. Jadi, misalnya, bahkan chip 48-layer (generasi ketiga dari memori flash tiga dimensi) diproduksi menggunakan teknologi proses 40-nanometer. Hal ini memungkinkan tidak hanya untuk meningkatkan keandalannya, tetapi juga untuk mengurangi biaya produksi, karena jalur produksi yang ada hanya membutuhkan modernisasi minimal, dan kebutuhan litografi dalam ultraviolet yang mendalam sepenuhnya menghilang.

Berbicara secara khusus tentang produk-produk Western Digital, kemudian di

WD NV SN750 NVMe SSDs modern , dimulainya penjualan yang dimulai pada 18 Januari 2019, TLC 3D NAND BiCS 64-layer (Bit Cost Scalable), dibuat menggunakan teknologi proses 28-nanometer, digunakan. Selain meningkatkan kerapatan pengepakan sebanyak 1,4 kali (model teratas sekarang memiliki kapasitas 2 TB, yang dua kali ukuran andalan generasi sebelumnya), fitur penting dari chip jenis ini adalah penggunaan string berbentuk U.

Arsitektur 3D NAND BiCSKarena sekarang transistor switching dan jalur sumber terletak di bagian atas chip, mereka praktis tidak terkena pengaruh suhu tinggi, yang dengan sendirinya dapat menyebabkan kesalahan selama operasi baca / tulis, yang selanjutnya meningkatkan keandalan drive solid-state.

Bagaimana algoritme perekaman memengaruhi kehidupan SSD?

Kami sudah menulis di atas bahwa tidak peduli seberapa kuat dan amannya memori flash itu sendiri, sumber dayanya akan terbuang sia-sia jika pengembang SSD tidak repot-repot membuat algoritma perekaman yang efektif. Untuk mengoptimalkan prosedur ini, dua teknik yang sangat efektif digunakan: SLC caching dan Wear Leveling.

Inti dari yang pertama adalah bagian dari array memori yang tersedia, yang ukurannya tergantung pada total volume drive (misalnya, ketika mengembangkan

WD Blue 3D NAND SSD, kami melanjutkan dari perhitungan cache 4 GB untuk setiap kapasitas 250 GB) ditransfer ke mode operasi SLC, mis. , hanya satu bit informasi dicatat di setiap sel, yang memungkinkan keduanya untuk secara signifikan meningkatkan kinerjanya dan mengurangi tingkat keausan. SLC terlibat dalam perekaman dan konsolidasi data yang disimpan pada SSD, yang memungkinkan tidak hanya untuk meningkatkan kecepatan operasi, tetapi juga untuk mengurangi tingkat keausan sel. Dalam versi Western Digital SSD saat ini, teknologi nCache 3.0 digunakan, versi terbaru yang telah memperoleh fungsi direct-to-TLC, yang memungkinkan untuk menemukan keseimbangan antara caching dan kecepatan: data ditulis melewati cache saat penuh atau saat menggunakan SLC- penyangga tidak praktis. Ini, di satu sisi, membantu membongkar cache, dan pada saat yang sama untuk menghindari penurunan kinerja yang dramatis ketika mengisinya.

Dinamika kecepatan tulis pada SSD saat mengisi SLC-bufferSedangkan untuk teknologi keausan leveling, ada baiknya untuk memastikan bahwa semua blok halaman yang tersedia digunakan serata mungkin. Seperti yang Anda ketahui, sistem operasi apa pun menggunakan mekanisme logis untuk mengatasi blok data (LBA), sementara pengontrol itu sendiri beroperasi dengan alamat fisik (PBA), menghubungkannya dengan yang logis. Sebagai hasil dari ini, tidak masalah di mana fragmen file sebenarnya berada, karena itu dimungkinkan untuk menulis program mikro yang akan memastikan bahwa beban antar sel didistribusikan secara merata.

Leveling aus memastikan beban seragam pada selSecara umum, algoritmanya adalah sebagai berikut. Anda membeli SSD baru dan meskipun ada ruang kosong di sana, informasi akan dicatat dalam blok gratis. Ketika Anda beroperasi, Anda mulai menghapus file yang tidak perlu, dan mekanisme pengumpulan sampah membersihkannya di latar belakang, namun, mereka akan digunakan untuk merekam hanya setelah tidak ada satu blok tersisa di disk yang datanya tidak akan ditulis setidaknya satu kali. Tentu saja, dalam kenyataannya, semuanya jauh lebih rumit, tetapi artinya tidak berubah.

Dan di sini satu lagi catatan penting harus dibuat mengenai produk Western Digital. Ketika kami memutuskan untuk mengembangkan pasar SSD, kami dapat melakukan dua cara: membeli memori dan pengontrol dari produsen pihak ketiga, hanya berfokus pada pengembangan dan optimalisasi firmware, atau menyiapkan produksi siklus penuh. Menjalankan proyek semacam itu dari nol akan menjadi tidak praktis, dan bahkan

pembelian SanDisk telah menelan biaya yang sangat besar. Tetapi dana yang diinvestasikan mengalahkan sepenuhnya: mengendalikan produksi chip, kami mendapat kesempatan untuk menyesuaikan mikroprogram dengan fitur-fitur sirkuit mikro.

Harus dipahami bahwa menulis bit informasi ke dalam sel memori flash adalah proses yang jauh lebih rumit daripada yang terlihat pada pandangan pertama: itu memperhitungkan ratusan parameter yang berbeda, yang paling penting adalah tegangan yang diperlukan untuk transfer biaya dan waktu perekaman. Saat chip aus, karakteristik fisiknya juga berubah: untuk perekaman data yang sukses, lebih sedikit tegangan yang diperlukan, dan pada saat yang sama, waktu yang diperlukan pengaruhnya pada sel berkurang. Di sebagian besar SSD, parameter ini konstan, tetapi di Western Digital SSD, sebaliknya, mereka berubah secara dinamis ketika sel memakai, yang memungkinkan untuk memaksimalkan umur masing-masing, meminimalkan dampak negatif pada struktur semikonduktor.

QLC 3D NAND - memori flash generasi terbaru

Jika Anda mengikuti berita dari dunia teknologi tinggi, Anda mungkin menyadari bahwa Western Digital secara aktif menguasai produksi memori tiga dimensi generasi berikutnya - QLC 3D NAND (pengumuman pertama terjadi pada Juni 2018). Akronim QLC adalah singkatan dari sel quad-level. Dengan kata lain, 16 level pengisian daya dapat disimpan dalam satu sel, penyandian tidak hanya tiga, tetapi empat bit informasi. Dibandingkan dengan TLC 3D NAND, kepadatan perekaman di QLC meningkat sebesar 33%: dengan demikian, kapasitas satu chip 64-layer meningkat menjadi 768 Gbps. Tapi ini bukan batasnya: pada bulan Agustus 2018 kami memulai pelepasan microcircuits 96-layer. Dengan meningkatkan jumlah lapisan, kami dapat memperoleh peningkatan kapasitas 50 persen dan mengatasi penghalang 1 Tbit: chip baru, yang disebut 3D NAND BiCS4, dapat menampung informasi 1,33 Tbit, yaitu sekitar 166 GB. Itu mungkin untuk mencapai kepadatan penyimpanan data yang begitu tinggi dengan menggabungkan dua kristal 48-lapisan (hari ini ini adalah pendekatan yang paling ekonomis).

Peningkatan kapasitas berpotensi mengurangi kinerja SSD, tetapi Anda tidak perlu khawatir tentang ini: memori flash 3D NAND BiCS4 baru menggunakan empat bukannya dua array fisik, yang memungkinkan untuk mengoptimalkan membaca dan menulis data dengan memparalelkan operasi, dan ini, pada gilirannya, Ini akan membantu untuk lebih efisien menggunakan cache dan mengontrol tingkat keausan sel, sambil mempertahankan kehidupan kerja chip-QLC pada tingkat yang sebanding dengan solusi-TLC modern. Namun, deskripsi teknologi yang mendasari QLC berada di luar cakupan materi ini dan tentu saja layak untuk artikel terpisah.