Kami terus mempertimbangkan UDB berdasarkan dokumentasi kepemilikan Cypress, yaitu hal-hal sepele yang berguna terkait dengan Datapath.

Isi umum dari siklus “UDB. Apa ini? "

Bagian 1. Pendahuluan. Pld.Bagian 2. Datapath.Bagian 3. Datapath FIFO.Bagian 4. Datapath ALU.Bagian 5. Datapath. Hal-hal kecil yang bermanfaat. (Artikel saat ini)

Bagian 6. Modul manajemen dan status.Bagian 7. Pengaturan waktu dan reset modul kontrolBagian 8. Mengatasi UDB21.3.2.6 Dukungan CRC / PRS

Datapath mendukung generasi Cyclic Redundancy Checking (CRC) dan sekuens pseudo-acak (Pseudo Random Sequence, PRS). Sinyal dirantai dilacak antara blok Datapath untuk mendukung CRC / PRS lebih dari 8 bit.

Jumlah bit paling signifikan (MSB) dari blok CRC / PRS tertinggi dipilih dan dilacak (dan dirantai ke blok lain) ke blok yang lebih rendah. Setelah itu, operasi XOR dengan data input (data SI) diterapkan ke MSB, memberikan sinyal umpan balik (umpan balik, FB). Setelah itu, sinyal umpan balik dilacak (dan dihubungkan dalam rantai dengan blok lain) ke blok yang lebih rendah. Nilai umpan balik ini digunakan pada semua blok untuk melakukan operasi

XOR polinomial (dari data0 atau data1 register) dengan nilai baterai saat ini.

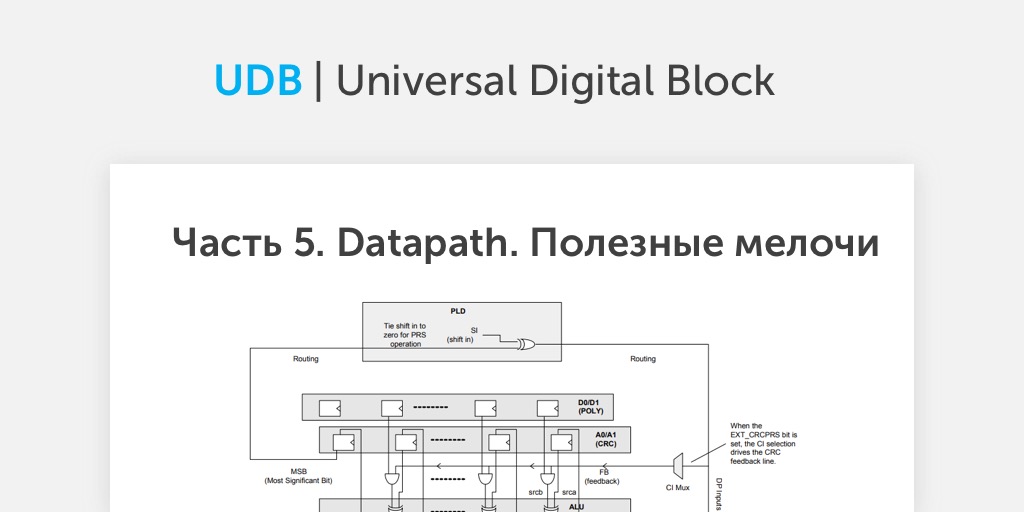

Gambar 21-18 menunjukkan konfigurasi struktural operasi CRC. Konfigurasi PRS identik, tetapi input shift (SI) ditarik ke 0. Dalam mode PRS, D0 atau D1 berisi nilai polinomial, dan A0 atau A1 berisi nilai awal (seed) dan nilai CRC yang diperoleh setelah perhitungan.

Catatan oleh penerjemah.Rupanya, ada kesalahan ketik dalam dokumentasi milik dalam kalimat ini, karena nomor acak harus diperoleh dalam mode PRS. Dan informasi tentang CRC terletak tepat di bawah. Gambar 21-18. Struktur fungsional CRC.

Gambar 21-18. Struktur fungsional CRC.Untuk mengaktifkan dukungan CRC, Anda harus mengatur bit

CFB_EN dalam konfigurasi dinamis RAM ke 1. Ini mengaktifkan operasi

DAN sehubungan dengan input ALU SRCB dan sinyal umpan balik CRC. Jika bit ini diatur ke nol, sinyal umpan balik akan ditetapkan ke satu, yang memungkinkan operasi aritmatika normal dilakukan. Kontrol dinamis bit ini pada setiap siklus memungkinkan Anda untuk bergantian operasi CRC / PRS dengan operasi aritmatika lainnya.

Rantai CRC / PRS

Gambar 21-19 menunjukkan contoh pengikatan CRC / PRS dalam rantai di antara tiga UDB. Skenario ini mendukung operasi dalam mode dengan resolusi 17 hingga 24 bit. Bit pengikat kontrol dalam rantai diatur sesuai dengan posisi Datapath dalam rantai (lihat gambar).

Gambar 21-19. Ikatan rantai CRC / PRS.

Gambar 21-19. Ikatan rantai CRC / PRS.Bagaimana sinyal umpan balik CRC / PRS (cfbo, cfbi) terhubung dalam sebuah rantai:

- Jika blok yang dipilih adalah yang termuda, sinyal umpan balik pada blok ini dihasilkan dari logika bawaan, yang mengambil input shift ke kanan (sir) dan melakukan operasi XOR pada mereka dengan bit yang paling signifikan. (Dalam hal PRS, sinyal "sir" diatur ke "0").

- Jika blok yang dipilih bukan blok urutan rendah, bit konfigurasi CHAIN FB harus dikokang, dan umpan balik dikirim dalam rantai dari blok sebelumnya.

Bagaimana rantai sinyal CRC / PRS MSB (cmsbo, cmsbi):

- Jika blok yang dipilih tinggi, bit konfigurasi MSB (sesuai dengan polinomial yang dipilih) dikonfigurasi menggunakan bit konfigurasi MSB_SEL .

- Jika blok yang dipilih tidak tinggi, bit konfigurasi CHAIN MSB harus dikokang, dan sinyal MSB akan dikirim sepanjang rantai dari blok berikutnya.

Spesifikasi Polinomial CRC / PRS

Sebagai contoh konfigurasi polinomial untuk menulis ke register yang sesuai D0 / D1, pertimbangkan polinomial

CCITT CRC-16 , yang memiliki bentuk x

16 + x

12 + x

5 + 1. Metode untuk mengekstraksi format data dari polinomial ditunjukkan pada Gambar 21-20. Istilah X0, menurut definisi, selalu 1, oleh karena itu, tidak perlu ditulis. Untuk semua anggota polinomial lain, unit diatur ke posisi yang diperlukan, seperti yang ditunjukkan pada gambar.

Gambar 21-20. Format polinomial CCITT CRC16.

Gambar 21-20. Format polinomial CCITT CRC16.Harap dicatat bahwa format polinomial sedikit berbeda dari format yang ditentukan dalam format heksadesimal klasik. Misalnya, polinomial

CRC16 CCITT biasanya disebut sebagai

1021H . Untuk mengonversinya ke format yang diperlukan untuk Datapath, Anda perlu menggeser ke kanan dengan satu posisi dan menambahkan 1 ke bit MSB. Dalam hal ini, nilai polinom yang benar untuk ditulis dalam D0 atau dalam D1 adalah

8810H .

Contoh Konfigurasi CRC / PRS

Berikut ini adalah penjelasan singkat tentang persyaratan konfigurasi CRC / PRS, asalkan D0 adalah polinomial dan CRC / PRS dihitung dalam A0:

- Pilih polinomial yang sesuai (contoh di atas), dan tulis ke D0.

- Pilih nilai seed yang cocok (misalnya, semua nol untuk CRC atau semua untuk PRS) dan tulis ke A0.

- Jika perlu, konfigurasikan rangkaian seperti dijelaskan di atas.

- Pilih item MSB seperti dijelaskan di atas.

- Konfigurasikan bidang RAM RAM dinamis:

a. Pilih D0 sebagai ALU "SRCB" (sumber data ALU B)

b. Pilih A0 sebagai ALU “SRCA” (ALU A sumber data)

c. Pilih

XOR untuk operasi ALU

d. Pilih

SHIFT LEFT untuk operasi SHIFT

e. Pilih

CFB_EN untuk mengaktifkan dukungan CRC / PRS.

f. Pilih ALU sebagai Sumber Rekam A0

Saat memilih CRC, Anda harus mengonfigurasi

pergeseran di bidang yang

benar untuk data input dan mengirimkan data pada input ini di setiap langkah. Saat memilih PRS, Anda harus mengatur

shift ke

kanan ke 0.

Konfigurasi UDB ini menghasilkan CRC yang diperlukan atau menghasilkan bit paling signifikan, yang dapat diteruskan ke luar, menghapus darinya urutan pseudo-acak.

Mode eksternal CRC / PRS

Untuk mengaktifkan komputasi CRC atau PRS eksternal, Anda dapat menentukan bit konfigurasi statis (

EXT CRCPRS ). Seperti yang ditunjukkan pada Gambar 21-21, perhitungan umpan balik CRC dilakukan di blok PLD. Ketika bit dikokang, sinyal umpan balik CRC ditransmisikan langsung dari input multiplexer CI (Carry In), melewati perhitungan internal. Gambar tersebut menunjukkan konfigurasi sederhana yang mendukung CRC atau PRS hingga 8-bit. Biasanya, sirkuit elektronik built-in digunakan, tetapi parameter ini memungkinkan Anda untuk mengimplementasikan konfigurasi yang lebih kompleks, misalnya, fungsi CRC / PRS 16-bit dalam satu UDB, menggunakan multiplexing pembagian waktu.

Gambar 21-21. Mode eksternal CRC / PRS.

Gambar 21-21. Mode eksternal CRC / PRS.Dalam mode ini, bit

CFB_EN dari RAM konfigurasi dinamis juga mengontrol apakah operasi

AND digunakan pada sinyal umpan balik CRC pada input ALU CRCB atau tidak. Jadi, seperti dalam kasus mode CRC / PRS internal, fungsi ini dapat, jika perlu, bergantian dengan fungsi lain.

21.3.2.7 Output data dan multiplexing

Kondisi dihasilkan dari nilai pemicu baterai, output ALU, dan status FIFO. Kondisi ini dapat ditransmisikan melalui saluran pelacakan digital ke UDB lain untuk membentuk permintaan interupsi baik ke DMA atau ke "kaki chip". 16 kondisi yang mungkin ditunjukkan pada tabel di bawah ini.

Tabel 21-16. Generasi kondisi datapath.

Ada enam jalan keluar dari Datapath. Seperti yang ditunjukkan pada Gambar 21-22, setiap output memiliki multiplexer 16 in 1 yang memungkinkan Anda untuk merutekan salah satu dari 16 sinyal ke output Datapath apa pun.

Gambar 21-22. Koneksi ke multiplexer keluaran.

Gambar 21-22. Koneksi ke multiplexer keluaran.Perbandingan

Ada dua perbandingan, yang satu memiliki sumber tetap (

Bandingkan 0 ), dan yang lainnya dipilih secara dinamis (

Bandingkan 1 ). Setiap perbandingan memiliki register masking statis 8-bit, yang memungkinkan perbandingan dalam bidang bit yang ditentukan. Secara default, masking dinonaktifkan (semua bit dibandingkan) dan harus diaktifkan secara manual.

Bandingkan 1 input yang dikonfigurasi secara dinamis. Seperti yang ditunjukkan pada tabel di bawah, ada empat Bandingkan 1 parameter yang berlaku untuk kondisi kurang dan sama.

Bit konfigurasi

CMP SELA dan

CMP SELB menentukan konfigurasi perbandingan yang mungkin. Bit RAM dari konfigurasi dinamis menentukan salah satu konfigurasi (A atau B) pada setiap siklus.

Tabel 21-17. Konfigurasi Perbandingan.

Bandingkan 0 dan

Bandingkan 1 dikaitkan dengan kondisi yang dihasilkan dalam Datapath sebelumnya secara independen (dalam urutan perawatan). Apakah atau tidak untuk perbandingan rantai ditentukan secara statis dalam register konfigurasi UDB. Gambar 21-23 menunjukkan menghubungkan "sama" dengan rantai perbandingan, yang mengurangi untuk menerapkan operasi

DAN untuk perbandingan "sama" dari blok ini dan ke input dari blok sebelumnya.

Gambar 21-23. Menautkan ke rantai perbandingan adalah "sama."

Gambar 21-23. Menautkan ke rantai perbandingan adalah "sama."Gambar 21-24 menunjukkan menghubungkan ke rantai perbandingan kurang. Dalam hal ini, hasil keluaran (cl0) untuk blok yang diberikan dihasilkan oleh rangkaian perbandingan "kurang dari" dan tidak bersyarat. Sinyal ini digabungkan

ATAU dengan hasil yang masuk dari rantai jika kondisinya sama dengan blok saat ini dan mode penghubung dihidupkan.

Gambar 21-24. Tautan kurang dari

Gambar 21-24. Tautan kurang dariDeteksi semua nol dan semua yang ada

Setiap baterai memiliki detektor semua nol dan detektor semua unit. Kondisi ini dapat dirantai secara statis seperti ditunjukkan dalam register konfigurasi UDB. Mode penjilidan diatur dalam register konfigurasi UDB. Menghubungkan dalam rantai deteksi nol terjadi sesuai dengan konsep yang sama dengan perbandingan "sama dengan". Jika rantai diaktifkan,

DAN operasi diterapkan untuk data yang berhasil ditautkan.

Overflow

Overflow didefinisikan sebagai operasi transfer

XOR dalam MSB dan transfer dari MSB. Perhitungan dilakukan dengan MSB saat ini, seperti yang ditunjukkan dalam bit

MSB_SEL . Kondisi ini tidak dapat dirantai, namun, perhitungan akan benar jika fungsi kapasitas total dilakukan pada Datapath yang lebih lama sampai transfer antar blok terhubung.

21.3.2.8 Input dan Output Paralel Datapath

Seperti ditunjukkan pada Gambar 21-25, sinyal

Parallel In (PI) dan

Parallel Out (PO) menyediakan kemampuan terbatas untuk mengirimkan data dan melacak sumber daya ke Datapath dan mengeluarkan data dari data tersebut. Sinyal PO selalu tersedia untuk ditelusuri sebagai pilihan ALU asrc antara A0 dan A1.

Catatan oleh penerjemah.Ini adalah mekanisme yang sangat penting yang memungkinkan UDB untuk bekerja tidak hanya dengan serial, tetapi juga dengan data paralel. Untuk beberapa alasan, dokumen ini tidak menekankan ini, tetapi Anda dapat membacanya di dalam salah satu Catatan Aplikasi. Gambar 21-25. Sinyal Datapath Masuk / Keluar Paralel.

Gambar 21-25. Sinyal Datapath Masuk / Keluar Paralel.Untuk memasukkan data ke dalam ALU, Anda harus memilih

Parallel In . Ada dua mode: statis dan dinamis. Dalam mode statis, bit

PI SEL mengonversi nilai ALrc asrc ke PI. Bit

PI DYN digunakan untuk menyediakan mode dinamis PI. Ketika dimiringkan, dan juga asalkan

PI SEL adalah 0, multiplexer PI dapat mengontrol bit kontrol dinamis

CFB_EN . Fungsi utama bit

CFB_EN adalah untuk menyediakan fungsionalitas PRS / CRC.

21.3.2.9 Chaining Datapath

Setiap blok Datapath memiliki ALU 8-bit, yang dirancang untuk menghubungkan tanda hubung, shift, trigger trigger, dan sinyal bersyarat ke Datapath terdekat untuk menciptakan fungsi aritmatika dan menggeser register dengan kedalaman bit yang lebih tinggi. Sinyal-sinyal ini, terhubung dengan rantai, terisolasi dan memungkinkan Anda untuk secara efektif mengimplementasikan fungsi 16-24-dan 32-bit dalam satu siklus tanpa balapan dan masalah lain yang timbul dari keterlambatan saluran jejak. Selain itu, pegangan rantai mendukung pembacaan atom baterai di blok yang terhubung. Seperti yang ditunjukkan pada Gambar 21-21, semua sinyal kondisional dan menangkap yang dihasilkan terhubung dalam rantai yang bergerak dari yang termuda ke blok tertua. Pergeseran ke kiri juga dilakukan dari junior ke senior. Pergeseran ke kanan dilakukan dari yang tertua ke yang termuda. Sinyal rantai CRC / PRS untuk umpan balik dialihkan dari tinggi ke rendah, dan output MSB dikirim dari tinggi ke rendah.

Gambar 21-26. Rantai threading datapath.

Gambar 21-26. Rantai threading datapath.21.3.2.10 Konfigurasi dinamis RAM

Setiap Datapath berisi konfigurasi RAM dinamis dengan 8 kata masing-masing 16 bit (lihat Gambar 21-27). Tujuan dari RAM tersebut adalah untuk mengontrol bit-bit konfigurasi Datapath pada setiap siklus, berdasarkan jam yang dipilih untuk Datapath ini. RAM memiliki port baca dan tulis yang sinkron untuk mengunduh konfigurasi melalui bus sistem.

Untuk dengan cepat menampilkan kata-kata 16-bit ini ke Datapath, port baca asinkron tambahan disediakan sebagai bit kontrol. Input alamat asinkron dipilih oleh multiplexer dari input Datapath, yang dapat diambil dari setiap sinyal yang mungkin, termasuk kaki sirkuit mikro, output PLD, output unit kontrol, atau output Datapath apa pun.

Tujuan utama dari port baca asinkron adalah untuk memberikan decoding cepat bit kontrol Datapath dalam satu siklus tunggal.

Gambar 21-27. Konfigurasi RAM I / O.

Gambar 21-27. Konfigurasi RAM I / O.Bidang kata RAM dari konfigurasi dinamis ditampilkan dalam tabel berikut bersama dengan deskripsi penggunaan setiap bidang.

Tabel 21-18. Referensi konfigurasi dinamis.

(a. - Untuk bidang CI, SI, dan CMP, bidang RAM memungkinkan Anda untuk memilih satu dari dua opsi yang telah ditentukan. Lihat konfigurasi register statis).

Dilanjutkan ...