Teknologi FPGA (FPGA) saat ini mulai populer. Jumlah aplikasi meningkat: selain memproses sinyal digital, FPGA juga digunakan untuk mempercepat pembelajaran mesin, dalam teknologi blockchain, pemrosesan video dan dalam IoT.

Teknologi ini memiliki satu minus signifikan: untuk pemrograman, bahasa deskripsi yang cukup kompleks dan spesifik dari peralatan digital Verilog dan VHDL digunakan. Ini mempersulit masuknya pendatang baru ke dalam FPGA dan sulit bagi pemberi kerja untuk menemukan spesialis dengan pengetahuan khusus ini di pasar tenaga kerja. Di sisi lain, bahasa pemrograman Python tingkat tinggi yang populer dengan kerangka

MyHDL membuat pemrograman FPGA sederhana dan menyenangkan. Selain itu, orang yang tahu Python adalah urutan lebih banyak spesialis dengan Verilog / VHDL. Dengan serangkaian artikel saya ingin menunjukkan betapa mudahnya untuk memasuki bidang FPGA mengetahui Python dan mulai membuat proyek FPGA yang sangat kompleks dalam bahasa ini. Saya perhatikan bahwa python tidak langsung dieksekusi pada FPGA, tetapi merupakan alat untuk menghasilkan firmware.

Pertama, kita membutuhkan python versi 3.6 itu sendiri (selanjutnya, semua operasi dilakukan pada OS Ubuntu 18.04).

Instal myhdl:

pip3 install myhdl

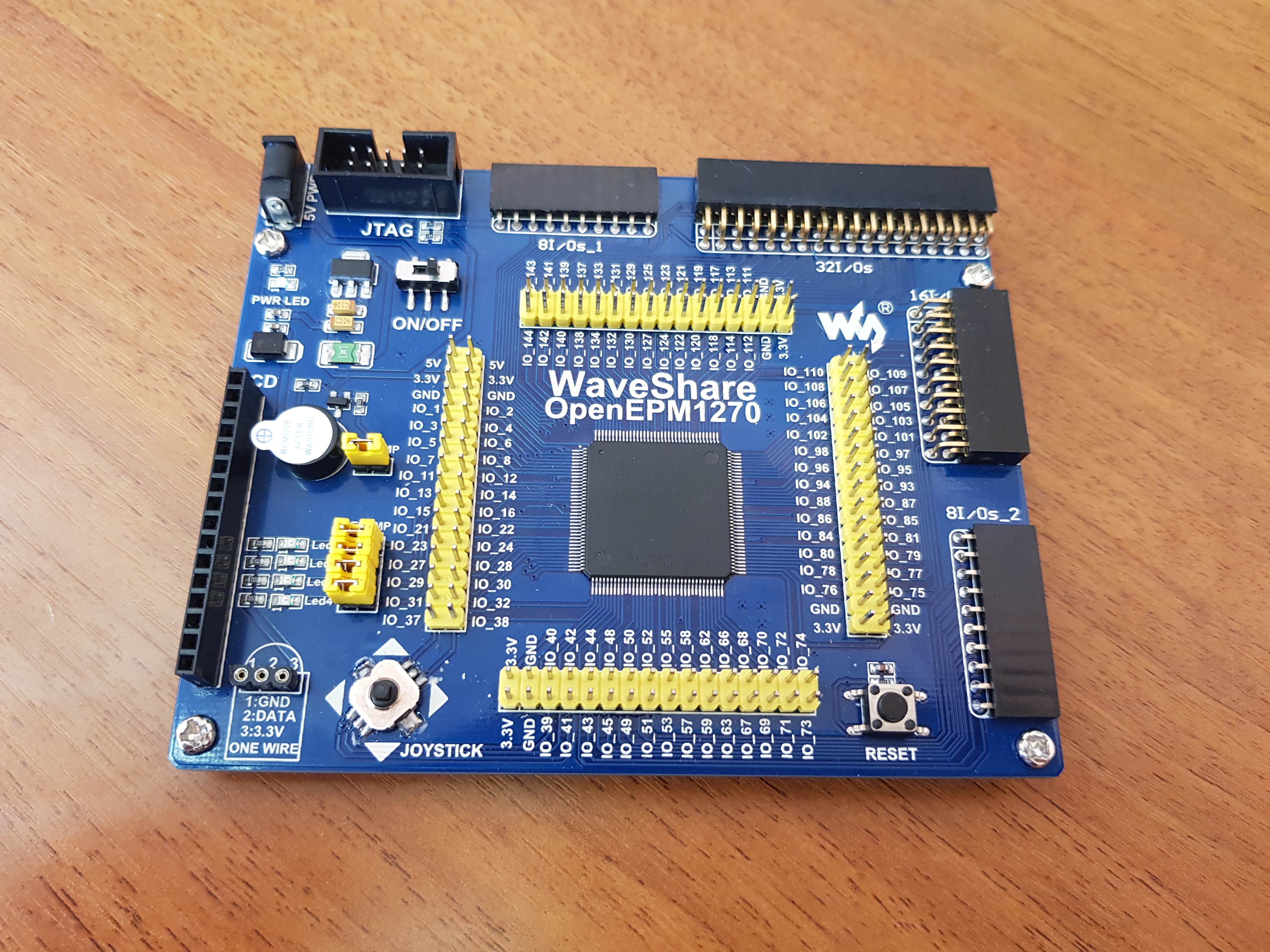

Sebagai "Hello World!" Kami akan menulis program sederhana yang membuat LED menyala ketika tombol ditekan. Di dunia mikroprosesor "Hello World!" Ini adalah program yang berkedip dengan satu LED, di dunia FPGA, Hello World adalah flashing dari seribu LED. Hanya ada empat LED di papan tulis, jadi kami hanya akan mem-flashnya, tergantung pada tombol yang ditekan. Penting untuk dicatat bahwa semua kode dalam FPGA, tidak seperti mikrokontroler, dieksekusi pada saat yang sama, semua dioda menyala dan keluar pada saat yang sama. Dan tidak berurutan dalam kasus mikrokontroler. Tes ini menggunakan papan WaveShare OpenEPM1270 dengan papan Altera Max II EPM1270T144C5 di papan tulis.

Buat file python baru:

from myhdl import * from random import randrange def led_blinker(input1, led1, led2, led3, led4): @always_comb def on_off_led(): if input1 == 1: led1.next = 1 led2.next = 1 led3.next = 0 led4.next = 0 else: led1.next = 0 led2.next = 0 led3.next = 1 led4.next = 1 return on_off_led

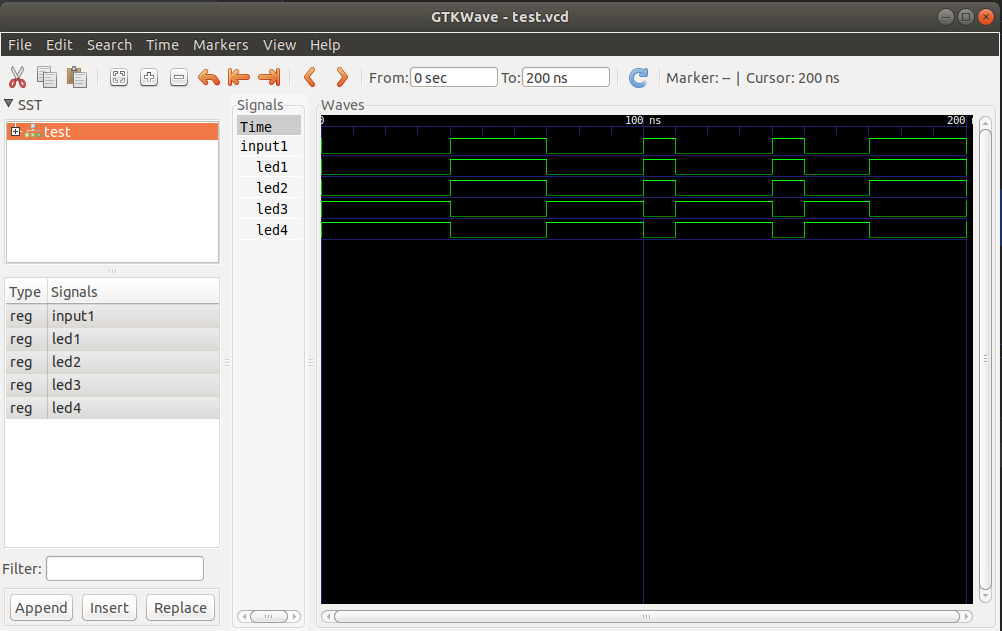

Untuk mengetahui apakah kode kami berfungsi dengan benar, Anda memerlukan alat verifikasi. Faktanya, setiap program untuk FPGA adalah prosesor sinyal digital, sehingga pengembang perlu memastikan bahwa ia menunjukkan dengan benar apa yang harus dilakukan dengan chip tersebut. Ini dilakukan melalui simulasi, untuk ini Anda perlu menginstal program yang akan menampilkan sinyal yang diproses. Ada banyak program seperti itu, tetapi menurut saya GTKWave gratis terbaik saat ini. Itu dimasukkan dari terminal:

sudo apt-get install gtkwave

Selanjutnya, dalam file dengan firmware, lingkungan pengujian harus dijelaskan. Ini juga merupakan fungsi python:

def test(): input1, led1, led2, led3, led4 = [Signal(bool(0)) for i in range(5)] test = led_blinker(input1, led1, led2, led3, led4) @always(delay(10)) def gen(): input1.next = randrange(2) return test, gen

Di sini lingkungan pengujian menghasilkan urutan nol dan acak (modul Python acak digunakan).

def simulate(timesteps): tb = traceSignals(test) sim = Simulation(tb) sim.run(timesteps)

Dan kami menginisialisasi simulator, menyeret fungsi lingkungan test_inverter di sana. Dengan demikian, kita mendapatkan simulasi boneka Rusia → test_inverter → mensimulasikan (waktu dalam unit sewenang-wenang).

Setelah menjalankan skrip di folder yang berfungsi, buat file .vcd dan jalankan melalui gtkwave, di terminal: gtkwave test_invereter.vcd.

Akibatnya, urutan acak dari sinyal input input1 dihasilkan, dan bagaimana fungsi led_blinker memproses sinyal-sinyal ini.

Setelah kami memastikan bahwa logika bekerja persis seperti yang kami inginkan, maka kami harus membuang fungsi ini ke FPGA. Saya sudah terbiasa bekerja dengan chip dari Intel (sebelumnya Altera), urutan operasi ini serupa untuk chip dari produsen lain dengan sistem CAD yang sesuai. File biner dibuat pada chip FPGA, yang dibuat oleh kompiler dari pembuat chip, untuk Intel itu adalah Quartus, untuk Xilinx Vivado. Kompiler hanya dapat bekerja dengan kode dalam VHDL / Verilog, sehingga kode Python harus diterjemahkan ke dalam salah satu bahasa ini (tidak masalah yang mana).

def convert(): input1, led1, led2, led3, led4 = [Signal(bool(0)) for i in range(5)] toVerilog(led_blinker, input1, led1, led2, led3, led4) convert()

Dalam contoh ini, kode tersebut diterjemahkan ke dalam Verilog. Hasilnya ada dalam file led_blinker.v, dan Quartus harus memberikannya untuk menghasilkan firmware FPGA:

module led_blinker ( input1, led1, led2, led3, led4 ); input input1; output led1; reg led1; output led2; reg led2; output led3; reg led3; output led4; reg led4; always @(input1) begin: LED_BLINKER_ON_OFF_LED if ((input1 == 1)) begin led1 = 1; led2 = 1; led3 = 0; led4 = 0; end else begin led1 = 0; led2 = 0; led3 = 1; led4 = 1; end end endmodule

Dalam pendekatan ini untuk pengembangan firmware FPGA, Anda dapat mengabaikan file ini dan cukup memasukkannya ke Quartus.

Anda dapat mengunduh Quartus dari

fpgasoftware.intel.com , kami memerlukan versi Lite gratis, itu sudah cukup bagi kami. Unduh versi dasar ukuran 9 GB.

Menginstal Quartus seharusnya tidak menjadi masalah bagi rata-rata pengguna Linux. Setelah instalasi, Anda perlu mengatur beberapa parameter dalam sistem sehingga Anda dapat menggunakan perangkat untuk menginstal program FPGA - pemrogram:

1. Buat aturan udev. Untuk melakukan ini, buat file baru /etc/udev/rules.d/51-altera-usb-blaster.rules dengan konten berikut:

Mulai ulang udev menggunakan udevadm:

sudo udevadm control --reload

2. Izinkan akses non-root ke perangkat USB-Blaster. Untuk melakukan ini, buat file /etc/udev/rules.d/altera-usb-blaster.rules dengan baris:

ATTR{idVendor}=="09fb", ATTR{idProduct}=="6001", MODE="666"

Ini memberikan rw-rw-rw- akses ke programmer.

3. Konfigurasikan jtagd. Quartus menggunakan daemon jtagd untuk bekerja, yang mengaitkan perangkat lunak dengan perangkat programmer. Salin deskripsi dari direktori Anda dengan Quartus:

sudo mkdir /etc/jtagd sudo cp <Quartus install path>/quartus/linux64/pgm_parts.txt /etc/jtagd/jtagd.pgm_parts

Jalankan Quartus dan buat "File" proyek baru - "Wizard proyek baru", ketikkan nama proyek.

Selanjutnya, klik Selanjutnya. Dan di menu Add Files, kami menghubungkan file Verilog yang dihasilkan dengan ekstensi .v. Jadi, jika file Verilog diedit dari file python, maka akan secara otomatis diambil oleh Quartus. Selanjutnya, kita masuk ke menu pemilihan perangkat, dalam kasus kami adalah MAX II EMP1270T144C5 dan beberapa kali berikutnya. Proyek ini dibuat.

Di Project Navigator, buka menu file dan klik kanan pada file Verilog kami "Tetapkan sebagai entitas tingkat atas".

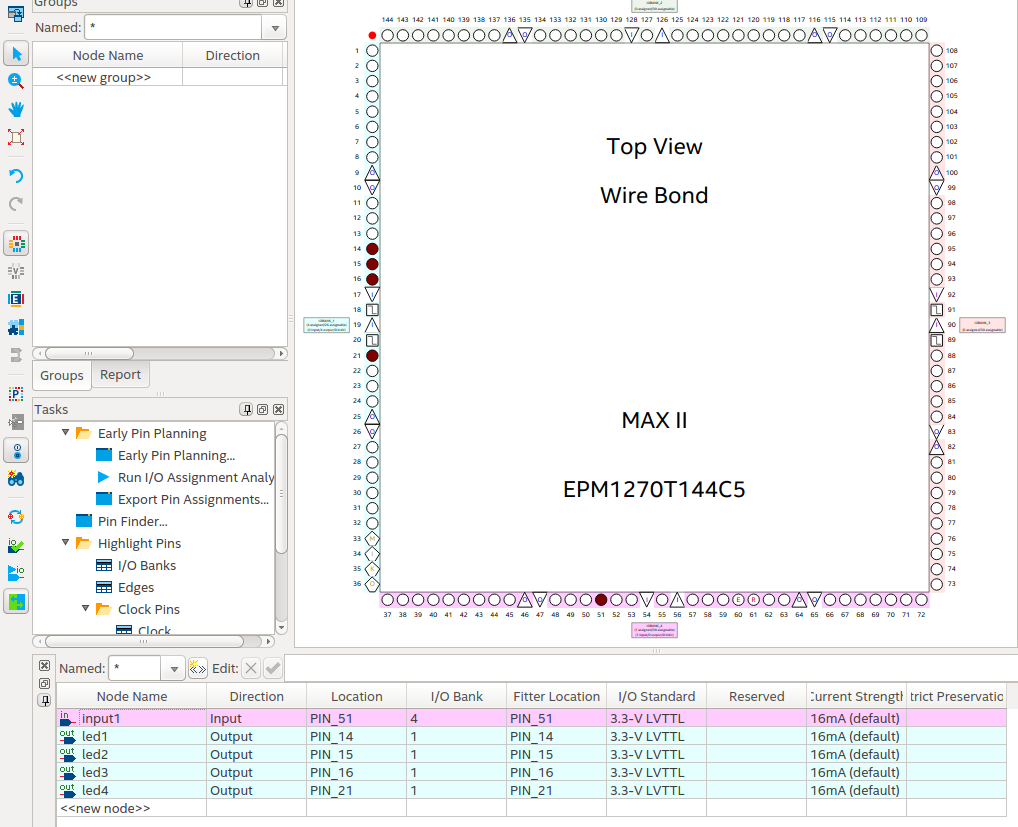

Kami menyusun proyek. Sekarang, di menu “Assignments-Pin Planner”, konfigurasikan pin pada chip:

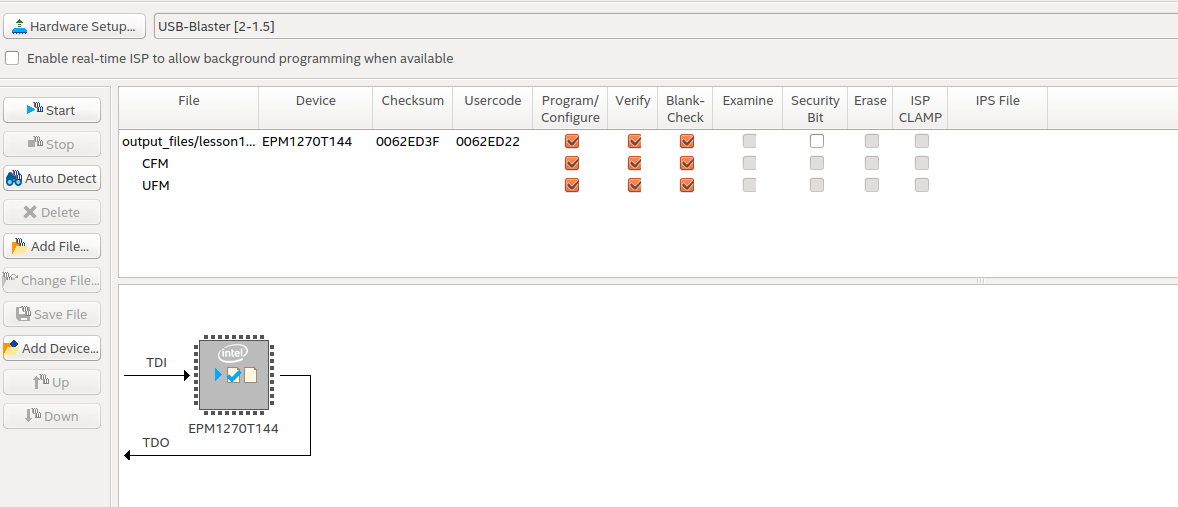

Kompilasi lagi. Sekarang semuanya siap untuk pemrograman: Tools-Programmer. Kami menghubungkan programmer dan power ke board, di Hardware Setup kami memilih USB-Blaster kami, mengatur kotak centang seperti yang ditunjukkan pada gambar dan Mulai.

Setelah Programmer melaporkan Berhasil. Anda dapat melihat hasilnya di papan tulis:

Kesimpulan

Pelajaran ini menjelaskan cara membuat lingkungan kerja dan proyek FPGA sederhana pertama dalam bahasa pemrograman Python.

Dianggap:

- cara menginstal:

- Pemrogram USB Blaster yang dikonfigurasikan di Ubuntu;

- FPGA Proyek FPGA dikembangkan;

- Pengujian dan verifikasi proyek;

- Menyusun proyek untuk FPGA;

- Proyek diunggah ke FPGA.