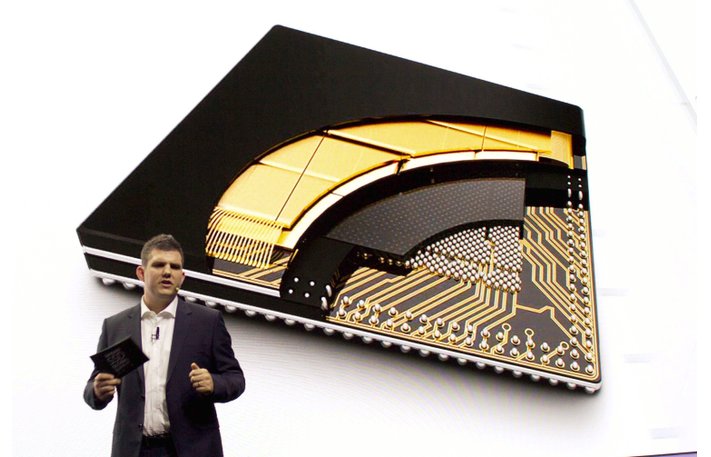

Intel Foveros 3D

Intel Foveros 3DKarena Hukum Moore tidak berlaku lagi, perancang chip harus mencari cara lain untuk meningkatkan kinerja. Salah satu teknologi yang cocok untuk ini disebut penumpukan chip 3D. Ini adalah arsitektur tumpukan tiga dimensi chip, dalam pengembangan yang dipimpin Intel. Dua bulan lalu, Intel memperkenalkan arsitektur

3D Foveros : struktur tiga dimensi yang mencakup CPU 10 nm, chip I / O dan koneksi listrik vertikal TSV (Through Silicon Via) di tengah chip, dan chip memori di atas seluruh chip.

Pada Rice Oil and Gas HPC konferensi komputasi kinerja tinggi, AMD

meyakinkan bahwa itu sedang mengerjakan versi sendiri dari arsitektur chip 3D.

Forrest Norrod, wakil presiden senior dan manajer umum, mengatakan perusahaan sedang mengembangkan beberapa teknologi untuk meningkatkan pengembalian dan memotong masalah yang terkait dengan penghentian Hukum Moore dan konsekuensi dari penghentian pertumbuhan kepadatan transistor dan frekuensi clock. Ini adalah konsekuensi yang tak terhindarkan dari produsen yang mendekati batas di mana ukuran transistor hanya beberapa atom (ukuran atom silikon 0,2 nanometer). Pertumbuhan daya komputer dalam beberapa tahun terakhir datang tidak hanya dari peningkatan kecepatan komputasi, tetapi dari peningkatan paralelisme.

Seperti perusahaan lain, AMD telah menghadapi batasan pada area chip sekitar 700 mm² dan dipaksa untuk mengembangkan arsitektur 3D. Perusahaan sudah mengambil pendekatan ini, menempatkan memori HBM2 di sebelah substrat GPU, yaitu, dalam kasus yang sama dengan prosesor. Tetapi di masa depan, perusahaan berencana untuk beralih ke penumpukan 3D yang lebih maju.

Norrod mengatakan AMD sedang berupaya menempatkan SRAM dan DRAM langsung di atas komponen komputasi (seperti prosesor dan GPU) untuk menyediakan bandwidth dan kinerja yang lebih banyak.

Samsung Polaris

Samsung PolarisPendekatan ini berbeda dari implementasi paket-on-paket (PoP) yang biasa, yang hanya menempatkan dua kasus selesai di atas satu sama lain, seperti yang ditunjukkan Norrod menggunakan chip Samsung Polaris sebagai contoh. Dalam contoh ini, penutup DRAM terhubung melalui dua baris tambahan konektor BGA yang mengelilingi chip dasar. Konektor BGA ini mentransfer data antara dua chip. Seperti halnya desain standar, logikanya ada di bagian bawah tumpukan karena kebutuhan akan lebih banyak konektor, tetapi kedua kristal tersebut tidak terhubung secara langsung. Dengan demikian, pendekatan PoP memberikan kepadatan maksimum, tetapi ini bukan opsi tercepat.

Dalam penumpukan 3D sejati, dua chip (dalam hal ini, memori dan prosesor) terletak satu di atas yang lain dan dihubungkan oleh koneksi TSV vertikal yang secara langsung menghubungkan mereka. Koneksi TSV ini mentransfer data antara kristal pada kecepatan setinggi mungkin dan biasanya terletak di tengah chip, seperti yang kita lihat dengan Intel Foveros 3D. Pasangan langsung ini meningkatkan kinerja dan mengurangi konsumsi daya (semua pergerakan data membutuhkan daya, tetapi koneksi langsung mengoptimalkan proses). Penumpukan 3D juga meningkatkan kepadatan.

Norrod tidak masuk ke rincian proyek yang sedang dikembangkan, tetapi ini mungkin berubah menjadi perubahan mendasar dalam desain prosesor AMD.

Teknologi 3D Intel Foveros yang baru dapat berubah menjadi momen yang menentukan bagi industri, sehingga tidak mengejutkan mendengar bahwa AMD bergerak ke arah ini,

tulis Tom's Hardware .

Sejauh ini, tidak ada detail teknis tentang teknologi penumpukan 3D AMD, selain yang dikatakan Forrest Norrod pada presentasi berjudul Working Beyond Moore's Law, lihat video di bawah ini.

Apa alternatif lain yang ada untuk kembali ke kurva pertumbuhan eksponensial yang diprediksi oleh Gordon Moore? Tidak ada jawaban tunggal untuk pertanyaan ini. Industri semikonduktor sedang bereksperimen dengan bahan yang dapat digunakan sebagai pengganti silikon. Beberapa bahan semikonduktor III-V dapat beroperasi

pada tegangan yang lebih rendah dan pada frekuensi yang lebih tinggi daripada silikon , tetapi mereka tidak membuat atom lebih kecil atau lebih lambat cahaya. Pembatasan fisik masih berlaku.

Pertanyaannya tetap bagaimana chip 3D masa depan akan dingin. Bagaimana cara efektif mendinginkan chip seperti itu ketika energi didistribusikan ke seluruh chip? Microcircuit tidak akan dapat mentransfer daya ke semua sirkuit secara bersamaan tanpa terlalu panas. Dia mungkin harus menjaga sebagian bagian terputus sebagian besar waktu dan memasok daya ke setiap bagian hanya selama penggunaan.