Suatu hari,

stasiun otomatis Jepang Hayabusa-2 menjatuhkan bom pada asteroid Ryugu . Pesawat ruang angkasa dikendalikan oleh sistem yang stabil terhadap radiasi berdasarkan chip HR5000 (JAXA2010 / 101) dengan inti prosesor MIPS 5Kf 64-bit. Komputer on-board menjalankan sistem operasi uITRON real-time, salah satu keluarga standar RTON TRON, yang muncul di Jepang pada 1980-an

dan layak mendapat jabatan terpisah .

Dalam catatan ini, saya akan menjelaskan secara singkat apa yang termasuk dalam HR5000 SoC dan inti prosesornya, saya akan menunjukkan foto-foto dua pengembang kunci garis MIPS 4K dan 5K, dan juga memberi tahu bagaimana Anda dapat bermain di rumah di FPGA dengan "keturunan adik lelaki" dari komputer ini - Kernel 32-bit MIPS microAptiv UP, yang kodenya dalam bahasa deskripsi perangkat keras Verilog didasarkan pada MIPS 4KEc.

Badan kedirgantaraan Jepang JAXA melisensikan inti prosesor MIPS 5Kf dari MIPS Technologies, sebuah perusahaan Amerika. Ini terjadi pada tahun 2000-an. Grup yang mengembangkan inti ini telah ada dalam berbagai konfigurasi selama 40 tahun:

- Pertama, pada 1978-1984, MIPS adalah proyek di Stanford, dipimpin oleh John Hennessey. Atas keberhasilan proyek ini, Hennessey menjadi penulis buku teks paling terkenal tentang arsitektur komputer dan di beberapa titik - presiden Stanford.

- Kemudian, pada tahun 1984, MIPS menjadi perusahaan komersial - MIPS Sistem Komputer. Pada tahun yang sama, ARM juga dikomersialkan. Pada tahun 1991, MIPS merilis mikroprosesor 64-bit pertama di dunia - MIPS R4000.

- Setelah itu, MIPS diserap oleh Silicon Graphics dan pada 1990-an ia digunakan di dalam stasiun grafis di mana film pertama dengan grafis realistis dibuat di Hollywood (Jurassic Park).

- Pada tahun 2000-an, grup ini dipisahkan menjadi MIPS Technologies dan, khususnya, merancang prosesor untuk JAXA. MIPS berkantor pusat di California, beberapa pengembang MIPS 5Kf berlokasi di MIPS Eropa di Kopenhagen.

- Pada 2012, MIPS Technologies dibeli oleh perusahaan Inggris Imagination Technologies, yang menjadi terkenal sebagai pengembang GPU di dalam Apple iPhone awal.

- Pada 2017, Apple melempar Imagination, dan setelah beberapa gangguan, teknologi dan bagian dari kelompok MIPS diintegrasikan ke dalam Wave Computing, sebuah startup yang mengembangkan chip untuk mempercepat jaringan saraf.

- Chip Wave Computing adalah kombinasi dari sekelompok prosesor 64-bit MIPS I6500, pengganda matriks berdasarkan susunan sistolik ala Google TPU, dan prosesor pemroses data yang didasarkan pada perangkat dengan Arsitektur yang dikonfigurasi ulang kasarnya - CGRA ) Prosesor klasik di kluster I6500 memuat pengali matriks dan prosesor aliran data, pengali matriks menyediakan kerapatan komputasi, dan pengolah aliran data tugas terletak di tengah antara prosesor klasik dan pengali matriks - lebih fleksibel daripada pengali dan lebih produktif daripada CPU klasik.

Jadi saya mengambil foto dengan salah satu dari dua pengembang kunci garis MIPS 4K dan 5K - Larry Hudepohl, Larry Huedepol (di sebelah kanan dengan kemeja merah). Larry memulai karirnya di Digital Equipment Corporation (DEC) sebagai perancang prosesor untuk MicroVAX. Kemudian Larry bekerja untuk perusahaan kecil Cyrix, yang pada akhir 1980-an menantang Intel dan membuat prosesor FPU yang kompatibel dengan Intel 80387 dan 50% lebih cepat. Kemudian Larry mendesain chip MIPS di Silicon Graphics. Ketika MIPS Technologies terpisah dari Silicon Graphics, Larry dan Ryan Quinter bersama-sama meluncurkan produk MIPS independen pertama, MIPS 4K, yang menjadi tulang punggung lini yang mendominasi elektronik rumah tahun 2000-an (pemutar DVD, kamera, TV digital). Kemudian MIPS 5K terbang ke angkasa - itu digunakan oleh badan antariksa Jepang JAXA. Kemudian Larry, sebagai VP Hardware Engineering, memimpin pengembangan baris-baris berikut, dan sekarang ia sedang mengerjakan arsitektur akselerator Wave baru:

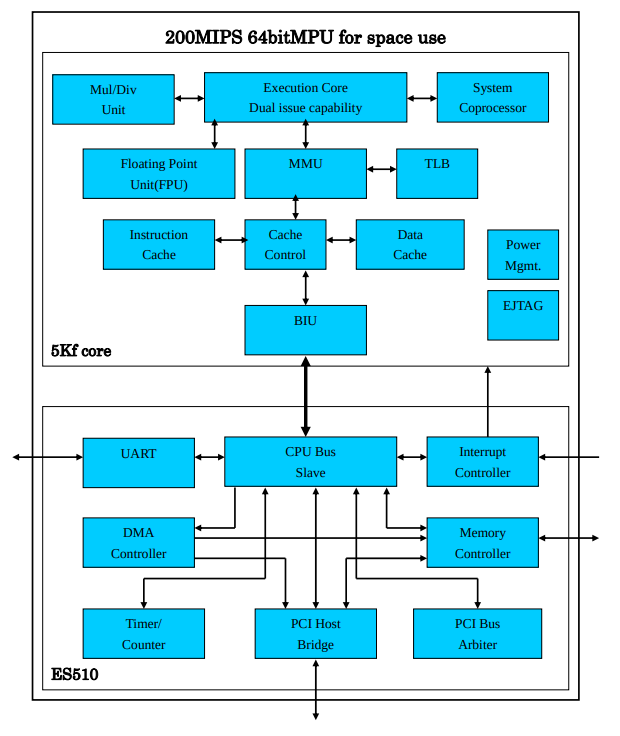

Sekarang kembali ke prosesor di Hayabusa-2 (di Hayabusa-1 berbeda). Berikut ini adalah

lembar data untuk inti prosesor MIPS64 5Kf dan

halaman dengan data sistem pada chip HR5000 . Perhatikan beberapa poin menarik.

Pertama-tama, MIPS 5Kf adalah prosesor pipelined. Jika Anda tidak terbiasa dengan cara kerjanya, maka cara termudah untuk saling mengenal adalah mempelajari bab ketujuh buku "Sirkuit Digital dan Arsitektur Komputer" oleh David M. Harris dan Sarah L. Harris, versi terbaru yang dapat diunduh ke bahasa Rusia di

sini atau di

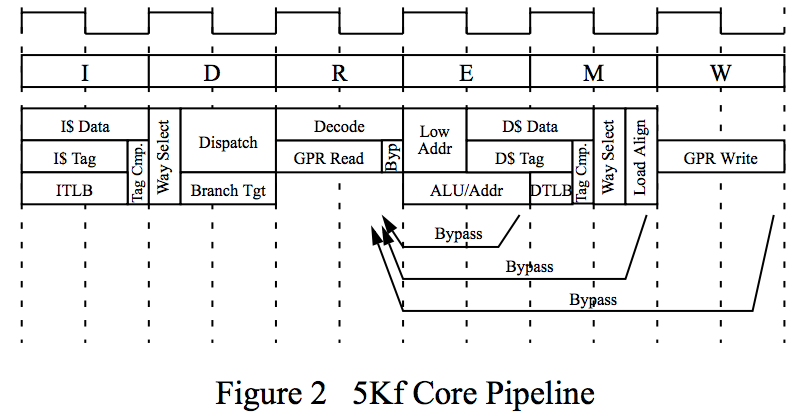

sini ) . Konveyor di MIPS 5Kf berbeda dari konveyor MIPS klasik dari Harris & Harris. Anda yang telah membaca X&X dapat melihat perbedaannya dan tebak mengapa:

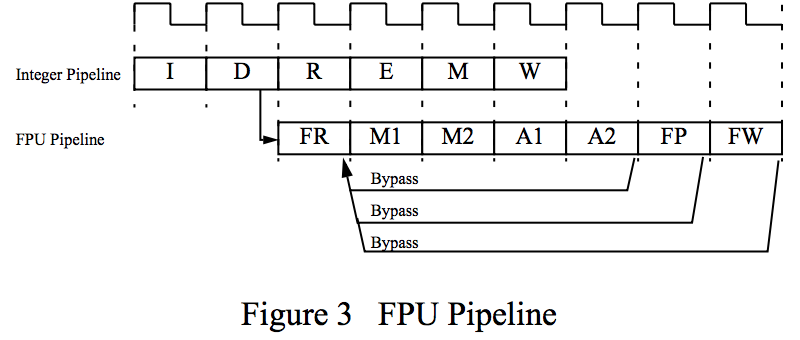

Tentu saja, MIPS 5Kf tidak memiliki lima tahap pipa, tetapi enam, dengan tahap Pengiriman tambahan. Tahap ini diperlukan untuk membuat MIPS 5Kf terikat superscalar. Ia tidak hanya dapat melakukan operasi satu demi satu dalam pipa, tetapi juga dapat melakukan operasi titik-mengambang secara bersamaan dengan operasi integer atau dengan operasi memori (memuat atau menyimpan). Stage Dispatch meluncurkan coprocessor floating point yang memiliki pipeline tujuh tahap sendiri:

Dan di sini di sebelah kanan dalam foto adalah Darren Jones, Darren Jones, pengembang FPU di MIPS 5Kf. Huruf "f" dalam "5Kf" berarti persis bahwa ia memiliki titik mengambang:

Di sini, di piring ini Anda dapat melihat berapa banyak siklus memerlukan operasi yang berbeda di FPU dan seberapa sering (tingkat pengulangan) mereka dapat dijalankan dalam pipa. Misalnya, perkalian presisi tunggal membutuhkan empat siklus, tetapi Anda dapat memulai perkalian baru dalam pipa setiap siklus. Jadi FPU dapat secara bersamaan memproses empat perkalian presisi tunggal pada setiap tahap pemrosesan. Tetapi penggandaan presisi ganda membutuhkan lima siklus, dan Anda bisa memulainya hanya dengan jeda dalam siklus. Operasi kompleks untuk mengambil akar kuadrat dari ketelitian ganda membutuhkan sebanyak 32 siklus, dan Anda dapat memulai pengambilan akar kuadrat baru hanya setelah 29 siklus. Ini adalah bagaimana perhitungan koordinat kapal dan formula geraknya di luar angkasa dioptimalkan:

Hayabusa-2 menggunakan konfigurasi MIPS 5Kf dengan instruksi 32-kilobyte dan cache data terpisah. Pada saat yang sama, tidak jelas dari

deskripsi singkat HR5000 apakah ia menggunakan cache empat saluran 8 kilobyte - atau cache dua saluran 16 kilobyte. Anda dapat membaca bagaimana cache ini berfungsi baik di X&X maupun di

presentasi lama saya tentang cache , serta di buku yang berguna

Lihat MIPS Run Linux 2nd Edition oleh Dominic Sweetman:

Hayabusa-2 juga memiliki Memory Management Unit (MMU), dengan terjemahan lookaside buffer (TLB). TLB adalah alat universal untuk mengubah alamat dengan cepat dari virtual ke fisik. TLB memungkinkan Anda untuk:

Sembunyikan memori sistem operasi dari kode yang tidak terprivasi.

Lindungi program pengguna dari satu sama lain.

Menyediakan akses program ke jumlah memori virtual yang melebihi jumlah RAM fisik.

Alamat memori fisik yang lebih besar daripada alamat virtual yang tersedia.

Tempatkan program di bagian manapun dari memori fisik.

Mengizinkan beberapa wilayah memori terlihat seperti bagian berurutan.

Memungkinkan Anda memuat potongan program dari perangkat eksternal sesuai kebutuhan.

TLB juga mengaitkan berbagai atribut dengan alamat: membaca, menulis, dan mengeksekusi, serta atribut cache dan koherensi.

Atribut cache diperlukan untuk menunjukkan prosesor di mana ruang alamat untuk tingkat cache berikutnya, dan di mana untuk I / O Resistor yang tidak bisa di-cache.

Atribut koherensi diperlukan untuk beberapa core prosesor untuk bekerja bersama, masing-masing dengan cache tingkat pertama sendiri, dan bersama-sama mereka menggunakan cache tingkat kedua yang umum.

TLB dapat menyimpan indikator bahwa halaman dengan alamat yang diberikan telah direkam. Ini membantu saat bertukar, memuat-bongkar halaman memori pada sistem dengan memori fisik kurang dari aplikasi perlu untuk mengatasi semua bagian kode dan data dengan alamat virtual.

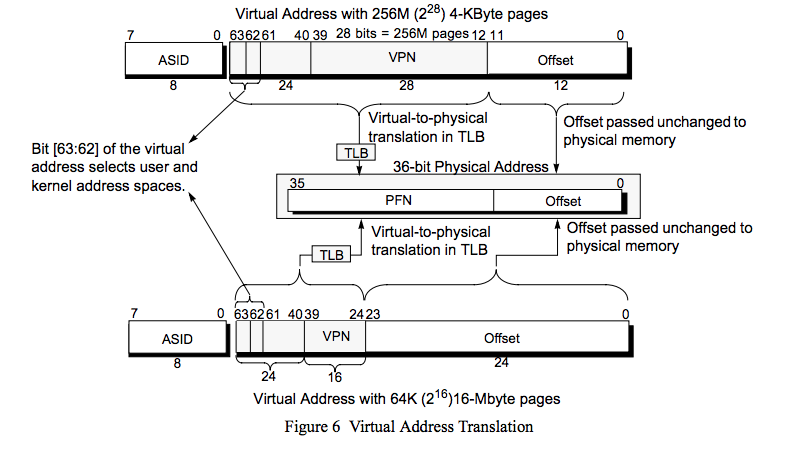

Beginilah terjemahan dari alamat virtual 64-bit menjadi alamat fisik 36-bit pada MIPS 5Kf. Mengapa pada Hayabusa-2 prosesor 64-bit dengan alamat fisik 36-bit? Saya menduga bahwa Hayabusa-2 mengambil foto dan harus memproses gambar, yang membutuhkan banyak memori. Mungkin untuk beberapa algoritma, 64-bit aritmatika dan 64-bit cache exchange (atau 64-bit non-cacheable memory exchange) meningkatkan sesuatu, dan ternyata bermanfaat dalam ruang. Tapi saya tidak tahu pasti, saya mungkin perlu bertanya kepada

Zelenyikot dan

amartologi , yang tahu lebih banyak tentang ruang daripada saya.

Anda dapat membaca tentang TLB di X&X dan See MIPS Run, tetapi ada nuansa: kedua buku menggambarkan seperti apa TLB dari sudut pandang programmer. Tetapi dari sudut pandang pengembang perangkat keras, perancang prosesor menipu programmer dengan menunjukkan kepadanya TLB sebagai satu tabel terjemahan asosiatif, terlepas dari kenyataan bahwa sebenarnya ada tiga tabel di dalam TL: ada tiga instruksi micro-TLB, data micro-TLB dan common (Joint TLB). Pertama, perangkat manajemen memori mencari ITLB dan DTLB, dan hanya jika tidak menemukannya, perangkat itu mengambilnya dari JTLB. Prosesor ini memakan biaya 2 siklus tambahan. Lihat juga

presentasi lama saya di TLB :

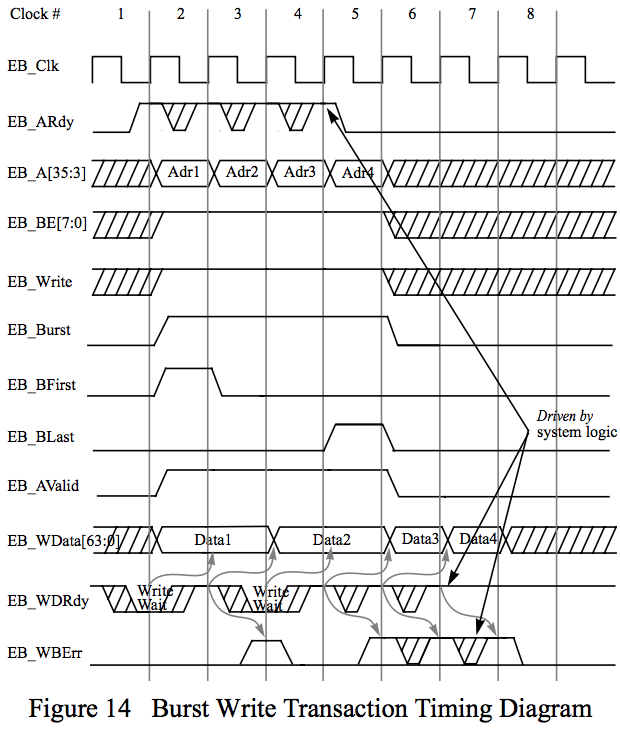

Antarmuka antara cache tingkat pertama dan pengontrol memori di MIPS 5Kf di Hayabusa-2 disebut EB (diucapkan IB). Ini kependekan dari Bus Eksternal. Ini mirip dengan AHB dan AXI, dan memungkinkan Anda untuk meledak, membuang dari cache, atau mengisi cache dari memori seluruh baris, menggunakan transfer dalam loop berurutan.

Di luar inti prosesor, HR5000 memiliki pengontrol interupsi, modul UART, pengontrol akses memori langsung, pengatur waktu, dan pengontrol PCI:

Untuk bekerja di luar angkasa, chip harus dilindungi dari radiasi. Saya bukan spesialis dalam proteksi radiasi, untuk ini ada

amartologi tentang Habré, tetapi saya tahu bahwa proteksi semacam itu dapat dilakukan baik pada level teknologi produksi fisik, dan pada level berbagai pemeriksaan ECC, dan bahkan pada level arsitektur, dengan tripling, dll. Pencipta sistem kristal HR5000 memutuskan untuk menggunakan rute RTL2GDSII yang biasa diadopsi dalam aplikasi komersial, sintesis grafik dari elemen logis dari kode dalam bahasa deskripsi perangkat keras Verilog. Namun, setelah menerima grafik seperti itu (netlist), mereka memodifikasinya menggunakan perpustakaan khusus primitif hard-by-design (HBD) (tidak pernah menggunakan ini, jadi klarifikasi dalam komentar diterima):

Karena MIPS 5Kf ditulis dalam Verilog, dapat diubah tidak hanya menjadi netlist, dan tidak hanya menjadi topeng untuk pembuatan chip di pabrik, tetapi juga menjadi konfigurasi FPGA. Sayangnya, sumber MIPS 5Kf tidak ada dalam domain publik, tetapi dalam domain publik adalah kode sumber keturunan "adik laki-lakinya", prosesor MIPS 4K 32-bit. "Keturunan" ini disebut MIPS microAptiv UP, dan konfigurasi dasarnya termasuk dalam paket MIPSfpga. Kode MIPS 4K / 4KEc / microAptiv UP / M5150 (ini semua adalah versi progresif dari baris) juga ditulis oleh Larry, Ryan dan Darren.

Anda dapat bermain dengan pipeline, cache, perangkat manajemen memori dan MIPS microAptiv UP interupsi kernel, jalankan di simulator atau papan dengan FPGA / FPGA. Untuk melakukan ini, cukup unduh

Paket Persiapan MIPS Open ™ FPGA , bersama dengan

MIPS Open ™ FPGA Labs , dan (ini penting!) Lengkapi dengan

MIPSfpga + . Dalam yang terakhir ada

laboratorium tentang pipa, cache, dan perangkat manajemen memori .

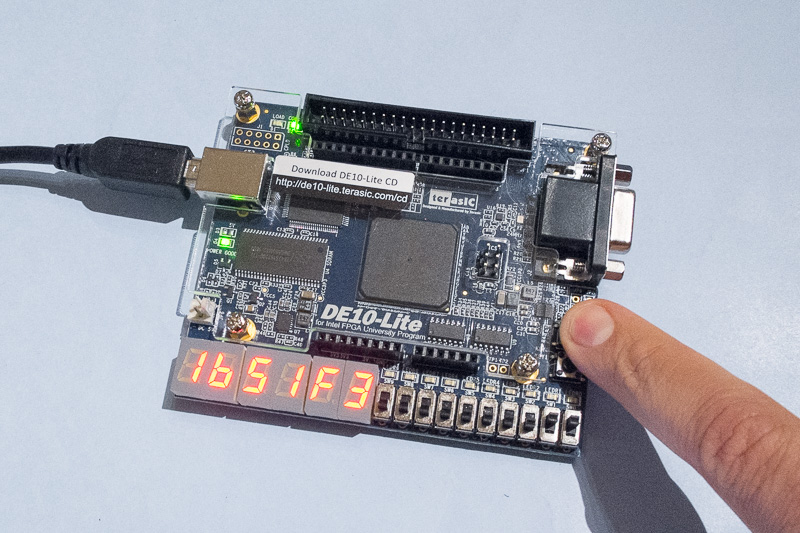

Anda dapat mensintesis dan menjalankan prosesor MIPS microAptiv UP pada papan murah untuk $ 85 (harga akademik $ 55):

Untuk bekerja dengan paket MIPSfpga / MIPSfpga +, Anda memerlukan pengetahuan tentang bahasa deskripsi perangkat keras Verilog, prinsip-prinsip desain pada tingkat transfer register dan kemampuan untuk menulis dalam assembler MIPS.

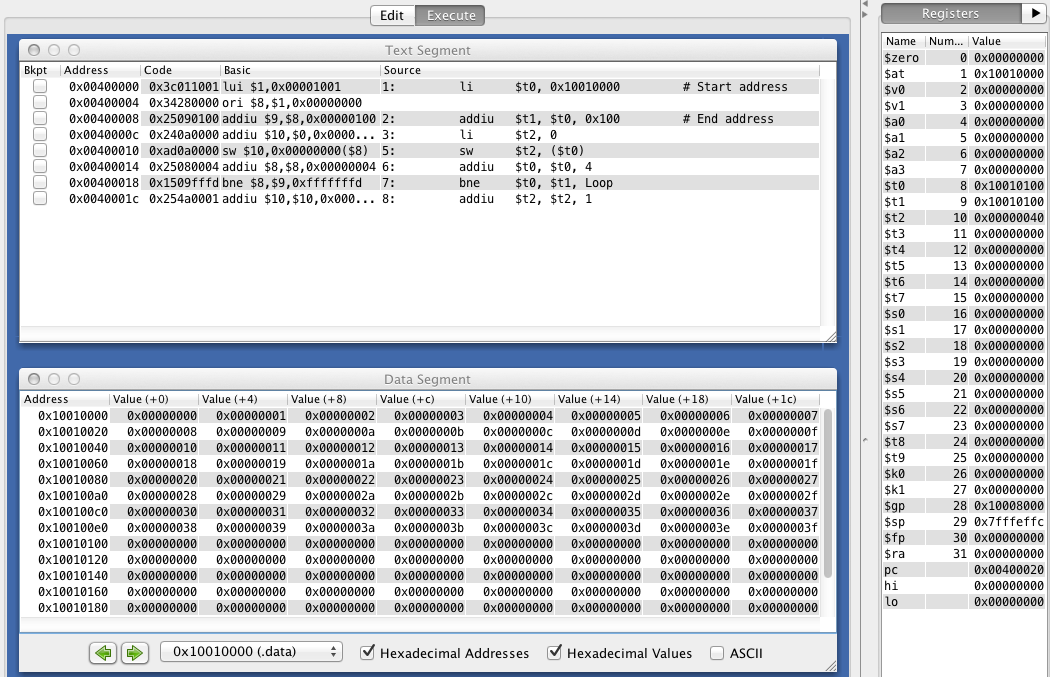

Assembler MIPS adalah yang paling mudah dipelajari. Untuk melakukan ini, Anda dapat

mengunduh simulator MARS (MIPS Assembler dan Runtime Simulator) . Anda dapat mempelajari cara menggunakannya dalam 5 menit, pada kenyataannya, ada tiga tombol di dalamnya - merakit, menjalankan, menjalankan langkah demi langkah:

Kemudian Anda dapat menghabiskan hari berlatih menulis dalam bahasa assembly untuk buku

Harris & Harris dan

See MIPS Run Linux .

Jika Anda tidak tahu apa-apa tentang pengembangan sirkuit digital secara umum dan dalam bahasa untuk menggambarkan peralatan pada khususnya, Anda dapat mulai dengan kursus online Rosnanov untuk anak sekolah, dalam tiga bagian:

"Dari transistor ke microcircuit" ,

"Sisi logis dari sirkuit digital" ,

"Sisi fisik dari sirkuit digital" ,

"Sisi fisik sirkuit digital " ). Kemudian Anda dapat mempelajari Verilog pada X&X dan memahami bahwa ada prosesor pada prosesor

schoolPSI yang disederhanakan.

Jika Anda tertarik dengan topik ini dan ingin berpartisipasi dalam pekerjaan di

MIPS Open (dalam kerangka di mana kernel MIPS microAptiv UP dibuka), tulis di komentar. Rosnanovtsy juga mengadakan

seminar untuk anak-anak sekolah tentang desain digital pada 17-19 April , yang akan mencakup, antara lain, prosesor ruang angkasa ini. Hayabusa-2 membom Ryuga tidak sia-sia - ini juga merupakan kesempatan bagi anak sekolah dan siswa Rusia untuk mencari tahu apa yang ada di dalam dirinya.