Bab selanjutnya dari dokumentasi resmi Cypress tentang pengaturan waktu dan pengaturan ulang. Seperti yang telah disebutkan dalam artikel pertama seri ini, modul ini menyediakan pemilihan waktu dan resolusi, serta reset pilihan dalam UDB. Lebih detail - di bawah potongan.

Isi umum dari siklus “UDB. Apa ini? "

Bagian 1. Pendahuluan. Pld.Bagian 2. Datapath.Bagian 3. Datapath FIFO.Bagian 4. Datapath ALU.Bagian 5. Datapath. Hal-hal kecil yang bermanfaat.Bagian 6. Modul manajemen dan status.Bagian 7. Pengaturan waktu dan reset modul kontrol. (Artikel saat ini)

Bagian 8. Mengatasi UDB21.3.4 Modul Reset dan Kontrol Jam

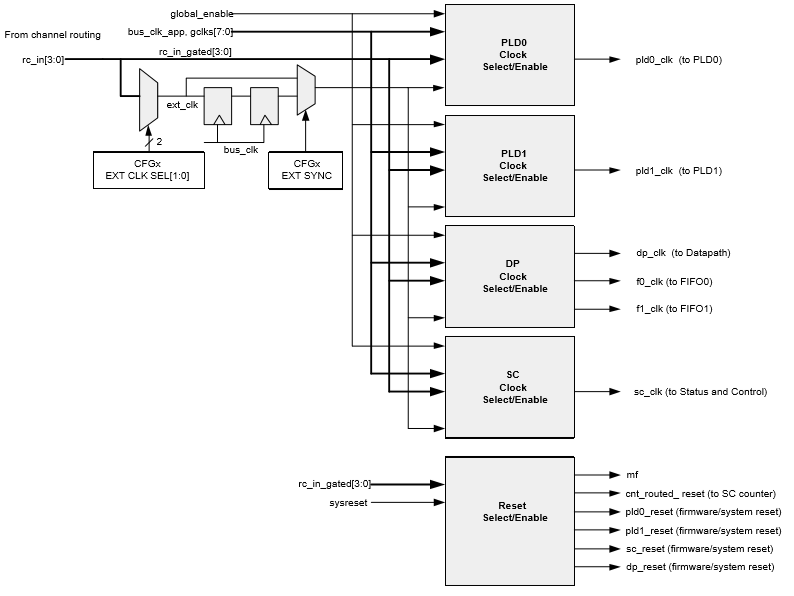

Fungsi utama modul ini adalah untuk memilih jam dari jam global atau jam bus yang tersedia untuk setiap modul PLD, Datapath, dan modul kontrol dan status. Modul ini juga mendukung pengaturan ulang blok dinamis dan perangkat lunak UDB. Seperti yang ditunjukkan pada Gambar 21-38, ada empat unit kontrol jam dan satu unit kontrol reset. Empat input (RC_IN [3: 0]) tersedia untuk diteruskan dari matriks jejak global. Setiap unit kontrol jam dapat memilih sumber untuk clock mengaktifkan input dari input jejak ini, dan ada juga multiplexer yang memungkinkan Anda untuk memilih salah satu input jejak untuk digunakan sebagai sumber jam eksternal. Seperti yang Anda lihat pada gambar, pilihan sumber jam eksternal dapat disinkronkan. Untuk setiap komponen UDB, ada 10 jam untuk dipilih: 8 jam digital global, jam bus, dan jam eksternal yang dipilih (ext clk). Setiap sinyal input yang dilacak (rc_in) dapat digunakan baik sebagai aktivator level-sensitif atau sebagai aktivator tepi-sensitif. Fungsi reset blok ini menyediakan reset blok PLD dan penghitung SC yang terlacak, serta kemampuan untuk mengatur ulang setiap blok secara terprogram untuk mendukung konfigurasi ulang.

Jam bus yang diterapkan pada jam dan reset modul kontrol berbeda dari jam bus sistem. Sinyal ini disebut "bus_clk_app" dan dikunci dengan cara yang sama seperti sinyal jam digital lainnya. Jam bus sistem hanya digunakan untuk operasi input-output dan dibuka secara otomatis untuk setiap akses. Datapath Clock Generator menghasilkan tiga jam: satu untuk Datapath dan satu sinyal untuk setiap FIFO.

Gambar 21-38. Modul kontrol jam dan reset.

21.3.4.1 Kontrol jam

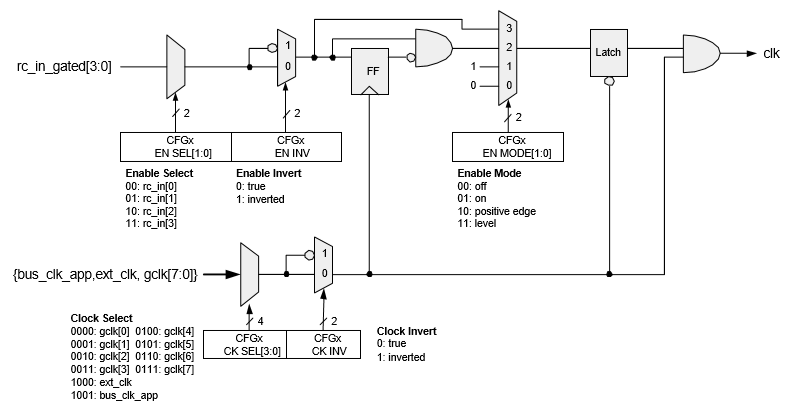

Gambar 21-39 menunjukkan contoh pemilihan waktu dan skema resolusi. Setiap UDB memiliki empat skema seperti itu: satu untuk setiap blok PLD, satu untuk Datapath, dan satu untuk blok kontrol dan status. Komponen utama dari rangkaian ini adalah multiplexer pemilihan jam global, inverter jam, clock memungkinkan multiplexer sinyal, clock mengaktifkan inverter sinyal dan logika deteksi diferensial.

Gambar 21-39. Kelola pemilihan / aktivasi waktu.

Pemilihan JamAda delapan jam digital global yang diteruskan ke semua UDB. Semua dari mereka dapat dipilih. Jam digital global adalah output dari pembagi frekuensi yang dipilih oleh pengguna. Lihat “Sistem Pengaturan Waktu” di halaman 109 dari dokumen asli. Pilihan lain adalah jam bus, yang memiliki frekuensi tertinggi dalam sistem. Sinyal ini disebut "bus_clk_app" dan dilacak secara terpisah dari jam bus sistem. Selain itu, untuk mendukung fungsi dengan sinyal jam langsung (misalnya, SPI), jalur jejak eksternal dapat dipilih sebagai sinyal jam input. Karena fungsi aplikasi terikat pada batas arbitrer dalam UDB, memilih sinyal clock individual untuk setiap subkomponen UDB berkontribusi pada granularitas yang tepat dalam pemrograman.

Inversi JamSinyal jam yang dipilih dapat dibalik. Ini akan membatasi frekuensi maksimum pekerjaan karena adanya bagian dengan siklus setengah siklus. Perekaman bus simultan dan perekaman internal (misalnya, program merekam nilai penghitung baru selama operasinya) tidak didukung ketika jam internal dibalik dan memiliki frekuensi yang sama dengan jam bus. Batasan ini mempengaruhi A0, A1, D0, D1, serta register kontrol dalam mode penghitung.

Jam Aktifkan PilihanSinyal aktifkan jam dapat diteruskan ke sinyal sinkron dan dipilih pada salah satu dari empat input matriks jejak yang tersedia untuk blok ini.

Jam Mengaktifkan PembalikanSinyal aktifkan jam dapat dibalik. Karena ini, sinyal ini dapat dihasilkan dalam polaritas apa pun.

Mode Aktifkan JamSecara default, mode resolusi jam MATI. Setelah mengatur operasi unit target, perangkat lunak dapat mengatur salah satu mode operasi yang dijelaskan di bawah ini menggunakan register CFGxEN MODE [1: 0], ditunjukkan pada Gambar 21-39.

Tabel 21-23. Mode Resolusi Pengaturan Waktu.

Menggunakan Izin JamAda dua kasus penggunaan umum untuk izin waktu.

Perangkat Lunak Aktif (Firmware Enable) : Diasumsikan bahwa sebagian besar fungsi memerlukan jam perangkat lunak memungkinkan untuk memulai dan menghentikan fungsi. Karena batas fungsi yang terikat pada larik UDB adalah bersyarat, fungsi tersebut dapat menjangkau beberapa UDB dan / atau bagian-bagian UDB. Oleh karena itu, diperlukan suatu cara untuk memasukkan setiap fungsi secara atom. Ini biasanya diterapkan menggunakan sedikit dalam register kontrol diteruskan ke satu atau lebih jam mengaktifkan input. Skenario ini juga mendukung kasus di mana aplikasi perlu menjalankan beberapa blok yang tidak terkait pada saat yang sama.

Emulasi Generasi Jam Lokal : Fitur ini memungkinkan UDB untuk menghasilkan jam lokal dan mendistribusikannya ke UDB lain dalam array menggunakan templat implementasi aktivasi jam sinkronisasi, daripada secara langsung mencatat setiap UDB secara terpisah. Menggunakan fungsi Positive Edge untuk memungkinkan resolusi menghilangkan batasan pada siklus tugas dari sinyal resolusi.

Pengaturan waktu FIFO khususBlok FIFO Datapath memiliki fitur pengaturan waktu. Secara default, clocking FIFO memiliki konfigurasi yang sama dengan clocking Datapath. Namun, blok FIFO memiliki bit kontrol khusus yang mengubah konfigurasi jam:

- setiap jam FIFO dapat dibalik relatif terhadap polaritas jam Datapath yang dipilih;

- ketika mode FIFO FAST dipilih, bus clock menggantikan pilihan jam Datapath yang biasanya menggunakan FIFO.

21.3.4.2 Mengatur ulang manajemen

Ada dua mode pengaturan ulang: bawaan dan standar. Mode diatur menggunakan bit

ALT RES di setiap register konfigurasi UDB CFG31. Secara default, nilai bit adalah 0 (mode lama); Anda disarankan untuk memberikan nilai 1 (mode standar). Mode standar memiliki tingkat granularitas yang lebih besar - blok individual di dalam UDB dapat menggunakan flush yang terlacak. Untuk informasi tentang mode lama, hubungi Cypress.

Kontrol Reset PLDGambar 21-40 menunjukkan sistem reset PLD.

Gambar 21-40. Atur Ulang Struktur PLD.Atur Ulang Kontrol Datapath

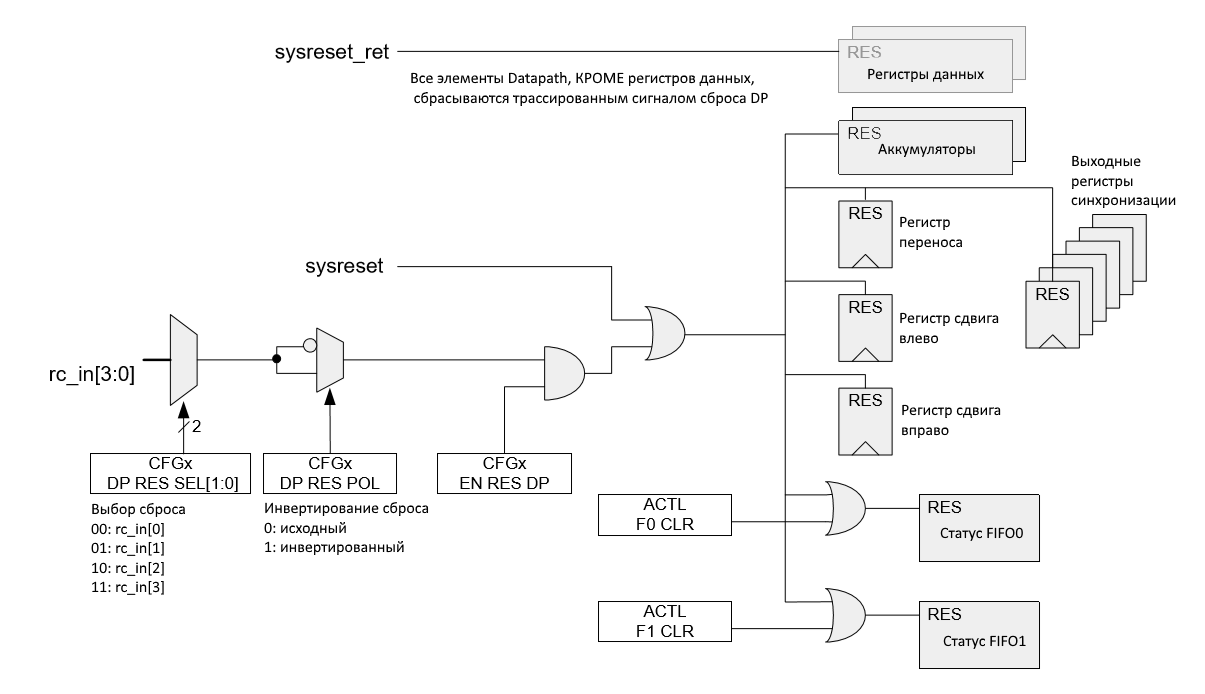

Gambar 21-40. Atur Ulang Struktur PLD.Atur Ulang Kontrol DatapathGambar 21-41 menunjukkan sistem reset Datapath. Flush yang dilacak berlaku untuk semua register dan status Datapath kecuali register data D0 dan D1. Register data adalah register persisten. Konten FIFO tidak ditentukan setelah reset, karena terletak di RAM.

Gambar 21-41. Struktur atur ulang datapath.Status dan Kontrol Atur Ulang Kontrol

Gambar 21-41. Struktur atur ulang datapath.Status dan Kontrol Atur Ulang KontrolGambar 21-42 menunjukkan sistem kendali dan pengaturan ulang status. Daftar kontrol / penghitung dan status memiliki pengaturan ulang jejak yang umum, namun mereka diaktifkan secara terpisah. Register tumpang tindih / periode dan kontrol bantu adalah register simpanan.

Gambar 21-42. Atur ulang manajemen dan manajemen status.

Gambar 21-42. Atur ulang manajemen dan manajemen status.21.3.4.3 Power On UDB Inisialisasi (POR)

Daftar dan Inisialisasi NegaraTabel 21-24. Inisialisasi status UDB saat diaktifkan

Lacak inisialisasiSaat diaktifkan, status jejak input dan output memiliki fitur berikut:

- semua output UDB yang mengarahkan data ke matriks jejak disimpan pada '0';

- semua driver yang keluar dari jejak dan memasukkan input UDB awalnya nol.

Inisialisasi ini menghindari keadaan yang saling bertentangan selama pelacakan, dan konfigurasi awal terjadi dalam urutan di mana urutan tidak menjadi masalah.

Akhir cerita berikut. Kami sedang menyiapkan terjemahan

terbaru dari bagian yang tersisa dari dokumentasi milik Cypress tentang UDB, yaitu UDB Addressing.