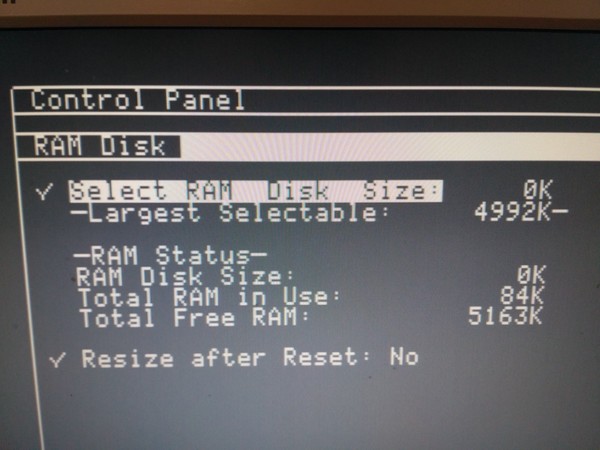

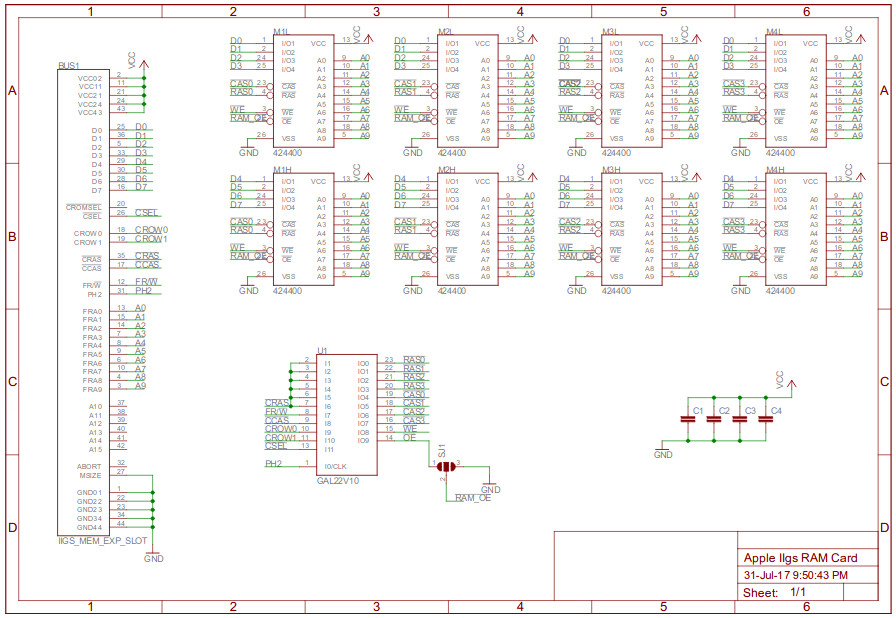

Papan ekspansi RAM yang diusulkan untuk komputer Apple IIgs didasarkan pada chip NEC uPD424400-70 dari beberapa modul SIMM 1-megabyte. Masing-masing microchip ini menyimpan 1 M nibbles dan ditempatkan dalam kasing tipe SOJ 26-pin.

Komputer Apple IIgs ditenagai oleh prosesor 65C816 - 16-bit, tetapi dengan bus data 8-bit. Kartu ekspansi berisi 4 MB RAM. Memori dibagi menjadi empat baris, masing-masing 1 MB. Jalur ini terdiri dari dua chip 1 M nibbles, sehingga total delapan chip diperlukan.

Komputer sudah memiliki slot untuk kartu ekspansi RAM. Ini menampilkan semua sinyal yang diperlukan, komputer juga merawat regenerasi RAM dinamis. Karena itu, kartu ekspansi cukup sederhana. Penulis memutuskan untuk membuat papan berukuran kecil, karena biaya pembuatannya tergantung pada ini, dan juga menempatkan semua logika dalam GAL22V10 FPGA.

Sinyal-sinyal berikut ada pada slot ekspansi RAM:

FRA0-FRA9 - 10-bit address cell multiplexed, disajikan langsung ke input alamat chip RAM dinamis

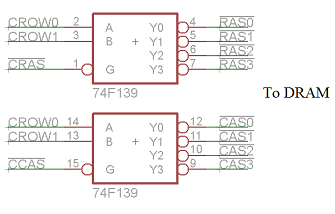

CROW0, 1 - dua bit untuk memilih satu dari empat baris

/ CRAS - jalur alamat sinyal strobo dari RAM dinamis

/ CCAS - alamat kolom sinyal gating dari RAM dinamis

FR / W - izin menulis dalam RAM, sinyal ini membutuhkan pemrosesan tambahan, lihat di bawah

D0-D7 - bus data, terhubung langsung ke jalur input / output dari chip RAM

/ CSEL - unit logis muncul pada baris ini ketika membaca dari RAM, itu harus dibalik dan diumpankan ke input / OE dari chip RAM

MSIZE - memberi tahu komputer volume baris: satu - 256 kB, nol - 1 MB, di sini baris ini terhubung ke kabel biasa

14M, PH2CLK, A10-A15 - tidak terlibat dalam dewan yang diusulkan

Sinyal / CRAS dan / CCAS harus didemultipleks untuk mendapatkan sinyal terpisah / RAS dan / CAS untuk setiap saluran. Untuk ini, chip 74F139 cocok (selanjutnya dipahami bahwa tidak akan ada chip terpisah di papan, alih-alih mereka akan ada satu FPGA umum).

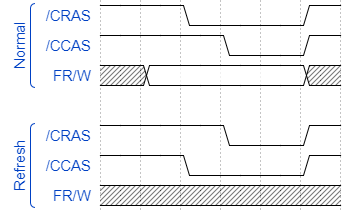

Sinyal FR / W tidak dapat diumpankan langsung ke input / WE dari chip RAM dinamis, dan inilah sebabnya. Dalam operasi baca-tulis normal, garis / RAS pertama menjadi aktif (yang sesuai dengan nol logis), kemudian garis / CAS. Selama siklus regenerasi RAM dinamis, sebaliknya, garis / CAS menjadi aktif terlebih dahulu, kemudian / RAS menjadi aktif. Tetapi chip yang digunakan mengharuskan unit muncul pada baris / WE sebelum baris / RAS menjadi aktif. Dan sinyal FR / W yang berasal dari Apple IIgs tidak memenuhi persyaratan ini. Keadaan FR / W selama siklus regenerasi tidak ditentukan. Oleh karena itu, diperlukan sirkuit yang mendeteksi siklus regenerasi dan mengumpankan unit ke / WE.

Langkah pertama adalah mengidentifikasi siklus regenerasi. Di bawah ini adalah bagan waktu:

Gagasan penulis adalah menggunakan kait "transparan". Sinyal / CRAS untuk itu adalah sinyal input, / CCAS adalah sinyal kait. Ketika unit aktif / CCAS, perangkat akan melewati sinyal input dengan sendirinya: status output berubah setelah status input. Ketika / CCAS beralih dari satu ke nol, kait mengingat sinyal pada input, dan sekarang tidak berubah pada output. Dalam operasi baca / tulis normal pada / CRAS, nol ada pada saat beralih / CCAS dari satu ke nol. Dan selama siklus regenerasi pada / CRAS, ada satu juga saat switching / CCAS ke nol. Kemudian, ketika / CCAS beralih kembali ke satu, kait menjadi transparan lagi. Ini mengingatkan bunga fantastis dari "Rahasia Planet Ketiga", yang bisa menjadi "cermin" dan "kamera".

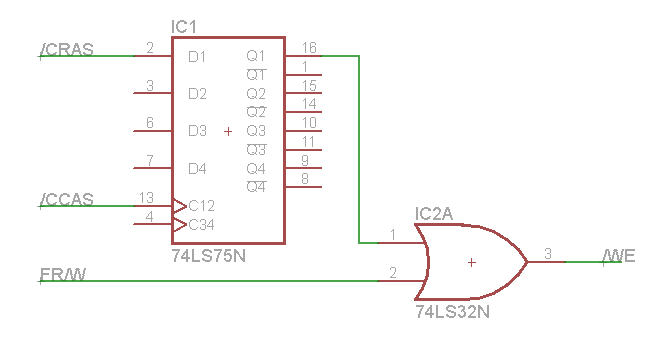

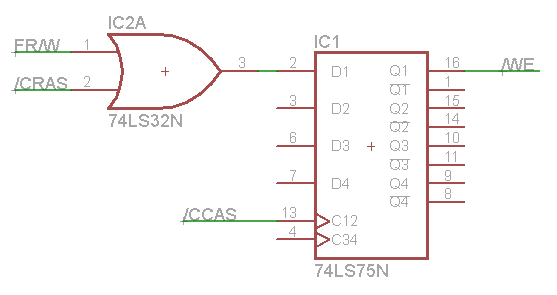

Pada awalnya, penulis membuat skema berikut:

Tetapi untuk transfernya ke GAL22V10 FPGA, diperlukan dua pin output. Karena itu, skema harus disederhanakan. Selama operasi normal, sinyal FR / W mengambil nilai yang diinginkan hingga mengklik, jadi ini juga memungkinkan.

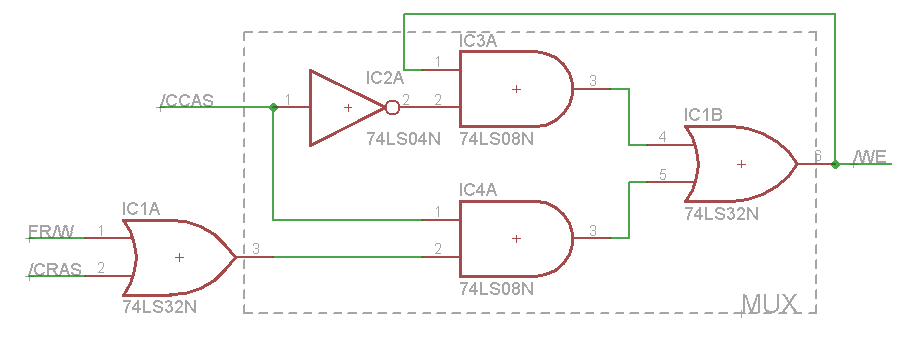

Kait "transparan" dapat dibuat dari multiplexer, dan pada gilirannya, dari elemen logika. Skemanya menjadi seperti ini:

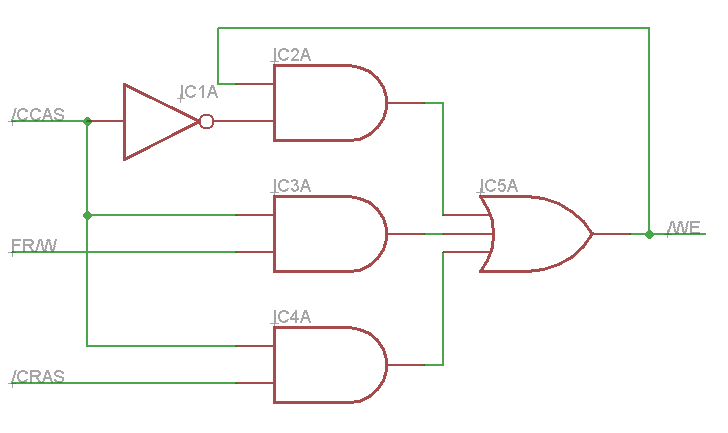

Dan setelah penyederhanaan - seperti ini:

Opsi ini ditransfer ke FPGA. Untuk kompilasi, penulis menggunakan WinCUPL. Program ini ada di situs web Atmel. Itu mentah dan terus-menerus terbang, tetapi berhasil dengan tugas dengan sempurna. Programmer - Genius G540.

Jumper SJ1 di papan bertindak seperti ini. Jika pin 1 dan 2 terhubung, sinyal / OE melewati FPGA. Jika pin 2 dan 3 terhubung, terhubung ke kabel biasa. Penulis tidak yakin bahwa skema untuk mengidentifikasi siklus regenerasi akan berfungsi. Oleh karena itu, ia menambahkan jumper ini jika konfigurasi FPGA harus diulang.

Karena semuanya bekerja, Anda tidak perlu menyolder pin, cukup sambungkan terminal 1 dan 2 dengan setetes solder.

Untuk mengurangi ukuran papan, penulis menerapkan satu kapasitor daya untuk setiap empat chip RAM, dan menempatkan chip itu sendiri di kedua sisi papan.

Microchip dalam kasus SOJ sulit disolder, dan terutama solder, dengan besi solder. Penulis merekomendasikan untuk menggunakan pengering rambut.

Perluas chip dengan benar. Pada intinya mereka terbalik. Pin 1 melihat ke bawah.

Beberapa lubang terlalu dekat dengan bantalan. Jangan korsleting dengan solder.

Dan platform 1 dan 2 untuk jumper, sebaliknya, tutup.

Kapasitor C1 - C3 memiliki kapasitansi 0,1 μF, C4 - 10 μF.

Penulis memesan papan di OSH Park. Lapisan ENIG diterapkan - emas, tetapi sangat tipis. Kartrid permainan tidak cocok - dengan cepat akan dihapus. Dan di sini papan ditempatkan di slot sekali dan lebih banyak tidak dihapus dari sana.

Penulis mengucapkan terima kasih kepada

GGLabs untuk rangkaian papan yang serupa, itu banyak membantu, terima kasih!

Sirkuit yang telah selesai ternyata seperti ini:

File:

Firmware FPGA GAL22V10 , program WinCUPL versi 5.30.4 diterapkan

Perangkat lunak

Board , Eagle versi 7.1 diterapkan

Garis besar PDFMenghasilkan!