Saya menyambut semua orang.

Mengikuti jejak artikel sebelumnya tentang penganalisis logis tentang Habré, saya memutuskan untuk menyelesaikan pekerjaan "fundamental" saya.

Saya akan mulai sedikit dari jauh.

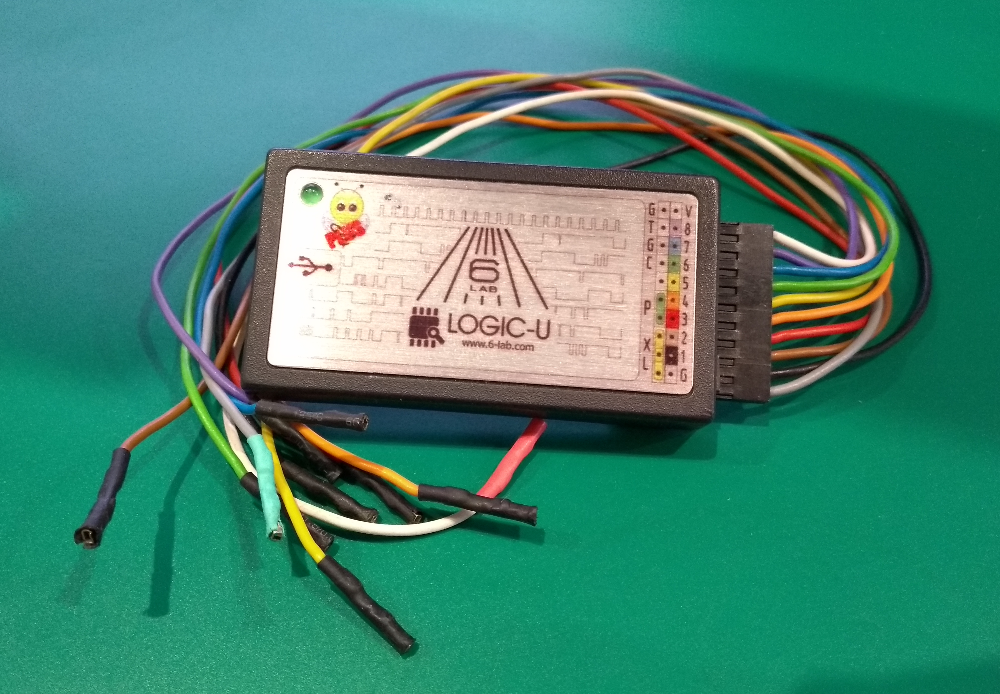

Semuanya dimulai pada awal 10-an, ketika saya pertama kali mengetahui tentang Saleae Logic (selanjutnya disebut Saleae yang saya maksud adalah penganalisa 8-channel tanpa slider) di beberapa forum radio amatir.

Mencatat. Tetapi sudah pada usia 13 dalam proses implementasi proyek lain saya menemukan fakta bahwa saya benar-benar membutuhkan penganalisa logika dengan buffer besar. Osiloskop dan hanteck la-5034 yang tersedia pada saat itu tidak menyelesaikan masalah.

Fitur utama Saleae dan klonnya adalah tidak adanya buffer bawaan - seluruh aliran segera dikejar ke PC dan disimpan di sana. Kemudian dapat dianalisis, diterjemahkan dan diekspor. Di satu sisi, kami secara praktis tak terbatas dalam melihat (data dapat disimpan selama berjam-jam), di sisi lain, frekuensi pengambilan sampel maksimum adalah 24 MHz. Dalam kebanyakan kasus, cukup, bagaimanapun, karena sifat programatik sampling, sampel memiliki "jitter" yang nyata.

Akibatnya, sangat cepat, dalam waktu sekitar satu hari, dari Kharkov, dari 6-lab (sekarang sudah meninggal), mereka mengirim saya melalui klon klon saleae mereka dengan dua eeprom yang sudah dibangun untuk mengganti jenis saleae dan xbee (perangkat keras perangkat ini sama-sama hanya berbeda: pid yang di-flash dalam eeprom).

Dengan demikian, Anda dapat menggunakan perangkat lunak dari kedua produsen.

Saat itulah saya menjadi tertarik pada hal seperti Y7C68013A, baik, atau lebih pendek dari FX2 (meskipun lebih tepat daripada FX2LP).

Ini adalah mikrokontroler yang kompatibel dengan 8.051 dengan port USB2.0 hardware dan jujur 480Mb / s.

Fitur termasuk: 16KB RAM dan kemampuan untuk mengunduh firmware baik dari EEPROM I2C yang terhubung dan melalui USB (tidak ada flash built-in di sana).

Dan MK ini dapat berpura-pura menjadi perangkat apa pun di USB-bus (dalam arti menanggapi VID: PID).

Beberapa detail dari lembar data tentang prosedur pemuatan

Pertimbangkan kasus ketika EEPROM I2C terhubung ke MK.

Dalam hal ini, 8 byte pertama dianalisis darinya:

Jika byte pertama adalah 0xC0 (seperti dalam firmware klon Saleae), maka MK mengkonfigurasi port USB dengan VID: PID yang ditentukan dalam 1-4 byte dan menunggu firmware diunduh melalui USB. Bergantung pada VID yang di-flash: PID MK dapat "menjadi" perangkat yang berbeda, setidaknya Saleae setidaknya Xbee setidaknya oleh seseorang. Sangat nyaman Anda dapat menyolder EEPROM dalam tumpukan dan memilih dengan jumper.

Tetapi jika byte pertama adalah 0xC2, kemudian dimulai dengan 9 byte, firmware untuk MK harus disimpan dalam EEPROM, yang akan dimuat ke dalam RAM dan mulai dijalankan.

Format penyimpanan mirip dengan HEX Intel:

Artinya, firmware dibagi menjadi beberapa blok yang secara individual dimuat ke bagian memori yang berbeda. Dan karenanya, tidak masuk akal untuk menyimpan area kosong.

Dan sekarang kita dengan lancar mendekati karakter utama dari artikel kami DreamSourseLab.

Saya tidak akan menceritakan kembali keseluruhan cerita (saya tidak benar-benar mengetahuinya dan tidak melihat secara mendalam) Ini adalah tiga insinyur yang, melalui crowdfunding, melihat proyek penganalisa mimpi yang logis (hampir).

Apa yang mereka lakukan.

Mereka menambahkan ke FX2 sebuah plisina murah - Spartan 6 (mungkin memata-matai Saleae).

Dan ini adalah 16 saluran sekaligus, ini adalah titik pengambilan sampel yang jelas, ini adalah kemampuan untuk mengemas bit individual (dua baris dapat disampel 4 kali lebih sering daripada 8, hal utama adalah tetap berada dalam bandwidth USB). Ini adalah kesempatan untuk menyimpan ke buffer pada frekuensi tinggi (400 MHz / 4 saluran, 200 MHz / 8 saluran, 100 MHz / 16 saluran), dan kemudian secara perlahan mentransfernya ke PC. Dan jika Anda mengacaukan sigrok dengan basis protokol terkode yang paling kuat. Secara umum, proyek ini dipecat - semua orang senang. Dan dengan mempertimbangkan fakta bahwa penulis menyimpan mode aliran (tanpa menyimpan ke buffer internal), kami mendapat penganalisa mimpi yang logis (well, hampir karena saya langsung ingin 32 saluran dan FX3).

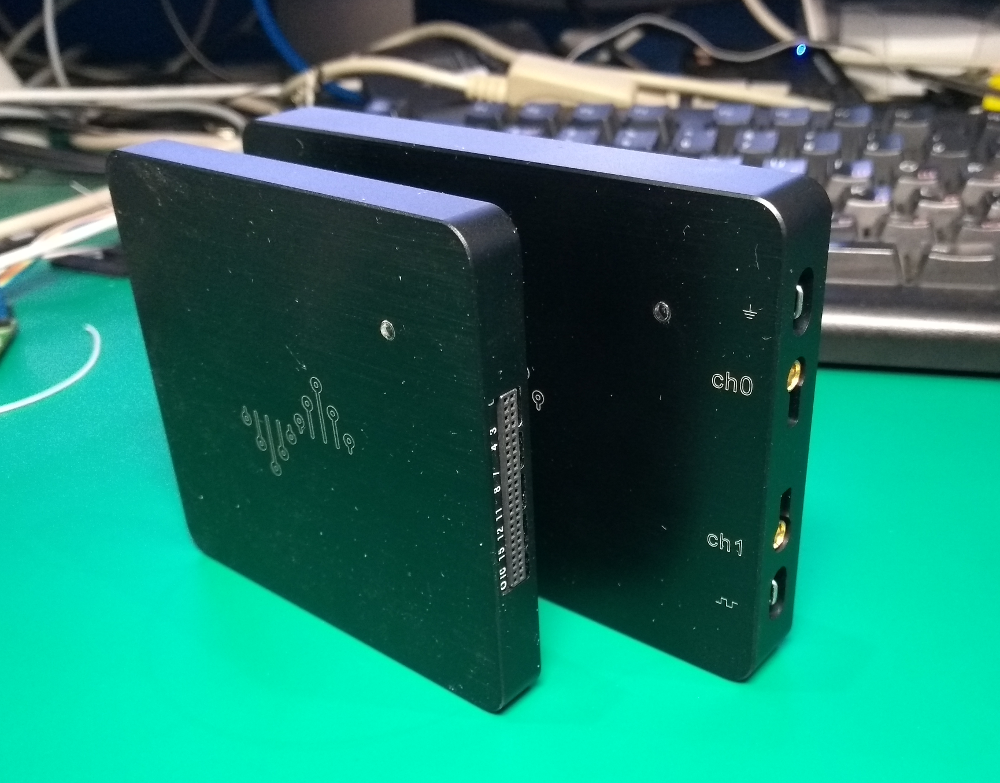

Maka muncullah DSLogicPro. Kotak aluminium hitam ketat dengan konektor USB-C.

Dan kemudian para insinyur memulai bisnis. Dan mereka merilis kotak dengan nama DSLogicBase dan DSLogicPlus (seperti yang saya pahami untuk menaklukkan dunia melalui situs Cina), serta DSCope (kami menggantung beberapa ADC 8-bit dan sekarang kami memiliki osiloskop dua saluran).

Nah, untuk menjaga proses ini di bawah kendali ketat, kami mengubah tata letak papan sedikit. Artinya, DSLogicPlus dan DSLogicPro identik secara elektrik dan fungsional, tetapi SRAM tergantung pada colokan pada pin lainnya (ini terlihat jelas pada gambar trek). Saya menduga bahwa perbaikan telah dilakukan di tempat lain.

Omong-omong, revisi yang sangat berharga dilakukan dalam hal kabel untuk menghubungkan sinyal yang dipelajari. Jika dalam Pro semua 16 saluran terhubung sekaligus dengan satu konektor lebar, maka dalam Plus, semua kabel dibagi menjadi kelompok 4 saluran yang dapat dihubungkan secara terpisah. Nah, kabel itu sendiri pendek, koaksial dan di tempat pemotongan (di mana koaksial dibagi menjadi sinyal terpisah dan kabel umum) ada syal kecil dengan filter.

Maka, pada musim semi 17, saya memesan DSLogicBase di China (sayangnya, saya tidak tahu semua yang saya tulis tentang itu). Mereka mengirimi saya segalanya, tetapi menantikan penyangga yang cukup besar, saya membuka papan dan melihat tempat kosong. Dengan cepat menaikkan butchu mengembalikan 50% dari biaya. Dan kemudian dia mulai mempelajari pertanyaan untuk mengubah Base saya menjadi Plus. Inilah tepatnya perbedaan antara Base dan Plus - keberadaan buffer terpisah. Basis menggunakan memori yang tertanam dalam FPGA.

Pada musim panas 17, dalam perjalanan untuk bekerja dan kembali selama setengah jam di kereta PKS, saya mempelajari masalah ini. Dan cukup cepat menjadi jelas bahwa perbedaannya hanya dalam SRAM disegel dan sepasang byte EEPROM firmware.

Sedikit tentang apa yang ada di direktori DSView / res

Di sana kami memiliki satu set file dengan ekstensi bin dan fw.

bin - ini adalah firmware untuk plisina. Mereka dimuat pada saat memulai program melalui fx2.

fw adalah file firmware biner untuk FX2.

Jika Anda membandingkan semua file fw dari itu ternyata mereka semua berbeda hanya dalam byte PID pada alamat di dekat akhir.

Artinya, perbedaan antara semua perangkat hanya ini dan firmware dari plug (yang, seperti yang saya katakan, dimuat pada saat inisialisasi).

Perbandingan fw dengan apa yang tertulis di EEPROM (tentu saja, saya langsung membuang dump dari analisa saya) menunjukkan bahwa firmware yang digunakan ada di sini.

Jika Anda menggunakan firmware dari EEPROM, maka (sejauh yang saya ingat) mereka akan cocok (untuk perangkat lunak versi 0.96).

Jadi, seperti yang sudah ditulis di hub, Anda hanya perlu menyolder memori dan mengubah 2 byte di firmware (di header dan kemudian di firmware).

Dengan cara yang sama, DSCope diselesaikan, kami menggandakan memori dan mengubah PID di EEPROM.

Ada satu lagi nuansa.

Ketika versi perangkat lunak baru dirilis (0.96-0.99), model perangkat keras yang didukung ditambahkan dan PID dari model ini diubah.

Jadi saya mendapat tablet seperti itu:

Selain itu, beberapa indikasi muncul di firmware di alamat 0x20 untuk versi Pro ada 5, untuk Base dan Plus ada 6. Kemungkinan besar ini hanya versi papan sirkuit cetak.

Ngomong-ngomong, ada cara lain untuk memurnikan. Tidak diperlukan pemrograman ulang EEPROM. Cukup untuk menyolder SRAM, dan kemudian, ketika mengkompilasi libsigrok4DSL, buat koreksi ke file libsigrok4DSL / hardware / DSL / dsl.h:

Dalam struktur yang menggambarkan peralatan statis, struct struct DSL_profile didukung_DSLogic [],

di tempat di mana DSLogic PLus dan Base dijelaskan, ubah bidang PID sehingga program berpikir bahwa Base PID adalah 20 dan Plus PID adalah 21.

319 {0x2A0E, 0x0020, "DreamSourceLab", "DSLogic PLus", NULL, 320 "DSLogicPlus.fw", 321 "DSLogicPlus.bin", 322 "DSLogicPlus.bin", 323 {CAPS_MODE_LOGIC, 324 CAPS_FEATURE_VTH | CAPS_FEATURE_BUF, 325 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 326 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 327 SR_MB(256), 328 0, 329 DSL_BUFFER100x16, 330 0, 331 0, 332 DSL_STREAM20x16, 333 SR_MHZ(1), 334 SR_Mn(1), 335 0, 336 0} 337 }, 338 339 {0x2A0E, 0x0021, "DreamSourceLab", "DSLogic Basic", NULL, 340 "DSLogicBasic.fw", 341 "DSLogicBasic.bin", 342 "DSLogicBasic.bin", 343 {CAPS_MODE_LOGIC, 344 CAPS_FEATURE_VTH, 345 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 346 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 347 SR_KB(256), 348 0, 349 DSL_STREAM20x16, 350 0, 351 0, 352 DSL_STREAM20x16, 353 SR_MHZ(1), 354 SR_Mn(1), 355 0, 356 0} 357 },

Dan versi analisa Anda dengan versi DSView ini akan berfungsi seolah-olah Anda memiliki Plus nyata.

Sementara itu, saya akan bermimpi tentang sekelompok Spartan6 + FX3 + DSView.