Sarapan bersama Charles Weatherly, penulis buku kultus Etudes for Programmers, berlangsung empat jam. Pada akhirnya, pelayan meminta kami dari sebuah restoran di Palo Alto, mengatakan bahwa ada antrian panjang di restoran, dan kami duduk di sini dari jam delapan pagi. Selama waktu ini, kami membahas banyak hal menarik: Pekerjaan Charles di Laboratorium Livermore dan Oracle, pemrograman berorientasi objek dan fungsional, kompiler dan bahasa deskripsi perangkat keras, bookmark ke prosesor, inefisiensi jaringan saraf dan Prolog yang tak terlupakan, kunjungan Charles ke Rusia, pemrosesan teks dengan mesin negara dalam coprocessor perangkat keras dan pembuatan video game di FPGA oleh anak sekolah.

Isi empat jam dengan Charles Weatherly sudah cukup untuk lima puluh artikel tentang Habré, oleh karena itu saya akan mendaftar terutama topik, setelah itu saya akan memberikan beberapa rincian tentang tiga di antaranya:

- Pemrograman berorientasi objek dan fungsional. Tugas tunggal, nilai fungsi, singkirkan mutasi, singkirkan waktu.

- Struktur data dan algoritma kompiler. Muchnik SSA dan buku tentang optimasi. Bob Morgan (Kompas) membangun kompiler pengoptimal. Penyusun vektor dan Randy Allen (kolega Wave saya dan kolega Charles tentang perusahaan lain).

- Evolusi parser Yacc, internal bahasa Ada (DIANA), dan frontend VHDL di Synopsys.

- Tata bahasa atribusi dan tidak berhasil, menurut pendapat saya, penggunaannya dalam manual pelatihan MIPT tentang Teori Implementasi Bahasa Pemrograman (TRNP).

- Bahasa pemrograman JOVIAL dan standardisasi Ada. Bahasa IDL.

- Pemrograman di Livermore Computing Laboratory untuk fisikawan dan kimiawan di CDC 7600 dan Cray-1. Livermore Fortran adalah perpanjangan dari Fortran-77 dengan struktur dan alokasi memori dinamis. Penggunaan microfiches, termasuk untuk pencarian dan produksi animasi secara otomatis. Harry Nelson Dan bagaimana Rubik's Cube masuk ke laboratorium sebelum diketahui.

- Klon Soviet Cray-1 Electronics SS BIS. Kompiler Fortran di IPM dan kompiler C yang kami kerjakan di MIPT.

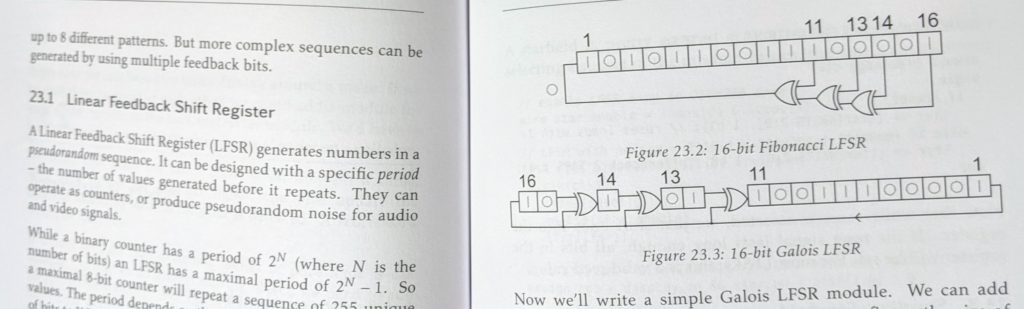

- Membalikkan rekayasa generator nomor acak di Synopsys VCS. Generator kongruensial dengan register shift. LSFR.

- Inefisiensi jaringan saraf dan bahasa Prolog yang tidak dapat dilupakan.

- Penerapan metode dari Prolog untuk analisis statis teks program.

- Termasuk analisis kode prosesor yang ditulis dalam Verilog atau VHDL untuk menemukan bookmark di dalamnya. Bookmark yang tersebar di berbagai bagian deskripsi prosesor di tingkat transfer register. Menemukan kode "berlebihan" yang melakukan sesuatu di luar spesifikasi. Sebagai contoh, mesin keadaan terbatas yang sedang menunggu frase kunci, teks dalam register terlihat oleh programmer, setelah itu prosesor beralih ke mode privilege.

- Metode analisis kode hibrid - eksekusi dinamis dengan penyelidikan statis selanjutnya dari ruang keadaan dari titik eksekusi tertentu.

- Daftar Hakmem dari MIT.

- Sebagian besar programmer dalam hidup hanya menggunakan lima algoritma - pengurutan cepat, pencarian biner, hashing, penyisipan daftar, dan yang lainnya (penyisipan pohon biner AVL?).

- Sejarah truf Unix di Bell Labs.

- Pekerjaan Charles Wazerell di Oracle pada SQL.

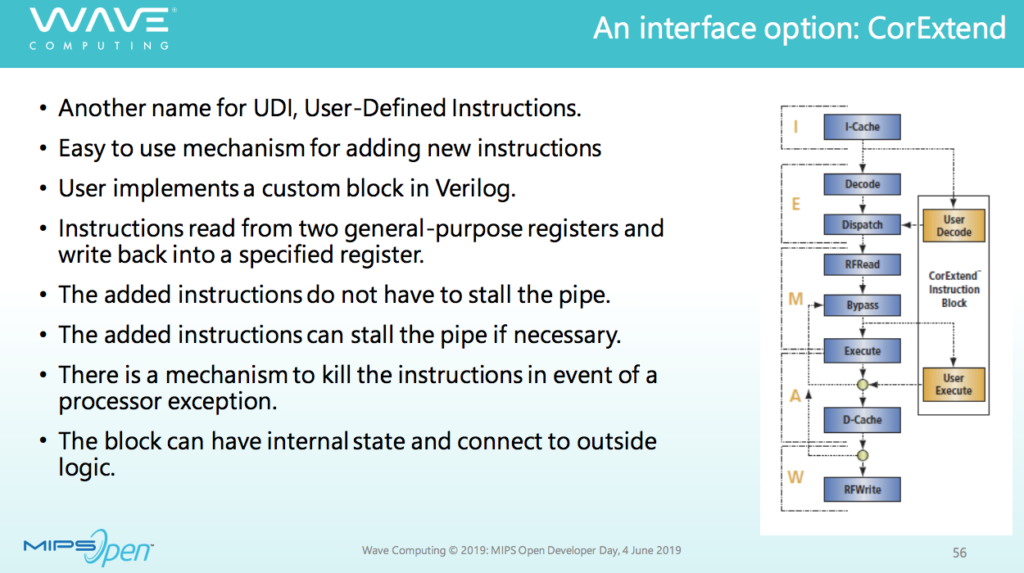

- Contoh yang baik menggunakan coprocessor perangkat keras untuk MIPS CorExtend / UDI adalah Instruksi yang Ditetapkan Pengguna. Menambahkan instruksi ke prosesor untuk analisis leksikal cepat, dengan mesin status di dalam coprocessor dan mempertahankan status di antara instruksi individual. Latar belakang sejak tes terjemahan IBM / 360 dan CDC STAR.

- Menggunakan coprocessor perangkat keras untuk membersihkan aliran data sebelum menerapkan algoritme pembelajaran mesin.

- Game Rogue, Scientific American di negara bagian dan Uni Soviet.

- Summer School of Young Programmer di Novosibirsk dan nyamuk di dalamnya (sesuai dengan ingatan dan kisah rekan-rekan saya, Charles Weatherly)

- Bagaimana Charles menghabiskan 36 jam di Moskow dan dua minggu di St. Petersburg. Pertapaan. Di universitas St. Petersburg, ia tidak memberikan kuliah.

- Dia menyarankan Charles untuk pergi ke sekolah musim panas di MIET / Zelenograd pada bulan Juli atau di tempat lain di musim gugur (Universitas Negeri Moskow? MIPT? ITMO?).

- Pendidikan untuk anak sekolah dan siswa yang lebih muda. Kebutuhan untuk keluar dari template (misalnya, pemrograman berurutan) dan mempelajari Verilog di FPGA sebagai salah satu cara untuk keluar dari template tersebut.

- Penggunaan sirkuit mikro dengan tingkat integrasi kecil sebelum latihan FPGA, sehingga anak sekolah atau siswa secara intuitif memahami bahwa kode Verilog adalah deskripsi sirkuit elektronik, bukan program (rangkaian instruksi).

- Contoh untuk RTL pada FPGA untuk sekolah musim panas di MIET / Zelenograd pada bulan Juli adalah mesin negara terbatas belajar mandiri yang menghitung tren lawan dalam permainan "gunting kertas batu".

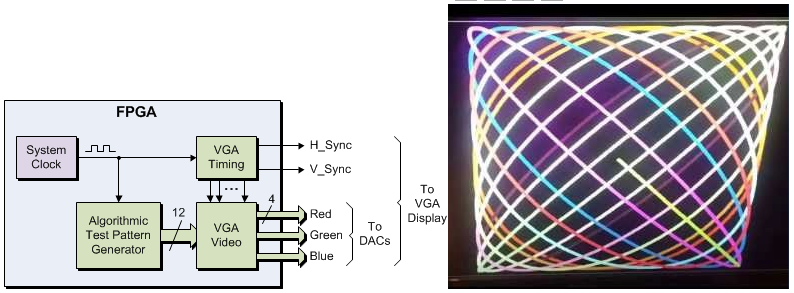

- Contoh lain adalah kompetisi mesin negara terbatas (hewan) yang memindahkan pemain ke tujuan di peta (bola dunia). Objek pada peta memiliki "bau" - positif (makanan) atau negatif (listrik yang dapat menyerang). Mendesain kartu dalam FPGA, output dan sprite pemain pada VGA menggunakan modul generasi pemindaian.

Di sini kami memeriksa perselisihan terbaru tentang Habré tentang OOP. Charles berkampanye untuk OOP dan pemrograman fungsional, jika ada. Saya menunjukkan kepada Charles

contoh yang saya lihat dalam dua proyek

desain kelas yang gagal untuk mewakili node dari pohon parsing dan optimisasi pada pohon ini , setelah itu Charles mengatakan bahwa tentu saja, algoritma transformasi pohon tidak boleh tersebar ke kelas-kelas kecil dengan cara ini, tetapi sebaliknya, pohon parsing seharusnya dengan cepat melempar grafik aliran kontrol, yang digunakan untuk menggunakan transformasi didorong tabel berdasarkan penugasan tunggal statis, dengan beberapa pengecualian. Charles memberi tahu saya tentang vektorisasi Muchnik, Bob Morgan, dan Randy Allen:

Kemudian saya memberi tahu Charles bahwa lusa kami akan mengadakan

seminar di Las Vegas pada konferensi otomatisasi desain elektronik , dan saya membutuhkan nasihatnya tentang contoh yang baik dari co-prosesor yang didasarkan pada protokol CorExtend / UDI - Instruksi yang Ditetapkan Pengguna. Protokol ini digunakan dalam core MIPS. CorExtend / UDI memungkinkan Anda untuk menanamkan sebuah blok di prosesor yang menerjemahkan dan mengeksekusi instruksi tambahan ke sistem instruksi utama yang dapat ditentukan oleh perancang sistem pada sebuah chip. Blok dapat disintesis dan menjadi bagian dari sirkuit mikro atau dikonfigurasi dalam FPGA / FPGA.

Instruksi tambahan bergerak di sepanjang pipa prosesor bersama dengan yang utama. Mereka menerima data dari register umum yang terlihat oleh programmer dan dapat mengembalikan hasilnya ke register. Instruksi ini juga dapat menyimpan beberapa status di coprocessor. Mereka dapat dibunuh oleh pengecualian jika pengecualian terjadi, misalnya, dalam pipa mengikuti instruksi ini:

Lusa, dalam

presentasi di seminar, saya akan menggunakan contoh dengan instruksi konvolusi sederhana untuk jaringan saraf. Tetapi akselerasi yang dicapai dalam kasus ini tidak mengesankan - hanya dua kali. Apakah mungkin membuat contoh yang lebih baik?

Charles segera datang dengan contoh yang jauh lebih baik: analisis leksikal perangkat keras. Mesin negara dapat ditempatkan di coprocessor, yang akan menentukan angka, pengidentifikasi dan komentar dalam aliran teks. Ini akan menghemat dengan menyimpan keadaan antara perintah individu yang mengirimkan teks dari register ke mesin. Hasil analisis saat ini (teks yang ditandai) juga akan dikembalikan ke register.

Charles juga menceritakan kisah tentang instruksi untuk parsing teks sejak tes terjemahan IBM / 360 dan CDC STAR. Dia juga mengatakan kepada saya bahwa coprocessor tersebut dapat digunakan untuk pembelajaran mesin, untuk pra-pembersihan aliran data sebelum menerapkan algoritma pembelajaran mesin untuk itu.

Kemudian saya memberi tahu Charles Saga bagaimana sekelompok insinyur dan guru menerjemahkan dan mengimplementasikan di berbagai universitas Rusia

buku pelajaran David Harris dan Sarah Harris "Sirkuit digital dan arsitektur komputer" (lihat posting di Habr.

1 ,

2 ,

3). Sekarang, dengan upaya gabungan MIET, RUSNANO, guru-guru MEPhI dan universitas lain, kami merencanakan sekolah musim panas di MIET di mana anak sekolah lanjutan memproyeksikan video game di FPGA dengan output ke layar grafis (bagian

Antara fisika dan pemrograman ). Untuk ini, ide-ide dari buku Merancang Video Game Hardware di Verilog oleh Steven Hugg, 15 Desember 2018 digunakan:

Game dapat dikembangkan baik dalam bentuk mesin negara hingga perangkat keras murni, atau dalam kombinasi grafis perangkat keras pada FPGA dengan program pada prosesor inti schoolMIPS, yang dijelaskan dalam

posting oleh Stanislav Zhelnio tentang Habr dan

wiki di schoolMIPS di GitHub . Pada FPGA, Anda dapat dengan mudah

menghasilkan pemindaian untuk VGA , menampilkan kartu dari memori dan memindahkan sprite dengan angka:

Charles menyarankan, selain permainan dengan tank dan balapan, untuk membuat kompetisi automata terbatas (hewan) yang menggerakkan pemain ke gawang di peta (globe). Objek pada peta memiliki "bau" - positif (makanan) atau negatif (listrik yang dapat menyerang). Murid dapat menulis mesin hingga pada veril yang melihat lingkungan, menanamkannya dalam kode yang menggambar grafik dan mendukung peta, dan kemudian bersaing dengan siapa yang lebih baik:

Untuk menghasilkan elemen perilaku pseudo-acak, Anda dapat menggunakan blok perangkat keras LFSR:

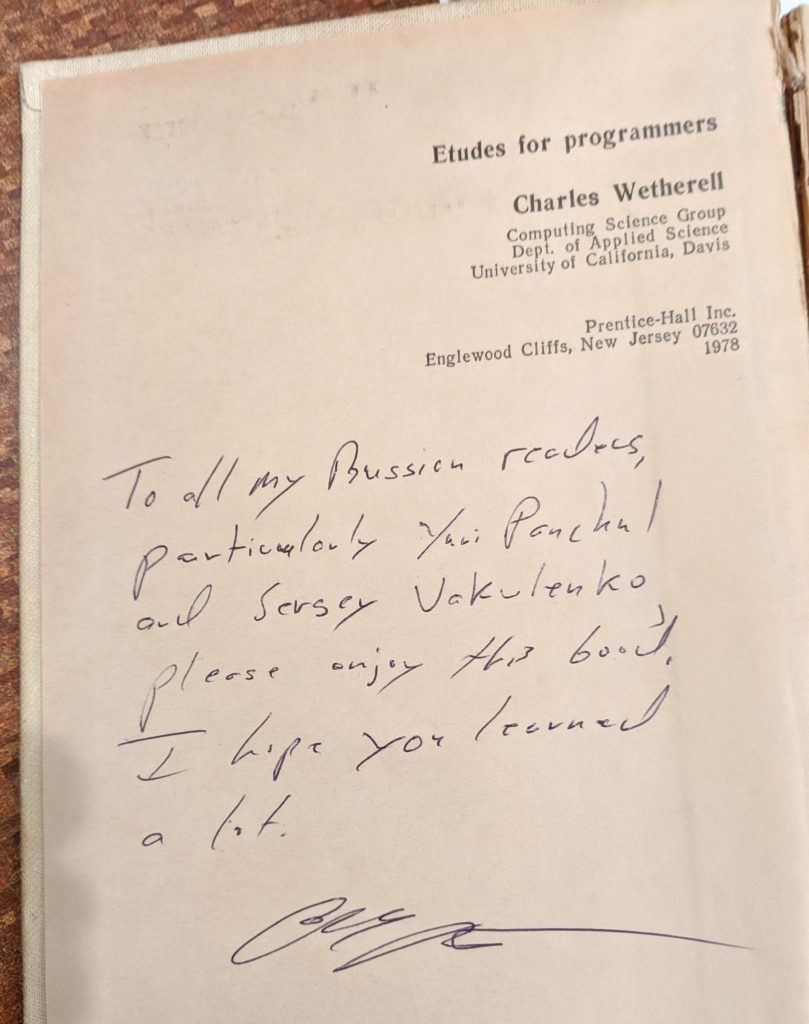

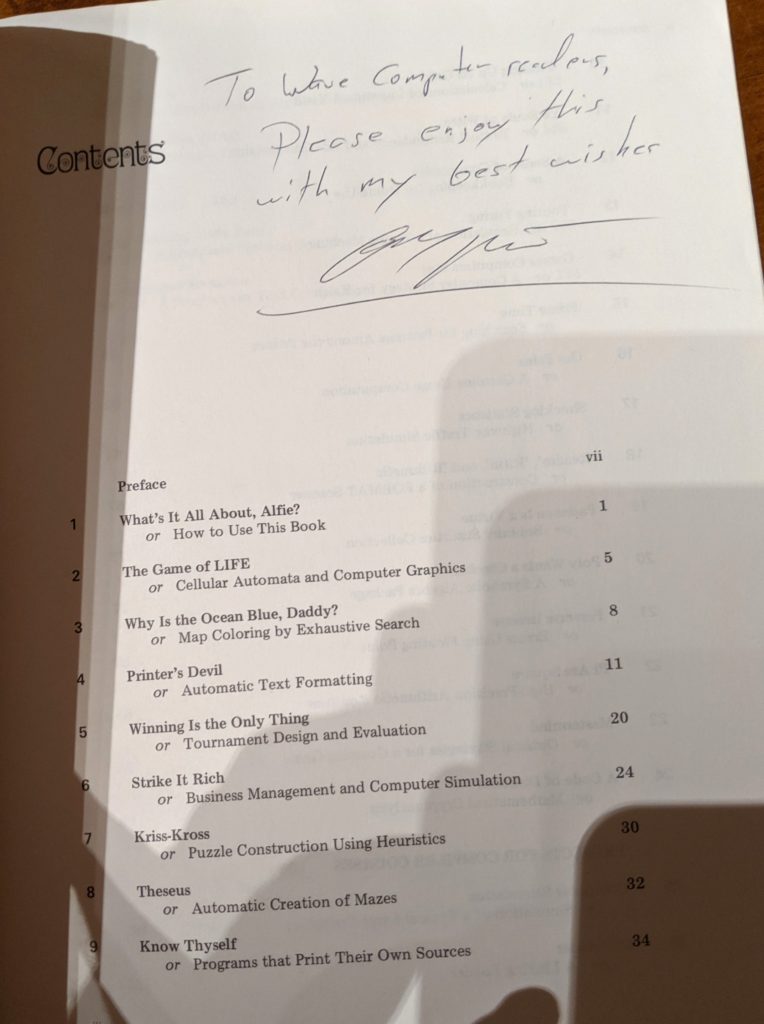

Pada akhirnya, Charles meninggalkan dua tanda tangan - untuk pembaca Rusia (saya meminjam buku Rusia dari

Sergey Vakulenko ) dan pembaca di perusahaan kami Wave Computing, dari perpustakaan internalnya saya meminjam buku asli dalam bahasa Inggris: