Pada bagian

pertama, kami secara singkat memeriksa fisika silikon, teknologi mikroelektronika, dan keterbatasan teknologi. Sekarang mari kita bicara tentang batasan fisik dan efek fisik yang mempengaruhi ukuran elemen dalam sebuah transistor. Ada banyak dari mereka, jadi mari kita lihat yang utama. Di sini Anda harus masuk ke fisika, jika tidak, tidak ada.

Penafian: Suatu

ketika saya berkecimpung dalam menulis artikel tentang

pembuatan chip , dan

dalam seri artikel "Inside Look" saya bahkan melihat ke dalamnya, yaitu: Topiknya sangat menarik bagi saya. Secara alami, saya ingin penulis artikel asli untuk menerbitkannya di Habré, tetapi sehubungan dengan pekerjaan, ia mengizinkan saya untuk mentransfernya di sini. Sayangnya, aturan Habr tidak memperbolehkan copy-paste langsung, jadi saya menambahkan tautan ke sumber, gambar dan sedikit lelucon dan mencoba meluruskan teks sedikit. Ya, dan saya tahu dan menghormati artikel (

1 dan

2 ) tentang topik ini dari

amartologi .

Efek fisik dalam mikroelektronika

Urutan jumlah dasar untuk silikon

Konsentrasi atom silikon dalam kristal adalah 10

22 cm

-3Konsentrasi elektron dan lubang intrinsik pada suhu kamar - 10

10 cm

-3Konsentrasi atom pengotor dari daerah yang didoping ringan - 10

16 -10

18 cm

-3Konsentrasi atom pengotor dari daerah yang sangat diolah - 10

19 -10

20 cm

-3Konsentrasi atom pengotor di daerah yang sangat diolah adalah 10

21 cm

-3 . Dalam hal ini, seseorang telah berbicara tentang

semikonduktor yang merosot , karena konsentrasi seperti itu (satu atom pengotor per 10 atau kurang atom silikon) mengubah struktur energi kristal.

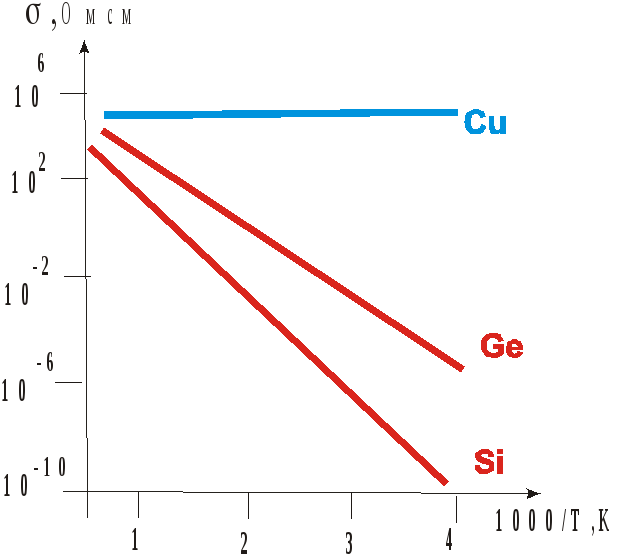

Ketergantungan suhu karakteristik silikon

Dari bagian pertama kita ingat bahwa pada suhu kamar silikon murni adalah dielektrik. Sepasang lubang elektron muncul hanya dalam satu dari satu triliun kasus, tetapi fraksi ini meningkat secara eksponensial dengan meningkatnya suhu. Ada hal seperti itu - suhu menggandakan konsentrasi pembawa muatan sendiri. Untuk silikon, sekitar 9 derajat.

Yaitu meningkatkan suhu sebesar 9 derajat, persentase atom silikon yang membusuk meningkat 2 kali lipat; 18 derajat - 4 kali; 27 derajat - 8 kali; 36 derajat - 16 kali; 45 - 32 kali; 90 - 1024 kali; 180 - 10

6 kali; 270 - 10

9 kali.

Perbandingan konduktivitas termal dari tembaga, silikon dan germanium. Sumber

Perbandingan konduktivitas termal dari tembaga, silikon dan germanium. SumberKami mendapatkan bahwa ketika dipanaskan hingga 200 derajat (~ 2.1 dalam grafik di atas), konsentrasi intrinsik pasangan lubang elektron menjadi 10

16 , yang sama dengan konsentrasi pengotor dari lapisan yang diolah secara ringan. Pada 300 derajat (~ 1,75) sudah 10

19 , ini adalah konsentrasi lapisan yang sangat diolah (n + dan p +). Pada suhu ini, silikon benar-benar berubah menjadi konduktor dan transistor kehilangan kendali.

Masalah akan dimulai jauh lebih awal. Suhu dalam chip tidak merata. Ada zona pemanasan lokal, biasanya di tengah chip. Jika suhu di area kecil melebihi 200 derajat, maka karena peningkatan konduktivitas intrinsik silikon, arus kebocoran mulai meningkat. Hal ini menyebabkan lebih banyak pemanasan, dan ini semakin meningkatkan arus bocor dan memperluas area overheating. Prosesnya menjadi ireversibel dan ... meledak. Dan tidak dapat dibatalkan. Oleh karena itu, pada semua sirkuit mikro besar, perlindungan otomatis terhadap panas berlebih diatur.

Itulah mengapa sangat penting untuk tidak membiarkan pemanasan yang kuat dari kristal.

Sebagai perbandingan, dalam gallium nitride pada suhu kamar, konsentrasi elektron dan lubang intrinsik beberapa kali lipat lebih rendah, dan suhu penggandaan jumlah pembawa muatan intrinsik sekitar 25 derajat. Masalah yang dijelaskan di atas dalam gallium nitride dimulai pada sekitar 600-700 derajat.

Terowongan saat ini

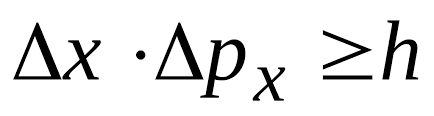

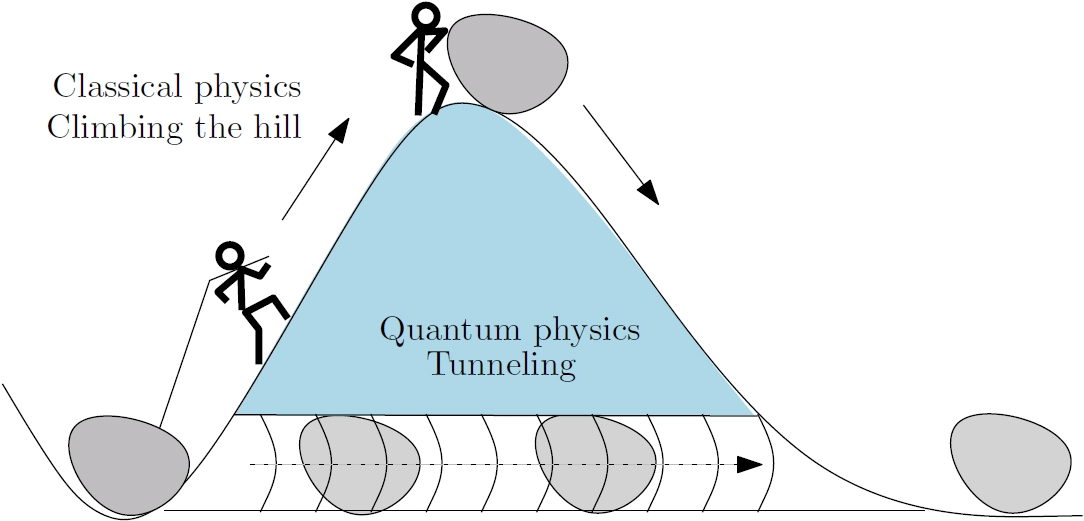

Fenomena ini kompleks dan sekaligus sederhana. Akar terletak pada sifat kuantum elektron. Sebuah elektron hidup berdasarkan hukum mekanika kuantum, yang tidak selalu dipahami dari sudut pandang fisika klasik. Menurut hukum-hukum ini, elektron tidak hanya partikel, tetapi juga gelombang, dan perilakunya dapat dihitung hanya dengan beberapa probabilitas. Ada formula Heisenberg seperti itu:

Ini juga disebut

hubungan ketidakpastian Heisenberg . Ini mengikuti dari rumus bahwa parameter spasial elektron tidak dapat ditentukan dengan akurasi lebih besar dari nilai tertentu (konstanta Planck). Dalam kasus ekstrim persamaan, jika kita mengetahui lokasi pasti elektron, kita tidak akan tahu apa-apa tentang kecepatan dan arah gerakannya. Jika Anda tahu kecepatan dan arahnya dengan tepat, maka tidak akan ada yang diketahui tentang keberadaannya. Ternyata elektron adalah partikel yang kabur di ruang angkasa dengan puncak probabilitas keberadaan. Setiap saat, sebuah elektron dapat berada di mana saja di Semesta tanpa pengaruh eksternal. Benar, kemungkinan kemunculannya sangat jauh dari lokasi saat ini yang semakin kecil.

Sekarang bayangkan struktur Logam - Dielektrik - Semikonduktor n-type (MIS). Dalam logam, konsentrasi elektron bebas kira-kira sama dengan konsentrasi atom (10

22 / cm

3 ). Mereka tidak dapat menembus ke dalam dielektrik, karena untuk elektron dari logam ini adalah wilayah energi terlarang. Di dalam dielektrik, gelombang elektron dengan energi seperti dalam logam akan mulai mengganggu (merusak diri sendiri). Tetapi mereka dapat terwujud dalam semikonduktor tipe-n, di mana bagi mereka ada zona energi yang diizinkan. Elektron berpindah dari logam ke semikonduktor melalui lapisan oksida tanpa pengaruh eksternal, hanya karena sifat probabilistiknya. Ini adalah

terowongan saat ini . Proses itu sendiri disebut tunneling, atau tunneling kuantum (terdengar lebih dingin!).

Energi tambahan yang harus ditambahkan ke elektron untuk penetrasi "klasik" ke dalam oksida disebut penghalang potensial. Secara skematis, sebuah elektron menggerogoti terowongan melalui penghalang potensial.

Ada aliran dalam arah yang berlawanan - dari semikonduktor ke logam. Tetapi karena konsentrasi elektron bebas dalam semikonduktor adalah beberapa urutan besarnya lebih rendah, arus balik secara proporsional lebih kecil.

Semikonduktor tipe-p untuk elektron dari logam juga merupakan band energi terlarang. Namun, proses sebaliknya dimungkinkan di sini - penerowongan elektron valensi dari semikonduktor ke logam dengan penampilan lubang di silikon. Sepertinya lubang terowongan dari logam. Intensitas, hal-hal lain dianggap sama, sekitar 10 kali lebih rendah daripada penerowongan elektron bebas.

Arus tunneling untuk jarak di atas 1 μm dapat diabaikan. Peluang dan transisi terlalu rendah. Ketika jarak menurun, probabilitas transisi spontan meningkat tajam. Pada jarak unit nm, arus tunneling tumbuh 10 kali ketika mendekati 0,2 nm.

Mekanisme serupa bekerja untuk lapisan silikon npn. Untuk elektron bebas dari n-region, p-region adalah pita energi terlarang, tidak ada transisi yang terjadi. Tetapi jika lebar p-base diatur terlalu sempit, elektron mulai terowongan langsung dari sumber ke tenggelam. Ini membatasi lebar dasar maksimum teoritis hingga 8 nm. Pada ukuran yang lebih kecil, karena arus tunneling, sumber - tiriskan transistor pada prinsipnya menjadi tidak terkendali.

Untuk struktur pnp, situasinya mirip, tetapi lubang (elektron valensi) terowongan.

Dalam semikonduktor yang merosot (sangat diolah) di pita energi terlarang ada pulau-pulau energi yang diizinkan. Bagi mereka, opsi penerowongan melalui pulau-pulau ini dimungkinkan. Tentang cara mengatasi arus dengan melompat di atas batu besar yang menempel.

Wilayah Biaya Ruang Angkasa (SCR)

Wilayah muatan ruang (SCR), juga merupakan daerah penipisan, juga merupakan wilayah muatan ruang - ini adalah lapisan bermuatan listrik yang terbentuk pada batas wilayah n dan p.

Hubungkan secara mental 2 buah silikon, satu tipe-n, tipe-p lainnya. Di lapisan-n ada banyak elektron bebas, di lapisan-p ada banyak lubang, mereka bergerak secara acak. Sebagian elektron bebas menuju ke lapisan-p, bagian dari lubang ke lapisan-n. Akibatnya, ion positif tanpa kompensasi tetap berada di lapisan-n, dan ion negatif tidak dikompensasi di lapisan-p. Medan listrik lokal muncul di sepanjang batas wilayah, yang mulai menghambat transisi lebih lanjut. Kekuatan medan maksimum pada batas, dan secara bertahap berkurang seiring jarak. Pada akhirnya, kekuatan medan menjadi sedemikian rupa sehingga transfer lubang dan elektron berhenti dan kondisi keseimbangan terbentuk. Untuk silikon, tegangan medan internal sekitar 0,5 volt. Tergantung pada konsentrasi pengotor di kedua sisi. Ketergantungan lemah, sekitar 0,1 volt ketika konsentrasi berubah 10 kali.

Selain penampilan medan listrik pada batas, ada penurunan konsentrasi elektron dan lubang bebas. Langsung pada batas layer ke nol. Oleh karena itu nama kedua - "wilayah habis". Lebar wilayah ini tergantung pada tegangan pada transisi dan konsentrasi pengotor. Ketergantungan pada konsentrasi pengotor adalah kuadrat terbalik, yaitu dengan peningkatan konsentrasi dengan faktor 100, lebar SCR berkurang dengan faktor 10 (sebenarnya, sedikit kurang, karena tegangan di persimpangan meningkat).

Ini adalah keadaan di mana tegangan eksternal tidak diterapkan ke struktur.

Jika Anda menerapkan tegangan eksternal, maka itu adalah vektor dengan internal.

Kami menerapkan tegangan maju kecil ke persimpangan, yaitu plus (+) ke p-layer, minus (-) ke n-layer. Bidang eksternal dan internal diarahkan ke berbagai arah dan mulai saling memberi kompensasi. Tegangan transisi dan lebar SCR berkurang. Ketika tegangan medan eksternal menjadi lebih tinggi dari internal, SCR menghilang, persimpangan pn terbuka sepenuhnya. Untuk dioda semikonduktor bahkan ada parameter - ambang tegangan. Ini adalah tegangan maju di mana dioda terbuka sepenuhnya.

Sekarang gunakan tegangan balik: minus (-) ke p-layer, plus (+) ke n-layer. Bidang eksternal dan internal bertambah, tegangan di persimpangan dan lebar SCR meningkat.

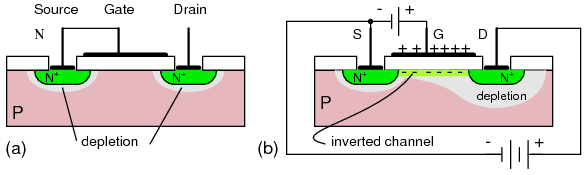

Jika kami mentransfer model ini ke transistor efek medan kami, kami mendapatkan gambar di bawah ini:

Merah muda terang menandakan area kosong (SCR). Kami mendapatkan bahwa lebar nyata dari

basis aktif , yang dikendalikan oleh tegangan gerbang, kurang dari jarak sumber-drain. Yaitu, ukuran basis dikurangi lebar transisi SCR. Dengan tidak adanya tegangan suplai, lebar SCR dari sumber dan tiriskan adalah sama. Jika Anda menerapkan voltase pengoperasian, lebar SCR dari drain meningkat, karena itu berada di bawah bias balik. Basis aktif semakin menyempit:

Jika basis terlalu pendek, SCR saluran dan sumber terhubung. Lebar basis aktif menjadi 0, arus mengalir dari drain ke sumber, transistor terbuka. Terlepas dari tegangan pada rana. Transistor menjadi tidak terkendali. Efeknya disebut "pangkalan dasar" (

catatan: sebagaimana F376 benar dicatat , kemungkinan besar, kita berbicara tentang "kerusakan dasar").

Masih ada opsi perantara ketika SCR tidak menutup, tetapi jarak dari sumber ke batas SCR limpasan kurang dari 8 nm. Kemudian, dalam SCR, elektron mulai menggali dari sumbernya. Setelah di SCR, mereka dibuang ke saluran pembuangan oleh medan listrik. Sederhananya, arus tunneling yang layak akan mengalir dari sumber ke saluran pembuangan.

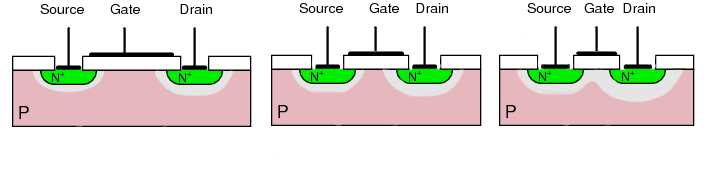

Kerusakan longsoran salju

Jika medan listrik di dalam SCR menjadi terlalu tinggi, maka sebuah elektron yang secara tidak sengaja terbang ke dalamnya berakselerasi sangat cepat sehingga ia menghilangkan elektron dari atom netral. 2 elektron muncul, mereka kembali mempercepat dan melepaskan elektron dari yang berikut, dll. Prosesnya menyerupai longsoran salju, karenanya namanya. Saluran konduktif muncul di SCR di mana arus mengalir. Transistor terbuka secara spontan.

Situasi serupa dapat terjadi di dielektrik gerbang. Jika kekuatan medan berada di atas ambang batas, elektron "cepat" yang terbang keluar dari logam mempercepat dan menyebabkan longsoran salju.

Perbandingan yang jelas dari berbagai jenis kerusakan. Sumber

Perbandingan yang jelas dari berbagai jenis kerusakan. SumberUntuk menghindari kerusakan longsor seperti itu, perlu untuk mencegah kelebihan kekuatan medan di atas nilai kerusakan. Kekuatan Bidang = Stres / Panjang. Yaitu perlu untuk mengurangi tegangan dan meningkatkan lebar SCR (atau ketebalan dielektrik).

Area hambatan listrik

Ini sudah merupakan teknik listrik klasik. Dan saluran, dan sumber, dan saluran, dan bahkan trek logam konduktif memiliki hambatan listrik sendiri. Resistansi lebih tinggi, semakin besar panjang plot dan semakin kecil luas penampang.

Misalkan kita semua elemen transistor dikurangi secara proporsional sebanyak 2 kali. Dengan mengurangi panjangnya, resistansi penampang

berkurang 2 kali , dan dengan mengurangi lebar dan tinggi

bertambah 4 kali . Secara total, ini memberikan

peningkatan resistensi elemen sebanyak 2 kali . Dengan berlalunya arus, resistansi menyebabkan penurunan tegangan. Untuk tegangan transistor di wilayah 1 V dan di bawahnya, bahkan penurunan tegangan kecil akan sangat penting.

Untuk metalisasi, pertanyaan ini diselesaikan dengan sederhana - lapisan sempit pertama logam hanya menghubungkan unsur-unsur di dalam sel. Segala sesuatu yang lain dibawa ke tingkat metalisasi yang lebih tinggi: di sana lapisan oksida dibuat lebih tebal dan jalurnya lebih lebar. Namun demikian, ukuran jendela kontak dan trek metalisasi tidak dapat dikurangi tanpa batas.

Untuk bidang silikon, peningkatan resistensi dikompensasi oleh peningkatan konsentrasi pengotor. Setidaknya hingga saat ini, hingga efek tunneling dan breakdown mulai memengaruhi.

Cara lain adalah teknologi "silicon stretched", atau "silicon strained". Esensinya adalah bahwa lapisan germanium diendapkan pada substrat silikon. Germanium adalah unsur dari kelompok yang sama dengan silikon, serupa dalam struktur kristal. Namun, atom germanium lebih besar, masing-masing, jarak antara mereka dalam kisi kristal lebih besar. Kemudian, film silikon epitaxial tipis terbentuk di atas germanium. Silikon dalam film mulai mengulangi struktur kristal germanium, langkah kisi kristal akan berada di germanium dan lebih besar dari pada silikon biasa. Ternyata silikon itu, seolah-olah, membentang ke segala arah. Karena itulah namanya. Ini memberikan peningkatan dalam mobilitas elektron dan lubang.

Efek gabungan dari efek fisik

Sekarang pertimbangkan efek dari efek-efek ini bersama-sama.

Ancaman utama dalam miniaturisasi transistor adalah basis tusukan. Untuk menghapusnya, Anda harus mengurangi lebar SCR. Ini dapat dikurangi dengan mengurangi stres eksternal dan meningkatkan konsentrasi pengotor dalam basa.

Tegangan suplai tidak memiliki tempat untuk mengurangi, sudah ada di wilayah 1V - sekitar dua ambang batas. Jika kita melakukan lebih sedikit lagi, maka kita berisiko mendapatkan pembukaan transistor yang “tidak jelas” karena hambatan listrik.

Anda dapat meningkatkan konsentrasi pengotor dalam database, tetapi kemudian kami mendapatkan:

- peningkatan tajam dalam arus bocor tunneling dari drain ke pangkalan;

- peningkatan risiko terkena longsoran salju transisi;

- meningkatkan ambang tegangan untuk menginduksi saluran, dengan risiko mendapatkan gangguan dielektrik gerbang.

Karena keterbatasan ini,

konsentrasi pengotor dalam alas ditetapkan pada 10 18 -10 19 .

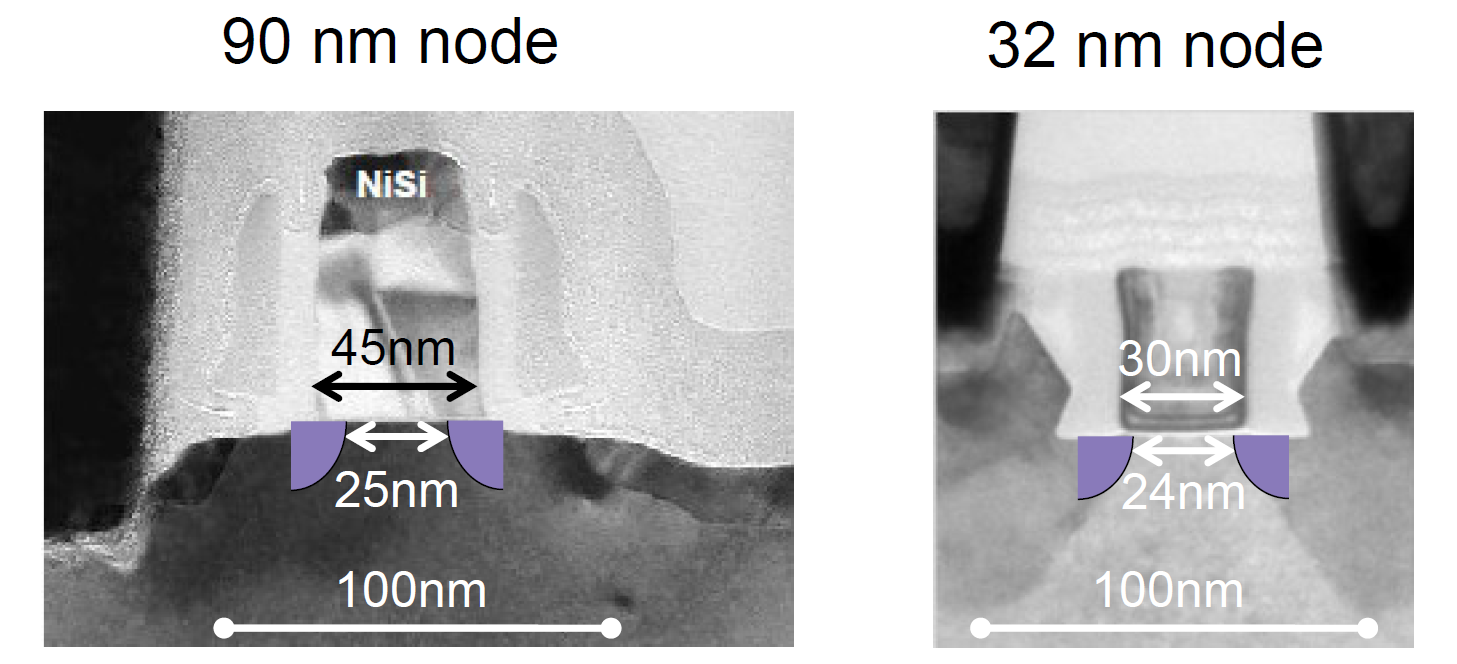

Semua ini dan faktor yang tidak disebutkan namanya membatasi

lebar dasar minimum untuk transistor MOS silikon di wilayah 25 nm . Itu mungkin lebih sedikit, tetapi arus bocor menjadi tidak memadai dan probabilitas kegagalan meningkat secara eksponensial.

Mikrograf transistor dibuat pada teknologi proses 90 nm dan 32 nm. Zoom dan skalanya identik. Sumber

Mikrograf transistor dibuat pada teknologi proses 90 nm dan 32 nm. Zoom dan skalanya identik. SumberSeperti yang dapat kita lihat, ukuran kontak logam telah menjadi jauh lebih kecil, tetapi lebar alasnya tidak berubah. Semua sama 25 nm. Terlebih lagi, untuk transistor yang menggunakan teknologi 14 nm, 10 nm dan 7 nm, itu sama (

ooops! ).

Ini pertama kali ditemukan ketika bergerak dari 130 nm ke seri 90 nm pertama. Kemudian untuk pertama kalinya mereka tidak dapat mengurangi lebar alas secara proporsional dengan semua ukuran lain, tetap sekitar 35 nm. Kemudian, itu masih dikurangi menjadi 25 nm, tetapi sejak itu lebar basis tidak lagi tunduk pada proporsi teknologi. Dan semakin kecil transistor menjadi, semakin banyak ini memanifestasikan dirinya.

Itu perlu untuk mengubah kriteria proses teknis. Apa yang telah kamu lakukan Kebanyakan tidak melakukan apa pun. Mereka terus mengeluarkan izin fotolitografi sebagai norma dari proses teknologi. Atau lebar minimum jalur metalisasi sebagai manifestasi dari operasi yang paling sederhana dan intuitif. Dan kemudian kita beralih ke pemasaran ...

Pemasar paling kreatif datang dari Intel. Mereka mulai menghitung laju proses teknis dari ukuran elemen, misalnya, berdasarkan luas sel enam-transistor dari memori statis. Dalam teknologi dengan resolusi litografi 65 nm, adalah 0,77 μm

2 , dan pada resolusi 40 nm menjadi 0,37 μm

2 . Jika ukuran transistor berkurang secara proporsional seperti sebelumnya, maka ini sesuai dengan teknologi 45 nm. Jadi kami akan menganggap bahwa kami memiliki teknologi 45 nm. Di sinilah perbedaan antara teknologi Intel dan lainnya berasal dari - 28 nm untuk semua, 32 nm untuk Intel; 20 nm untuk semua, 22 nm untuk Intel; 10 nm untuk semua, 14 nm untuk Intel.

Seperti yang ditunjukkan oleh sejarah selanjutnya, Intel akhirnya menjadi lebih jujur daripada para pesaingnya.

Efek arus bocor

Sudah ada jadwal yang luar biasa dari sebuah artikel di tahun 2010:

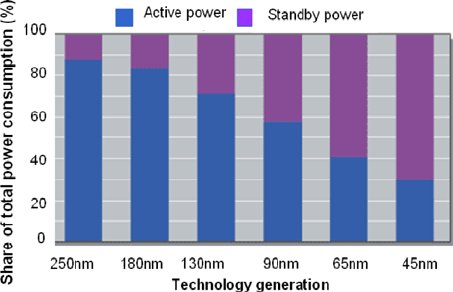

Sumber

SumberGrafik menunjukkan persentase konsumsi energi yang bekerja dan palsu. Biru - pelepasan energi sebagai hasil dari arus isi ulang (arus operasi), ungu - hasil dari arus bocor (arus nyasar). Ini memperhitungkan langkah-langkah yang telah diambil untuk mengurangi arus yang menyimpang.

Alasan mengapa pertumbuhan kecepatan clock prosesor berhenti terlihat jelas. Prosesor pertama dalam 3 GHz (

Pentium 4 , misalnya) muncul pada awal 2000-an. Jadi pada level ini dan bertahan. Biasanya ini dijelaskan oleh fakta bahwa jumlah inti telah meningkat, logika menjadi lebih rumit, perpipaan semakin dalam, sehingga persyaratan stabilitas dan, secara umum, kebahagiaan dalam gigahertz telah tumbuh. Sebagian benar.

Tapi!Sebelumnya, mereka entah bagaimana berhasil menggabungkan semua faktor ini dengan peningkatan frekuensi.Faktanya adalah bahwa sebelumnya, dengan penurunan ukuran transistor, cadangan untuk konsumsi energi muncul. Misalnya, norma teknologi menurun 2 kali, jumlah transistor meningkat 4 kali, dan konsumsi daya rata-rata setiap transistor berkurang 6-7 kali. Faktanya adalah bahwa transistor CMOS mengkonsumsi arus saat beralih, dan peningkatan jumlah transistor terutama disebabkan oleh peningkatan memori cache. Transistor memori jarang berpindah. Oleh karena itu, mereka mengonsumsi lebih sedikit dari elemen aktif prosesor.Perbedaan ini memungkinkan untuk menaikkan frekuensi jam dengan panas yang sama.Saat berjalan dari 180 nm ke 130 nm, arus bocor memakan delta ini. Sejak itu, terlepas dari semua trik, mereka belum keluar dalam plus. Semuamelahap bonggol sialan memakan arus bocor. Di suatu tempat bahkan menjadi minus, misalnya, untuk prosesor hemat energi harus mengurangi frekuensi. Jika keajaiban dihapus, maka untuk teknologi 45 nm kita mendapat margin tiga kali lipat untuk meningkatkan frekuensi.Bahkan, selama tahun 2000-an, sebuah glander yang sunyi terjadi perubahan prioritas. Sebelumnya, prioritasnya adalah mengurangi ukuran transistor, sekarang untuk mengurangi kebocoran.Tentang Teknik Kontrol Kebocoran

Perubahan Bahan Subgate Oksida

Dengan beralih ke High-k, dielektrik juga harus mengubah bahan gerbang. Alih-alih polisilikon, mereka mulai menggunakan kembali logam, biasanya nikel silisida NiSi. Silikon oksida masih digunakan untuk pemisahan dengan lapisan metalisasi kedua dan selanjutnya.Secara singkat tentang dielektrik High-k. . , . , , . – – .

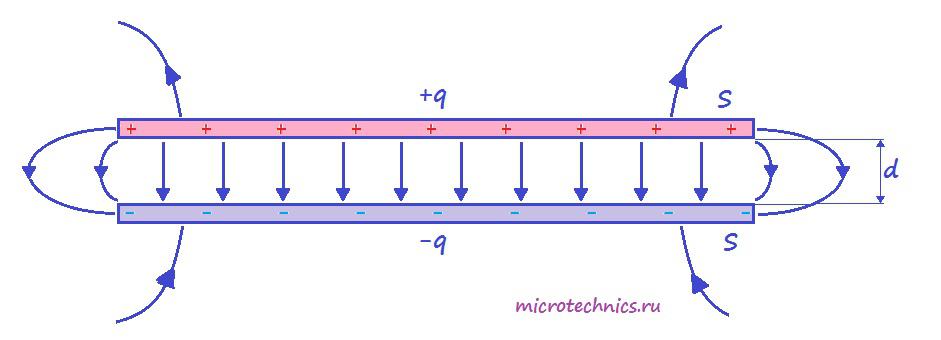

— . . , . . . :

S – ,

d – ,

ԑ – , 1, 1,

ԑ

0 – .

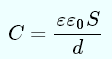

, . , . 1,2 (

sic! ). 6

(!!!) . . 5 , .. 1 , 10 (

!!! ) ( 10 0,2 ). .

– . — High-k . HfO

2 Ta

2 O

5 . 3.9, High-k 25-30. , , - .

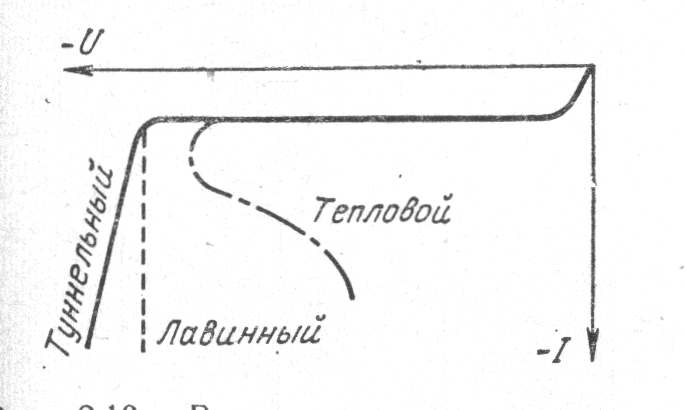

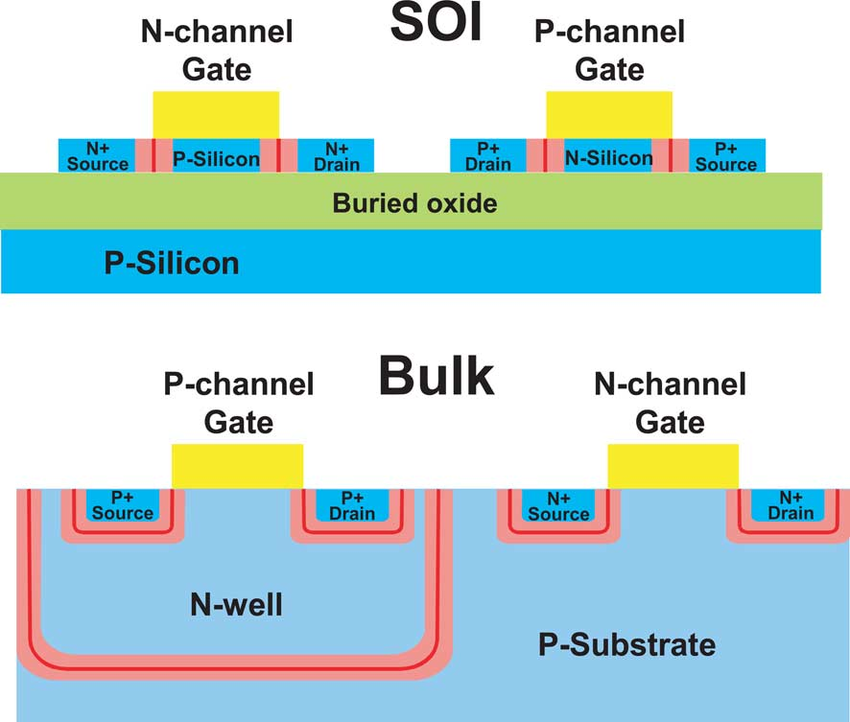

Silikon pada isolator (SOI)

Teknologi silikon pada isolator , alias SOI, alias SOI, telah digunakan sebelumnya untuk mengisolasi sel. Di sini kita melangkah lebih jauh: lapisan oksida terbentuk di atas substrat silikon, dan lapisan silikon secara epitaxial tumbuh ( UPD: penulis, tampaknya, sedikit menyederhanakan proses SIMOX dan Smart Cut ). Secara skematis, perbedaan antara teknologi SOI dan MOS planar konvensional.Teknologi ini secara dramatis mengurangi arus bocor.Namun ada juga kekurangannya. Teknologi SOI masih sangat rumit dan mahal. Selain itu, karena basa terisolasi tipis, ada masalah dengan akumulasi jumlah elektron atau lubang yang cukup untuk membentuk saluran. Salurannya sangat sempit. Masalah lainnya adalah pembuangan panas. Silikon oksida memiliki konduktivitas termal yang rendah, dan penghilangan panas dari film ke massa substrat sulit dilakukan.Atau, alih-alih silikon oksida, safir Al 2 O 3 dapat digunakan , konduktivitas termal lebih tinggi. Idealnya, oksida harus berada di bawah selokan dan sumbernya, tetapi oksida itu tidak berada di bawah basa. Kemudian, dalam kombinasi dengan dielektrik High-k, akan dimungkinkan untuk meningkatkan konsentrasi pengotor di dasar dan mengurangi lebar saluran hingga 15 nm. Namun, sementara penggunaan teknologi ini terbatas.

Secara skematis, perbedaan antara teknologi SOI dan MOS planar konvensional.Teknologi ini secara dramatis mengurangi arus bocor.Namun ada juga kekurangannya. Teknologi SOI masih sangat rumit dan mahal. Selain itu, karena basa terisolasi tipis, ada masalah dengan akumulasi jumlah elektron atau lubang yang cukup untuk membentuk saluran. Salurannya sangat sempit. Masalah lainnya adalah pembuangan panas. Silikon oksida memiliki konduktivitas termal yang rendah, dan penghilangan panas dari film ke massa substrat sulit dilakukan.Atau, alih-alih silikon oksida, safir Al 2 O 3 dapat digunakan , konduktivitas termal lebih tinggi. Idealnya, oksida harus berada di bawah selokan dan sumbernya, tetapi oksida itu tidak berada di bawah basa. Kemudian, dalam kombinasi dengan dielektrik High-k, akan dimungkinkan untuk meningkatkan konsentrasi pengotor di dasar dan mengurangi lebar saluran hingga 15 nm. Namun, sementara penggunaan teknologi ini terbatas.Transisi FinFET

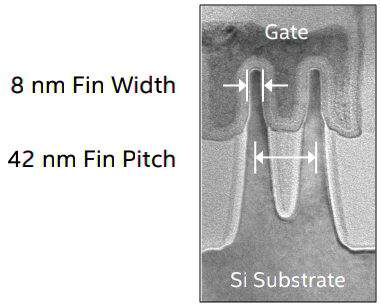

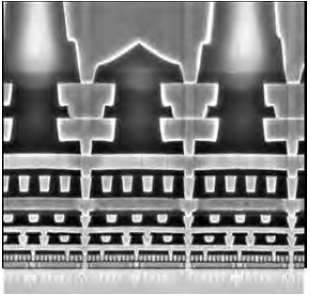

Nama dari sirip bahasa Inggris - sirip, lambang. Teknologi ini pertama kali digunakan pada teknologi 22 nm dan saat ini dominan dalam produksi prosesor. Intinya adalah bahwa tidak ada lapisan silikon lengkap di atas oksida yang tumbuh secara epitaxially, tetapi punggungan individu di zona dibersihkan dari oksida. UPD: tautan bagus tentang FinFET dari a5b , di mana awalnya wafer silikon terukir untuk menghasilkan sirip. Contohnya seperti itu. Sumber

Contohnya seperti itu. Sumber Perbandingan skematis dengan teknologi planar - transistor menjadi tiga dimensi. SumberRana dalam teknologi ini mengalir di sekitar saluran dari tiga sisi. Ketika kita memberikan voltase ke gerbang, itu menarik elektron (lubang) dari kedalaman ke puncak punggungan, dan sebuah saluran terbentuk di dalamnya. Dengan demikian, seluruh zona aktif saluran, sumber, dan gerbang masuk ke punggungan, dan kebocoran arus yang lebih dalam ke substrat minimal. Dalam hal ini, punggungan tidak terisolasi secara termal dari substrat dan panas bebas turun.Biasanya menggunakan transistor dua atau tiga bergaris (tiga gerbang). Dengan dimensi seperti itu, membuat punggungan persegi panjang seperti pada diagram tidak realistis, dalam bentuknya agak kerucut terpotong.

Perbandingan skematis dengan teknologi planar - transistor menjadi tiga dimensi. SumberRana dalam teknologi ini mengalir di sekitar saluran dari tiga sisi. Ketika kita memberikan voltase ke gerbang, itu menarik elektron (lubang) dari kedalaman ke puncak punggungan, dan sebuah saluran terbentuk di dalamnya. Dengan demikian, seluruh zona aktif saluran, sumber, dan gerbang masuk ke punggungan, dan kebocoran arus yang lebih dalam ke substrat minimal. Dalam hal ini, punggungan tidak terisolasi secara termal dari substrat dan panas bebas turun.Biasanya menggunakan transistor dua atau tiga bergaris (tiga gerbang). Dengan dimensi seperti itu, membuat punggungan persegi panjang seperti pada diagram tidak realistis, dalam bentuknya agak kerucut terpotong. Sumber Transistor

Sumber Transistor telur yang sama , tampilan atas. Apa yang menonjol di atas oksida adalah ujung gunung es nanometer. Basis punggungan jauh lebih luas dan tidak terlihat di sini.

sama , tampilan atas. Apa yang menonjol di atas oksida adalah ujung gunung es nanometer. Basis punggungan jauh lebih luas dan tidak terlihat di sini.Sedikit tentang metalisasi

Jejak logam pada lapisan metalisasi pertama dan terendah selalu dicoba untuk diminimalkan. Faktanya adalah bahwa jalur metalisasi bentuk dengan silikon kapasitor logam-dielektrik-silikon datar yang sama. Tapi tidak seperti shutter, ini adalah kapasitor yang tersesat. Dengan kapasitansi besar pada frekuensi dalam gigahertz, komunikasi listrik palsu dapat terjadi di tempat yang seharusnya tidak. Untuk mengurangi kapasitansi liar, Anda perlu mengurangi area trek. Oleh karena itu, trek di lapisan metalisasi pertama dibuat sesingkat dan setipis mungkin. Untuk alasan yang sama, mereka mencoba untuk tumpang tindih lapisan metalisasi yang berbeda pada sudut kanan - pertama membuat trek longitudinal, lapisan melintang berikutnya trek. Semakin tinggi lapisan, semakin tebal oksida di bawahnya dan semakin lebar jalurnya.Kenapa saya ?! Karena ketebalan track logam pertama sangat minim, maka sering diindikasikan sebagai norma proses teknologi. Dalam teknologi FinFET, ruang antara punggungan diisi dengan oksida. Lapisan yang cukup tebal di atas dielektrik High-k, gerbang, bubungan dan palung. Lapisan metalisasi pertama dihilangkan ke penyumbatan di atas palung. Track sendiri dibuat lebih lebar untuk mengurangi hambatan listrik dan mengkompensasi gundukan. Yaitu

lebar lintasan sekecil mungkin dan kenyataan juga menyimpang. Pai Logam Laminasi

Pai Logam LaminasiYaitu

standar proses menjadi semakin banyak kuantitas virtual. Oleh karena itu, kami memiliki prosesor serupa dengan parameter yang ditandai oleh standar dari 7 nm hingga 22 nm. Proses FinFET 22 nm memungkinkan Anda bertahan dengan dua punggungan, 7 punggungan membutuhkan 3 punggungan, sebagai akibatnya, dimensi transistor kira-kira sama. Namun, majalah sering terus menulis bahwa dengan transisi dari 10 nm ke 7 nm, jumlah transistor akan meningkat 1,8 kali lipat. Orang-orang masih memiliki pola lama dari era Moore ...Apa selanjutnya? Transisi ke transistor volumetrik telah menyebabkan munculnya sejumlah besar modifikasi yang menjanjikan. Sebagai contoh, Samsung mengumumkan teknologi GAAFET untuk teknologi 5nm. Perbandingan CMOS, FinFET dan GAAFET jelas. Sumber

Perbandingan CMOS, FinFET dan GAAFET jelas. SumberYaitu

sisir tidak boleh kontinu, tetapi dibagi menjadi utas terpisah. Pertanyaan: Apakah game sepadan dengan lilin? - tetap terbuka. UPD: seperti yang dicatat dengan benar oleh F376 , FinFet menyediakan input medan listrik dari dua pihak. Gate-All-Around FET menyediakan entri dari semua arah, yang lebih efisien.Ada juga opsi untuk penutup jendela, vertikal, dll. Ada kombinasi FinFET dan SOI. Secara umum, proses kimia epitaksi lebih kompleks, tetapi lebih linier dan dapat diprediksi dibandingkan litografi. Ini menyediakan digunakan untuk akurasi yang lebih besar dan kemampuan untuk menciptakan struktur tiga dimensi yang lebih halus.Situasi di pasar modern dari produsen dan prospek mikroprosesor

Jadi, tiga pemimpin menonjol - Intel, Samsung dan TSMC. Intel memproduksi di bawah merek sendiri, sisanya terutama dipesan. Di bawah merek AMD, NVIDIA, Qualcomm, Apple, IBM menyembunyikan chip yang diproduksi di pabrik TSMC atau Samsung. Beberapa pemimpin tua jatuh atau berlari ke penghalang. Orang Cina berusaha masuk ke liga besar, tetapi sejauh ini tidak terlalu berhasil: mereka tidak memiliki basis teknologi sendiri, dan para pemimpin dunia dalam produksi peralatan menjaga jalur teknologi terbaru untuk orang Cina.

Optimisme para ahli dikaitkan dengan transisi ke struktur curah dan awal penggunaan litografi EUV. Samsung dan TSMC telah mulai menggunakannya secara terbatas, untuk struktur yang paling rumit. Ini memberi mereka kesempatan untuk melaporkan pencapaian standar 7 nm dan di masa depan hingga 5 nm. Meskipun, seperti yang sudah dijelaskan, angka-angka ini sebenarnya tidak banyak berpengaruh. Intel yang sama umumnya meninggalkan EUV. Tampaknya, mereka tidak percaya bahwa ini akan sangat meningkatkan kinerja.

Di sisi lain, orang-orang dalam subjek memahami bahwa era Moore telah berakhir, dan setiap langkah baru dalam pertumbuhan produktivitas akan membutuhkan lebih banyak upaya dan waktu. Pertumbuhan cepat mikroelektronika berakhir (

hiks! ). Bagaimana ini terjadi sekali di industri otomotif dan penerbangan. Setelah pertumbuhan eksplosif, perkembangan lambat terjadi.

Di antara poin terobosan yang menjanjikan, seseorang dapat memilih transisi ke material lain (bukan silikon) dan penciptaan sirkuit mikro multilayer (integrasi 3D - salam untuk ide AMD). Untuk integrasi 3D, Anda harus mengurangi pembangkitan panas secara drastis atau meningkatkan pembuangan panas.

Itu semua untuk ukuran transistor. Ada cadangan pertumbuhan produktivitas lainnya. Dalam optimalisasi arsitektur, misalnya. Anda bahkan dapat melakukan langkah pemasaran, dengan mengatakan bahwa prosesor baru dengan arsitektur yang ditingkatkan berfungsi seolah-olah itu adalah prosesor lama dengan teknologi 0,5 nm. Oleh karena itu, kami menandainya 0,5 nm. Dan buah ara dengan dia bahwa dimensi transistor adalah sama.

Dimungkinkan untuk membuat tipe sel baru dari kombinasi transistor. Misalnya, alih-alih 6 sel memori transistor, buat 2 struktur transistor dengan fisika kompleks yang saling mempengaruhi. Struktur volumetrik di sini memberikan banyak peluang.

Batas fisik

Seseorang mungkin mengatakan bahwa pesimisme penulis tidak dibenarkan. Mereka menemukan cara untuk mengatasi batasan. Mungkin tidak secepat sebelumnya, tapi tetap saja.

Faktanya adalah masih ada proses fisik yang tidak dapat dilewati. Yang utama adalah materi yang terdiri dari atom, dan pembawa muatan adalah elektron. Untuk membuat transistor lebih kecil dari atom tidak berfungsi. Ini tidak akan berhasil untuk membuat bahkan kurang dari 1000 atom. Karena ada elektron dan hubungan ketidakpastian Heisenberg. Sebuah elektron adalah partikel yang sangat tidak stabil, perilaku yang kurang lebih stabil hanya mungkin terjadi pada susunan ribuan dan jutaan elektron. Dengan satu elektron, Anda hanya dapat menghancurkan kucing Schrödinger.

Catatan: meskipun ada perkembangan pada transistor elektron tunggal (

1 ,

2 dan

3 )

Bahkan pada ukuran saat ini, tabrakan terjadi karena operasi spontan transistor. Jika probabilitas tumbukan adalah 10

-9 (satu per miliar), maka dengan jumlah elemen dalam miliaran dan frekuensi dalam GHz, ini memberikan rata-rata 1 tumbukan per siklus, atau beberapa miliar tumbukan per detik. Untuk menangkap ini, ada sistem untuk memantau integritas operasi, dan operasi yang mencurigakan dikirim untuk dieksekusi kembali.

Dengan miniaturisasi, jumlah tabrakan mulai meningkat sangat tajam. Akibatnya, kita sampai pada situasi nol atau bahkan efek negatif dari miniaturisasi. Yaitu Transistor dibuat lebih sedikit, mereka lebih cocok dengan kristal, tetapi karena pertumbuhan tabrakan dan siklus pemrosesan ulang, total produktivitas tidak meningkat. Atau bahkan mungkin jatuh. Dan ambang ini cukup di cakrawala.

Beberapa kata tentang mikroelektronika digital domestik

Berlawanan dengan kepercayaan populer, hingga 1985 jeda Uni Soviet dari para pemimpin tidak begitu besar. Sekitar 3-4 tahun. Ini adalah jika kita mengambil perusahaan

terkemuka di Zelenograd (catatan:

BarsMonster menulis tentang Micron

pada saat itu ). Di bawah hukum Moore, bahkan keterlambatan 3-4 tahun sangat memengaruhi kinerja. Ada masalah dengan memperoleh oksida berkualitas tinggi, dengan kejelasan persimpangan pn. Jika kita menambahkan ini kebijakan konservatif dengan chip pengepakan dalam sebuah kasus (saluran kontak lama tidak meningkatkan produktivitas perangkat), serta standar Soviet untuk produksi papan dan kotak-kotak dengan setumpuk besi (mereka yang mengerti tentang tape recorder Soviet akan mengerti), kita mendapat lelucon tentang chip Soviet dengan cor-iron pegangan untuk membawa.

Ada banyak alasan untuk jaminan simpanan. Kemudian startanuli, sumber daya terbatas, sumber daya penyemprotan. Ketika orang Amerika fokus pada CMOS, kami terus bereksperimen dengan berbagai teknologi. Mereka bekerja cukup aktif dengan alternatif silikon, terutama dengan bahan A

3 B

5 . Nah, relaksasi umum dari lembaga penelitian Soviet akhir.

Setelah 1985, Amerika mulai dengan tiba-tiba, dan kami mulai mengalami masalah. Kemudian tahun 1990-an, ketika kehidupan di industri itu hangat oleh inersia. Akibatnya, mereka memasuki abad ke-21 dengan teknologi 800 nm, ketika para pemimpin telah menyerbu 130 nm. Kehidupan kedua industri ini diberikan oleh chipisasi massal kartu dan pesanan pemerintah. Produksi utama baja: chip untuk kartu SIM, kartu bank, kartu pembayaran, transportasi dan kartu diskon dan barang-barang konsumen lainnya. Gigahertz besar dan nanometer kecil tidak diperlukan di sana.

Catatan: ngomong

- ngomong, saat di Moskow ada satu kali tiket (dibeli-pakai-lempar-keluar, diisi dengan pabrik), di Cina yang sama mereka secara aktif mempromosikan teknologi hemat sumber daya, khususnya, penggunaan "token" yang digunakan kembali di kereta bawah tanah (bahkan untuk satu perjalanan singkat) .

Video tentang kereta bawah tanah Shenzhen

Namun demikian, ada upaya untuk memasuki "liga besar" mikroelektronika. Pembangunan berjalan dalam empat arah utama.

- Proses teknis "Berdaulat". Upaya untuk menciptakan siklus produksi penuh pada peralatan domestik dan proses teknologi kita sendiri. Kami mengikuti jalan yang sama dengan yang dilakukan para pemimpin 20 tahun yang lalu, tetapi dengan mempertimbangkan rake yang ditemukan dan solusinya. Dari yang terakhir, apa yang ada di sumber terbuka adalah 250 nm dalam seri dan 150 nm dalam proses implementasi. Ini juga termasuk upaya untuk membuat instalasi litografi EUV kita sendiri pada 13,5 nm dan dengan demikian segera keluar jika tidak di liga besar, kemudian dekat dengan mereka.

- Pembelian jalur teknologi dari produsen terkemuka. Masalahnya di sini adalah bahwa instalasi paling modern tidak dijual kepada kami bahkan di tahun-tahun terbaik. Biasanya mereka menjual jalur usang yang telah dihentikan. Sekarang, sehubungan dengan sanksi itu, terlebih lagi. Di sini kita dapat mengingat epik dengan pembelian oleh Angstrom dari peralatan pabrik AMD Dresden pada tahun 2007, di bawah proses manufaktur 180 nm. Atau pembelian garis Mikron 90 nm dari STMicroelectronics Prancis diikuti dengan peningkatan ke 65 nm. Meskipun ini adalah proses pembuatan tertipis di Rusia, mereka berhasil merebut sebelum sanksi. Benar, sekarang ada solusi - pengadaan melalui Cina.

- Memesan produksi di pabrik-pabrik di Cina atau Taiwan. Pada saat yang sama, arsitektur dan topologi sepenuhnya dikembangkan bersama kami,

sekarang kami bahkan membuat topeng foto kami sendiri . Orang Cina hanya dapat mereproduksi proses teknologi di pabrik mereka. Kami mendapatkan prosesor produktif yang lebih maju, dan mengembangkan kompetensi dalam pengembangan sistem prosesor yang paling modern. Di sini, bukan sekelompok ilmuwan Kulibin yang terlibat, tetapi tim desain besar. Hanya bagian terakhir, produksi, yang dikeluarkan dari siklus penuh.

Catatan: Baikal dibuat sesuai dengan standar 28 nm di pabrik TSMC. Artikel tentang keluarnya Baikal dan analisisnya.

- Perkembangan teknologi alternatif. Ini adalah pengembangan teknologi yang menjanjikan yang mungkin menyebar luas di masa depan. Ini termasuk pekerjaan pada senyawa A 3 B 5 dan heterostruktur, terutama gallium arsenide dan nitride. Serta upaya untuk mengoptimalkan sinar elektron dan litografi sinar-X untuk produksi massal, yang umumnya menghilangkan batasan litografi.

Catatan: kami mewarisi sekolah yang kuat tentang struktur heterostruktur dari Alferov, tetapi bahkan dengan dukungan negara, OptoGaN tidak memperluasnya , kondisi pasar dan pasar gagal.

Secara umum, situasinya tidak brilian untuk mikroelektronika Rusia. Tapi ada harapan bahwa para pemimpin pasti akan melambat karena keterbatasan fisik, dan di sini kita, perlahan-lahan, merangkak di belakang.

Akord terakhir tentang memori dan jendela peluang di bagian ketiga dalam beberapa hari - tetap disini!

Jangan lupa untuk berlangganan

blog : itu tidak sulit bagi Anda - saya senang!

Dan ya, tolong tulis tentang kekurangan yang tertulis dalam teks di PM.