Saya memutuskan untuk menulis catatan ini tentang Habré dalam bahasa Rusia dan bahasa Inggris untuk mendistribusikan tautannya ke forum dan grup berbahasa Inggris dan Rusia. Teks Rusia bukan terjemahan bahasa Inggris dan sebaliknya - Saya hanya menulis catatan dua kali (saya benci menerjemahkan). Mereka yang ingin mengkritik bahasa Inggris saya segera dikirim ke akhir posting, di mana mereka akan terkejut dengan aksen saya dalam video berdurasi panjang. Saya melihat penekanan saya bukan sebagai bug, tetapi sebagai fitur. Kita semua tahu bahwa banyak orang Amerika menemukan, misalnya, aksen Inggris nasofaring menarik. Sudah waktunya untuk memberikan status yang sama ke aksen Rusia yang parah. Untuk melakukan ini, sebanyak mungkin orang Rusia perlu berpidato di berbagai acara internasional. Kata sandi kami adalah "tahun mi Speak From May Hart".

Tapi pertama-tama tentang pameran.

Jutaan konsumen gadget di seluruh dunia menonton Consumer Electronics Show (CES), yang berlangsung di Las Vegas pada bulan Januari. Mereka, yang tidak pernah tahu apa itu pemicu-D, penting berpendapat bahwa empat gigahertz lebih baik daripada tiga pada prosesor terbaru dari AMD dan Qualcomm. Tetapi ada pameran yang berfokus bukan pada konsumen, tetapi pada pengembang elektronik. Pameran ini disebut Design Automation Conference (DAC), dan dalam beberapa tahun juga berlangsung di Las Vegas, tetapi tidak pada bulan Desember, tetapi pada bulan Juni.

Jutaan pecinta gadget setiap tahun menonton Consumer Electronics Show (CES) yang berlangsung di Las Vegas pada bulan Januari. Orang-orang itu, yang tidak pernah mempelajari fungsi D-flip-flop dan bagaimana penghitungan waktu statis, membahas frekuensi gigahertz setelah membaca artikel terbaru di majalah Wired yang mereka anggap sebagai publikasi teknis. Namun ada konferensi lain, bukan untuk konsumen, tetapi untuk pencipta elektronik. Konferensi ini disebut Design Automation Conference (DAC) dan juga berlangsung di Las Vegas, meskipun tidak setiap tahun, dan bukan pada bulan Januari, tetapi pada bulan Juni.

Industri Electronic Design Automation (EDA) membuat perangkat lunak untuk perancang perangkat keras. EDA dikendalikan oleh tiga perusahaan besar: Synopsys, Cadence dan Mentor Graphics (sekarang menjadi bagian dari Siemens). Baik Synopsys dan Cadence memiliki serangkaian produk lengkap, yang diperlukan untuk merancang dan mensimulasikan chip digital pada berbagai tingkatan. Alur desain, disebut RTL2GDSII, dimulai dari spesifikasi dan pengkodean perilaku siklus sirkuit dalam bahasa deskripsi perangkat keras (Verilog atau VHDL), dilanjutkan dengan mensintesis deskripsi ini ke dalam grafik elemen logika (netlist), kemudian terus menempatkan netlist ke dalam fisik. cetak biru chip dan routing kabel on-chip untuk menghubungkan sel standar, blok bangunan ASIC (Application-Specific Integrated Circuits).

Tiga perusahaan besar mendominasi industri otomatisasi desain elektronik: Synopsys, Cadence dan Mentor Graphics (yang dibeli oleh Siemens beberapa tahun yang lalu). Synopsys dan Cadence telah menciptakan perangkat lunak yang mencakup seluruh rute desain RTL2GDSII. Saya menjelaskan secara singkat rute ini dalam

artikel DAC saya

sebelumnya empat tahun lalu:

Selama 25 hingga 30 tahun terakhir, desain sirkuit mikro paling sering ditulis dalam bahasa deskripsi peralatan Verilog (di Eropa dan di antara militer - VHDL), setelah itu program khusus (sintesis logika) mengubah desain menjadi grafik kabel dan primitif logis, program lain (analisis waktu statis) memberi tahu perancang apakah cocok dengan anggaran kecepatan, dan program ketiga (tempat-dan-rute) menjabarkan desain ini di lokasi chip.

Ketika desain melewati semua tahapan: pengkodean pada veril, debugging, verifikasi, sintesis, analisis waktu statis, perencanaan lantai, tempat-n-rute, ekstraksi parasit, dll. - Ternyata file yang disebut GDSII, yang dikirim ke pabrik, dan chip pabrik bakes. Pabrik paling terkenal dari jenis ini dimiliki oleh Taiwan Semiconductor Manufacturing Company atau TSMC.

John Sanguinetti, seorang guru Verilog sejak 1980-an. John adalah pendiri sebuah perusahaan bernama Simulasi Kronologis yang, pada 1990-an, menciptakan VCS, sebuah Simulator Kode Kompilasi Verilog. Simulator ini sekarang menjadi milik Sinopsis. VCS digunakan oleh sebagian besar perusahaan elektronik besar. VCS membawa ke Synopsys miliar dolar dalam pendapatan.

Di sepanjang sisi ruang pamer adalah John Sanguinetti, seorang guru verilog awal dari tahun 1980-an dan pendiri Simulasi Kronologis. Perusahaan ini memberi dunia simulator Verilog Compiled code Simulator (VCS) yang cepat, yang sekarang menjadi milik Synopsys. Simulator ini digunakan oleh sebagian besar pengembang chip utama. VCS membawa Synopsys miliaran dolar:

Mentor Graphics sekarang menjadi bagian dari Siemens, perusahaan EDA terbesar ketiga. Tidak seperti Synopsys dan Cadence, Mentor Graphics tidak memiliki garis penuh alat RTL2GDSII. Dua aliran pendapatan yang paling dikenal berasal dari Calibre, seperangkat alat verifikasi desain fisik, dan Veloce, emulator perangkat keras. Calibre misalnya termasuk alat yang memeriksa aturan desain geometris (lebar, spasi, penutup) pada "cetak biru" akhir chip. Veloce menggunakan chip mirip-FPGA yang

mensimulasikan meniru desain Verilog dengan sangat cepat.

Mentor Graphics, perusahaan terbesar ketiga di industri EDA, pada akhir 2016 menjadi bagian dari Siemens. Tidak seperti Synopsis dan Keydens, Mentor tidak memiliki seluruh rangkaian program yang mencakup rute RTL2GDSII. Dua sumber utama pendapatan untuk Mentor adalah paket perangkat lunak Calibre, yang melakukan pemeriksaan pada tahap akhir desain microchip, dan emulator Veloce (diucapkan Velochi). Contoh verifikasi dalam Calibre adalah jarak minimum antara trek pada chip

sehingga tidak ada efek antena .

UPD: dikoreksi berdasarkan komentar amartologi : Antena umumnya tentang yang lain. Ini terjadi ketika satu trek menjadi begitu besar sehingga mulai bekerja seperti antena, menerima sinyal pada frekuensi osilasi plasma untuk etsa selama produksi.Dan emulator Veloce menggunakan ASIC berbentuk FPGA untuk dengan cepat

mensimulasikan emulasi sirkuit yang dijelaskan pada level logis, yaitu pada veril.

Selain proyek Calibre dan Veloce yang sangat menguntungkan, Mentor selalu memiliki sejumlah besar proyek, produk, layanan, pelatihan dan program pendidikan lainnya. Misalnya Mentor sedang mengolah bidang verifikasi fungsional, bagian yang sangat penting dari alur kerja desain digital.

Selain proyek-proyek yang sangat menguntungkan seperti Calibre dan Veloce, Mentor memiliki banyak proyek, produk, layanan, proyek penelitian dan program pendidikan lainnya. Misalnya, di Mentor, mereka terlibat dalam verifikasi fungsional, bagian penting dari proses produksi:

Sejumlah perusahaan kecil, termasuk Doulos, Willamette HDL dan Sunburst Design, menjual pelatihan verifikasi perangkat keras kepada perusahaan elektronik besar dan menengah. Ceruk seperti itu ada karena universitas tidak mengajarkan seni verifikasi fungsional dengan benar dan tidak mengadopsi teknologi baru, seperti SystemVerilog, UVM, verifikasi formal menggunakan pernyataan bersamaan, Portable Stimulus, dll dalam kurikulum mereka selama beberapa dekade. Bahkan Stanford tidak memilikinya dalam kurikulum mereka sejauh yang saya tahu dari berbicara dengan lulusan mereka.

Verifikasi fungsional memberi makan beberapa perusahaan kecil yang menjual pelatihan SystemVerilog dan UVM ke perusahaan besar dengan harga yang sangat tinggi, seperti beberapa ribu dolar per orang. Ini termasuk Doulos, Willamette HDL, Sunburst Design dan lainnya:

Perusahaan kecil lain bernama Verific. Mereka hanya memiliki segelintir orang tetapi mereka sangat sukses di ceruk pasar mereka. Verific menjual SystemVerilog parser yang diadopsi oleh perusahaan EDA penting, baik besar maupun kecil.

Berikut ini adalah perusahaan kecil, hanya beberapa orang, tetapi sangat sukses dari jenisnya yang disebut Verific. Dia menjual parser Verilog, yang digunakan banyak perusahaan EDA:

Pendiri Verific memberikan wawancara ke situs web EDA populer yang disebut EDA Cafe. Ada beberapa situs web EDA populer lainnya termasuk deepchip.com John Cooley tetapi saya tidak bertemu John Cooley di lantai DAC kali ini.

Inilah pendiri Verific yang memberikan wawancara kepada EDA Cafe, situs web populer di industri:

Sekarang mari kita bicara tentang FPGA.

Sekarang mari kita bicara tentang FPGA, mereka adalah PPVM (mereka akan memperbaiki saya sekarang), mereka adalah FPGA.

Apa itu, saya juga jelaskan secara singkat dalam

artikel DAC saya

sebelumnya empat tahun lalu:

Dalam versi yang paling sederhana, sebuah FPGA terdiri dari sebuah matriks sel-sel homogen, yang masing-masingnya dapat diubah menjadi fungsi menggunakan multiplexer yang terhubung ke bit-bit memori konfigurasi. Satu sel dapat menjadi gerbang AND dengan empat input dan satu output, yang lain - register bit-tunggal, dll. Kami memuat urutan bit dari memori ke dalam memori konfigurasi - dan sirkuit elektronik yang diberikan terbentuk dalam FPGA, yang dapat berupa prosesor, pengontrol tampilan, dll.

FPGA / FPGA bukan prosesor, “pemrograman” FPGA (mengisi memori konfigurasi FPGA) Anda membuat sirkuit elektronik (perangkat keras), sedangkan saat memprogram prosesor (perangkat keras tetap), Anda memasukkan rantai instruksi program berurutan yang ditulis untuknya. (perangkat lunak).

Dua produsen FPGA terbesar adalah Xilinx dan Altera, sekarang menjadi bagian dari Intel.

Dua perusahaan terbesar yang memproduksi FPGA adalah Xilinx dan Altera, sekarang bagian dari Intel:

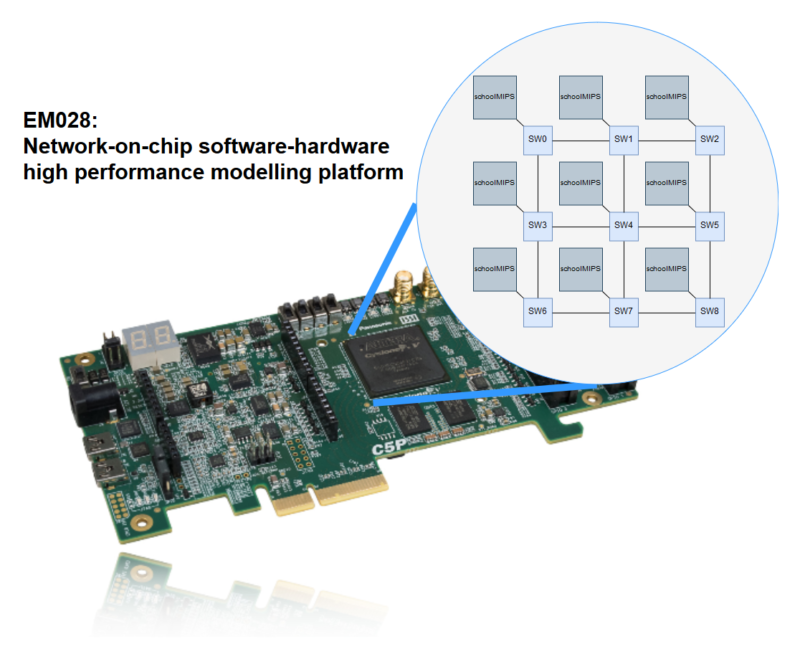

Minggu ini Intel mengumpulkan suara untuk putaran pertama kontes Innovate FPGA. Salah satu entri Rusia menggunakan mesh inti prosesor schoolMIPS kecil.

schoolMIPS mengimplementasikan subset arsitektur MIPS. Itu ada dalam beberapa varian, termasuk siklus tunggal tanpa memori data (yang paling sederhana), versi dengan interupsi, versi pipeline, dll:

Ngomong-ngomong, minggu ini Intel memilih di kontes Innovate FPGA, di mana

tim Rusia juga berpartisipasi. Satu proyek adalah

prototipe sistem multiprosesor berbasis NoC . Ini adalah jaringan prototipe pada sebuah chip dengan sejumlah besar node berdasarkan prosesor oleh Stanislav Zhelnio

sparf (berdasarkan buku Harris & Harris "Sintesis Digital dan Arsitektur Komputer")

https://github.com/MIPSfpga/schoolMIPS . Menjadikan siswa 4 tahun di MIEM NRU HSE:

Dunia FPGA tidak terbatas pada Xilinx dan Altera / Intel. Ada beberapa vendor yang jauh lebih kecil, seperti Lattice dan Microsemi / Actel, dan bahkan perusahaan kecil yang tidak mendesain chip akhir sendiri sedikit melisensikan desain blok sel FPGA ke perusahaan ASIC. Aplikasi yang bermanfaat adalah membuat coprocessor yang dapat dikonfigurasi ulang yang terhubung ke inti CPU berfrekuensi tinggi tetap. Aplikasi lain adalah keamanan: beberapa perusahaan ingin menyembunyikan rahasia mereka dalam logika yang dapat dikonfigurasi ulang daripada menunjukkan tata letak logika tetap mereka kepada peneliti termotivasi dengan mikroskop elektron dan banyak waktu.

Tetapi ada lebih sedikit pemain di dunia FPGA, misalnya, berikut adalah dua perusahaan yang melisensikan desain blok FPGA yang dapat tertanam dalam sirkuit tetap multi-run untuk memberi mereka fleksibilitas.

Setiap DAC memiliki beberapa vendor papan FPGA. Bukan vendor papan siswa murah seperti Digilent dan Terasic, yang mulai dari $ 55, tetapi papan FPGA untuk prototipe ASIC yang dapat biaya $ 30.000, $ 100.000 atau lebih.

DAC secara tradisional dihadiri oleh produsen papan FPGA. Mereka tidak menjual kartu pelajar murah seharga $ 55 dolar, tetapi papan FPGA serius seharga $ 55 _ ribu dolar dan lebih banyak lagi. Klien mereka bukan mahasiswa, tetapi tim pengembangan ASIC parah yang menggunakan papan besar untuk membuat prototipe.

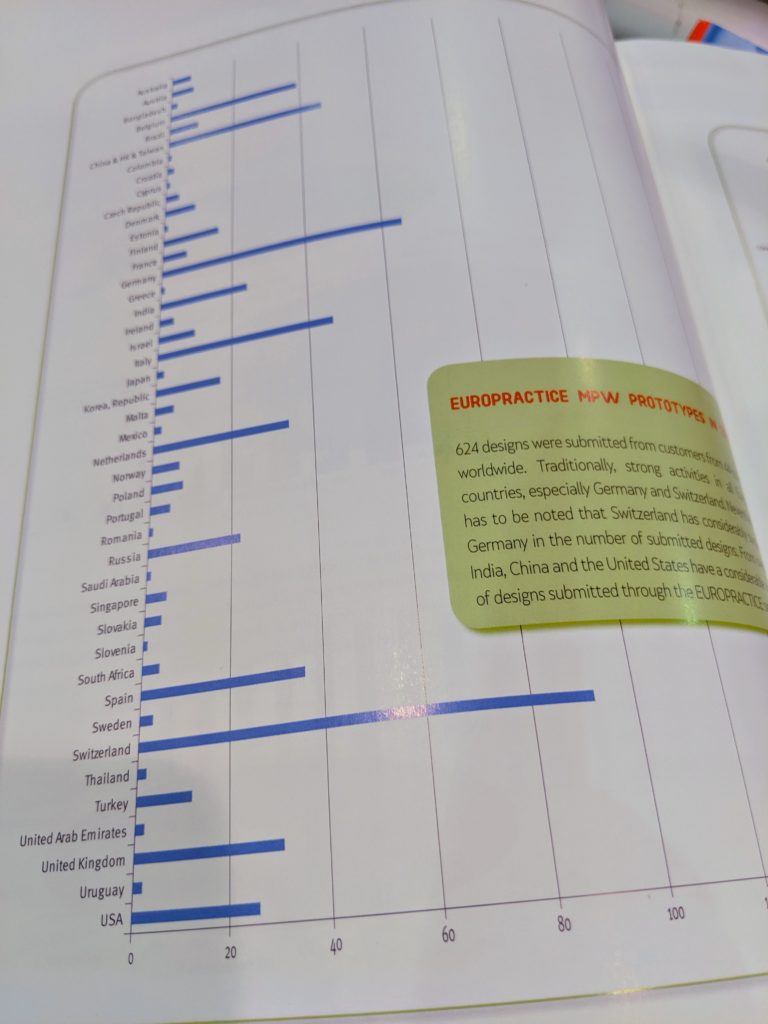

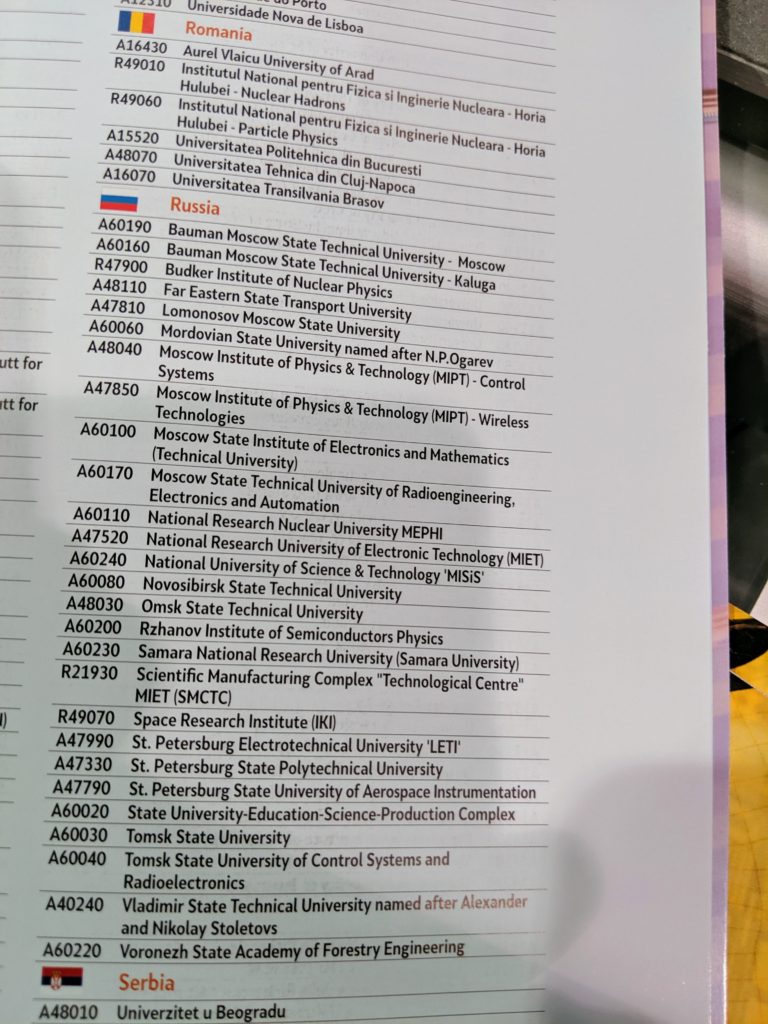

Bagaimana jika seorang peneliti melakukan beberapa bukti konsep menggunakan FPGA dan sekarang ingin membuat ASIC sendiri? Pesanan komersial tipikal untuk memproduksi ASIC biasanya membutuhkan pembayaran awal dari ~ $ 300 ribu hingga ~ $ 3.000.000 tergantung pada teknologi proses. Namun ada perusahaan khusus, Europractice di Eropa dan MOSIS di AS, yang menjual layanan "antar-jemput" dalam jumlah kecil, atau layanan multi-proyek wafer (MPW), mulai dengan hanya $ 3000 untuk teknologi 180nm atau hanya puluhan ribu dolar untuk sesuatu yang modern, seperti 28nm.

Tetapi bagaimana jika seorang siswa atau perusahaan yang keras ingin membuat ASIC nyata di pabrik, dan ada sedikit atau sedikit uang? Atau, jika tidak menyesal, apakah itu chip uji atau batch yang sangat kecil? Untuk melakukan ini, di Amerika ada perusahaan MOSIS, dan di Eropa - Europractice. Beberapa ribu dolar - dan Anda memiliki chip yang Anda rancang untuk teknologi seperti 180 nanometer. Beberapa puluh ribu - dan Anda memiliki chip Anda pada teknologi yang lebih baru, misalnya 28 nanometer, seperti iPhone kelima. Saya perhatikan bahwa untuk produksi komersial massal pembayaran awal ke pabrik adalah dari ratusan ribu dolar untuk teknologi lama hingga dua atau tiga juta untuk yang baru.

Sangat menarik bahwa Europractice memiliki pelanggan di Rusia, bahkan di Omsk. Akui siapa yang mendesain ASIC di Omsk.

Europractice memiliki sejumlah perusahaan Rusia, termasuk seseorang di Omsk:

Ada perusahaan dengan model bisnis yang agak misterius bagi saya. Sebagai contoh, saya tidak mengerti bagaimana perusahaan di bawah ini dapat bertahan hidup di plugin niche Eclipse. Saya kira mereka mendapatkan sebagian besar pendapatan dengan menjual beberapa layanan konsultasi.

Ada perusahaan yang saya tidak mengerti bagaimana mereka menghasilkan. Sebagai contoh, yang satu ini menjual plugin Eclipse yang sangat khusus. Tentunya mereka tidak hidup pada dirinya, tetapi pada semacam konsultasi.

Perusahaan niche lain dengan model bisnis yang tidak jelas. Mereka menerjemahkan deskripsi register yang terlihat oleh perangkat lunak ke dalam logika lem Verilog dan file antarmuka lainnya. Saya kira perusahaan ini mungkin memiliki beberapa pelanggan besar tipe Cisco yang sudah lama terpikat dengan teknologi mereka dan membayar mereka sejak saat itu.

Perusahaan niche lain dengan model bisnis yang tidak terlihat. Mereka menerjemahkan deskripsi register yang tersedia untuk programmer ke dalam file Verilog dan antarmuka. Mereka mungkin memiliki beberapa klien besar seperti Cisco, yang bertahun-tahun lalu jatuh cinta pada alat mereka, dan sejak itu membayar karena mengecewakan untuk menyewa klien untuk mengelola insinyur mereka.

Seorang pria melankolis dari Huawei menggambarkan pencapaian mereka dalam chip jaringan. Huawei jelas tergantung pada alat EDA AS, bahkan lebih dari pada pasar Android dan core CPU ARM. Jumlah uang mereka dan jumlah pakar teknis yang diperlukan untuk mengembangkan setara dengan kompiler Synopsys IC jauh lebih besar, menurut saya, daripada sumber daya yang dibutuhkan untuk merancang pesaing kelas atas untuk core ARM.

Perwakilan Huawei juga duduk di pameran dengan ekspresi kesedihan yang cerah di wajahnya. Saya perhatikan bahwa jika pemerintah AS memaksa perusahaan EDA AS untuk melarang Cina, situasi China akan jauh lebih buruk daripada sekarang, karena secara teknis lebih sulit untuk mengkloning IC Compiler Synopsys daripada core prosesor ARM dan Android Market.

Setiap DAC sejak tahun 1998 memiliki setidaknya satu perusahaan yang sedang mengembangkan kompiler C-to-Verilog. Kembali pada tahun 1998 itu adalah

startup saya sendiri . Tahun ini adalah orang lain:

Sejak 1998, setidaknya ada satu perusahaan di DAC yang mengkompilasi C di Verilog. Pada tahun 1998, perusahaan seperti itu adalah startup saya sendiri. Tahun ini orang lain:

Pria ini mencari nafkah dengan menjual solusi yang melawan apa yang disebut "Zakladki" (istilah Rusia, jamak dari "Zakladka"). Saya menjelaskan kepadanya arti dari istilah tersebut dan dia setuju bahwa ini adalah apa yang dia jual.

Berikut adalah pendamping yang membuat bookmark analisis hidup dalam prosesor:

Saya membawa ke DAC putri murid saya sehingga dia bisa melihat bagaimana ayah dapat hidup:

Saya membawa putri saya ke Las Vegas sehingga dia bisa melihat bagaimana orang menghasilkan uang di dunia industri yang keras dari industri elektronik dan menyadari bahwa dolar ayah tidak tumbuh di pohon:

Pesta setelah pameran:

Di pesta setelah pameran:

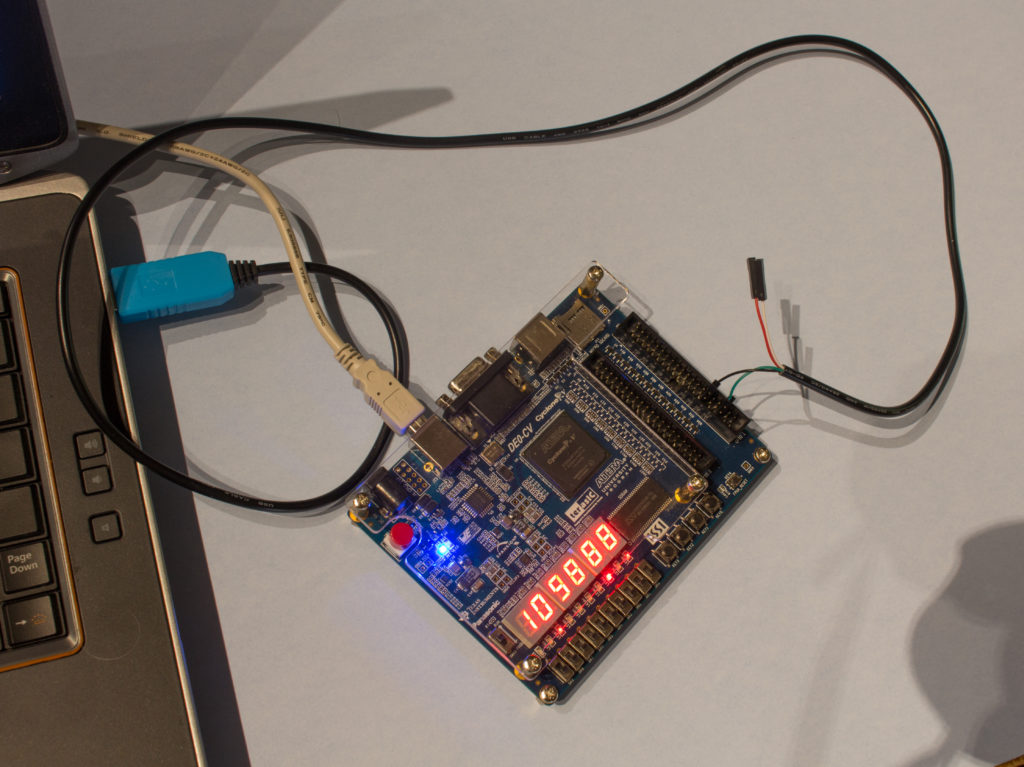

Setelah pameran saya melakukan MIPS Open Developer Day bersama rekan-rekan saya dari Wave Comnputing. Kami mendapat sejumlah orang dari beberapa perusahaan di atas + teman-teman Rusia saya dari

Viveng , layanan desain sinyal campuran California Silicon Valley yang juga memiliki beberapa pelanggan di Zelenograd, sebuah Lembah Silikon Rusia. Pertama kami membuat

presentasi , kemudian para peserta melakukan beberapa latihan pada papan Digilent Nexys4 DDR dan Terasic DE10-Lite FPGA.

Kemudian, bersama rekan-rekan saya, saya mengadakan seminar MIPS Open. Dia dikunjungi oleh kawan-kawan dari beberapa perusahaan yang dijelaskan, termasuk mereka yang melisensikan alat FPGA dan EDA, menjual layanan untuk produksi, melakukan pelatihan verifikasi, dan juga membuat keripik seperti itu. Dan juga teman lama saya dari perusahaan Rusia

VivEng . Rekan-rekan saya dan saya menunjukkan

slide-slide ini , setelah itu para peserta mencoba contoh-contoh pada FPGA Digilent Nexys4 DDR dan Terasic DE10-Lite.

Untuk mengulangi hasilnya, Anda dapat mengunduh dan menggabungkan dua paket:

Jika Anda ingin mereproduksi hasil, Anda dapat melakukan hal berikut:

- Pergi ke https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started-guide .

- Unduh paket MIPSfpga 2.0 standar.

- Buka https://github.com/MIPSfpga/mipsfpga-plus .

- git clone github.com/MIPSfpga/mipsfpga-plus.git

- Salin file RTL inti dari MIPS Buka paket FPGA ke subdirektori inti paket MIPSfpga + - lihat instruksi di https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core

Baik Intel FPGA Quartus Prime Lite Edition atau Xilinx Vivado, serta Codescape GCC Bare Metal Toolchain harus diinstal pada komputer Anda. Setelah itu, Anda dapat mengikuti instruksi dari slide:

Anda harus menginstal Intel FPGA Quartus Prime Lite Edition atau Xilinx Vivado di sistem Anda, serta Codescape GCC Bare Metal Toolchain. Setelah ini, Anda dapat mengikuti instruksi dari slide:

- cd your_git_directory / boards / board_directory (misalnya de10_lite atau nexys4_ddr)

- buat semua beban

- Tekan reset (atau KEY 0 pada beberapa papan) untuk mengatur ulang prosesor.

- Program hardcoded default harus mulai bekerja.

- cd your_git_directory / programs / 00_counter (atau program lain)

- membuat program srecord uart

- Jika komputer menggunakan koneksi serial selain ttyUSB0 (default), maka:

- buatlah program merekam uart UART = 1 (atau 2, 3, dll)

- Program yang diunggah melalui USB-ke-UART sekarang sedang berjalan.

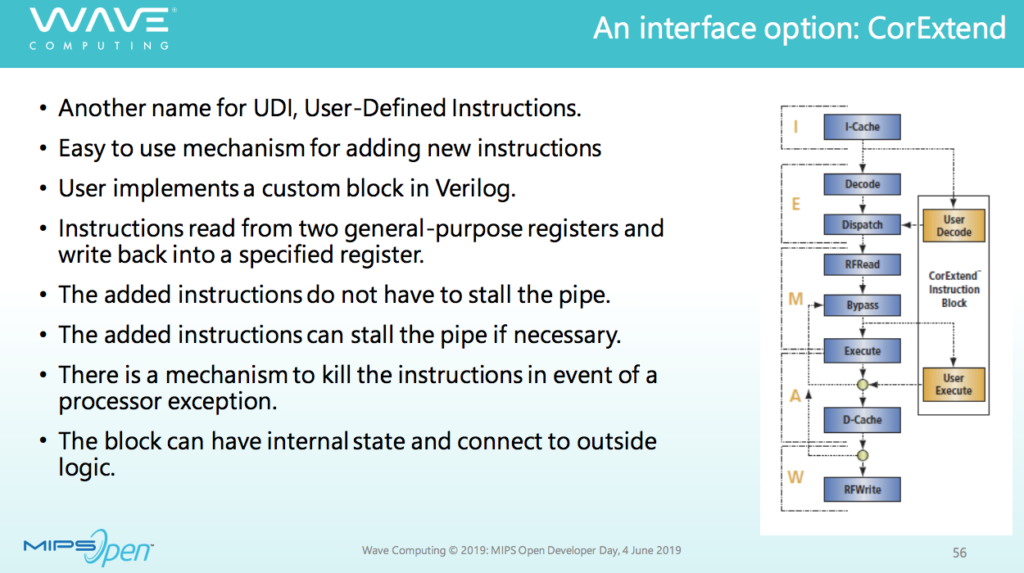

Dalam presentasi, saya menunjukkan cara menanamkan blok di prosesor yang menerjemahkan dan mengeksekusi instruksi tambahan ke sistem utama perintah yang dapat ditentukan oleh perancang sistem pada sebuah chip. Blok dapat disintesis dan menjadi bagian dari sirkuit mikro atau dikonfigurasi dalam FPGA / FPGA.

Instruksi tambahan bergerak di sepanjang pipa prosesor bersama dengan yang utama. Mereka menerima data dari register umum yang terlihat oleh programmer dan dapat mengembalikan hasilnya ke register. Instruksi ini juga dapat menyimpan beberapa status di coprocessor. Mereka dapat dibunuh oleh pengecualian jika pengecualian terjadi, misalnya, dalam pipa mengikuti instruksi ini:

Presentasi memiliki penjelasan terperinci, cara menambahkan instruksi prosesor yang ditentukan pengguna ke inti CPU MIPS microAptiv UP dan mensintesisnya bersama dengan beberapa SoC sederhana untuk papan FPGA:

Cuplikan kode perangkat keras Verilog dari teks sampel. Kode ini mengimplementasikan, pada Level Transfer Transfer (RTL), instruksi khusus untuk menghitung jaringan saraf convolutional:

Sebuah fragmen dari modul CorExtend kustom yang mengimplementasikan Instruksi yang Ditentukan Pengguna (UDI) untuk kasus khusus perhitungan neural net:

Besok saya terbang ke Rusia untuk membantu seminar lain, bukan untuk para profesional elektronik dan EDA, tetapi untuk anak-anak yang tertarik mengeksplorasi karier dalam desain mikroelektronika digital. Untuk perjalanan ini saya membuat videoprocessor 2D sederhana yang diintegrasikan dengan MIPS Open FPGA core, serta contoh permainan hanya perangkat keras (tanpa CPU atau perangkat lunak) untuk VGA. Anak-anak suka game dan saya akan menggunakan desain game untuk mengajari mereka dasar-dasar metodologi RTL:

Dan Senin depan

, 8 Juli, saya akan mengajarkan dasar-dasar pengembangan sirkuit digital untuk anak sekolah di Zelenograd .

Baginya, saya menulis contoh penerapan grafik sprite sederhana pada FPGA. Sebuah sirkuit yang disintesis dari Verilog menarik sprite pada layar VGA.

Berikut ini adalah contoh yang berfungsi dalam perangkat keras bersih (

kode sumber pada github ). Varian dari pertempuran laut, di mana satelit torpedo merah memburu salib biru musuh:

Dan di sini adalah contoh kombinasi perangkat keras dan perangkat lunak - penghormatan dari sprite.

Bagian perangkat keras dan

perangkat lunak :

Ya, dan saya berjanji akan memberikan pidato di Las Vegas. Ini adalah bagian:

Lihat Las Vegas Strip saat hari mulai gelap tetapi belum ada orang banyak:

Dan pemandangan jalan di strip, saat ini sudah malam, tetapi belum ada orang banyak:

Selama dua hari di Las Vegas saya tidak mendapat kesempatan untuk bertaruh, jadi saya bermain dengan $ 1 ketika pesawat kami kembali ke San Jose naik di bandara Las Vegas:

Selama ini, saya tidak pernah bermain di Las Vegas, karena saya berjalan di sekitar pameran dan berbicara tentang topik elektronik, kemudian saya mengadakan seminar. Namun saat naik ke pesawat, saya mencatat, kehilangan satu dolar: