Artikel ini akan menjelaskan instalasi dan penggunaan perangkat lunak gratis untuk pemodelan sirkuit logika digital di Verilog sebagai alternatif untuk produk komersial Incisve dari Cadense dan ModelSim dari MentorGraphics. Perbandingan simulasi dalam ModelSim dan Verilator. Metodologi verifikasi universal, UVM, juga akan dipertimbangkan.

Instalasi Perangkat Lunak SystemC UVM

1. Verilator

Salah satu bahasa deskripsi perangkat keras adalah Verilog. Anda dapat menulis modul dalam bahasa ini.

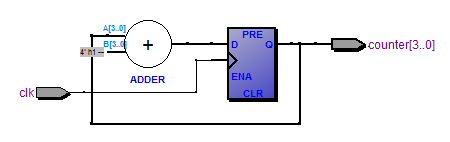

Misalnya, ada skema penghitung:

Kodenya akan terlihat seperti ini:

reg [3:0]counter; always @(posedge clk or posedge reset) if(reset) counter <= 4'd0; else counter <= counter + 1'd1;

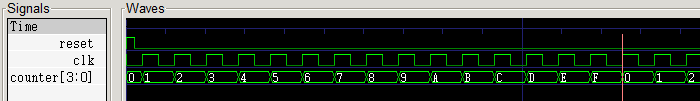

Setelah simulasi, kami mendapatkan bentuk gelombang:

Dapat dilihat bahwa nilai berikutnya, satu lebih dari yang sebelumnya, akan ditulis ke register penghitung di sepanjang frekuensi depan.

Modul tertulis dapat memiliki struktur yang lebih kompleks, yang akan sulit untuk memverifikasi semua keadaan secara manual. Kami akan membutuhkan pengujian otomatis. Untuk ini, perlu untuk mengembangkan lingkungan pengujian di salah satu bahasa pemrograman. Lingkungan pengujian akan memberi kita kesempatan untuk melakukan pemeriksaan fungsional penuh perangkat.

Untuk menguji kode proyek, selain bahasa seperti Verilog, SystemVerilog, Python (untuk model penulisan), Anda dapat menggunakan bahasa

SystemC . SystemC adalah desain tingkat bahasa sistem dan verifikasi untuk model tingkat sistem diimplementasikan sebagai perpustakaan C ++ open source.

Salah satu cara untuk memverifikasi modul Verilog menggunakan SystemC adalah menerjemahkan file Verilog ke C ++. Bantu kami dengan Verilator ini.

Verilator adalah simulator Verilog HDL tercepat gratis yang melampaui sebagian besar simulator komersial. Verilator mengkompilasi SystemVerilog yang disintesis (biasanya ini bukan kode testbed), serta beberapa pernyataan SystemVerilog dan Sintesis menjadi kode C ++ atau SystemC tunggal atau multi-berulir. Verilator dirancang untuk proyek besar di mana kinerja simulasi sangat penting dan sangat cocok untuk menghasilkan model prosesor yang dapat dieksekusi untuk tim pengembangan perangkat lunak tertanam. Verilator digunakan untuk mensimulasikan banyak desain gateway bernilai jutaan dolar dengan ribuan modul dan didukung oleh banyak penyedia teknologi IP, termasuk IP dari Arm dan semua penyedia IP RISC-V yang terkenal.

Verilator mungkin bukan pilihan terbaik jika Anda mengharapkan pengganti berfitur lengkap untuk NC-Verilog, VCS atau simulator Verilog komersial lainnya, atau simulator perilaku Verilog untuk proyek yang sangat kecil. Namun, jika Anda mencari cara untuk mem-port Verilog yang disintesis ke C ++ atau SystemC, dan tim Anda bebas menulis hanya kode C ++, ini adalah kompiler Verilog gratis untuk Anda.

Untuk menginstal versi terbaru di Ubuntu: unduh arsip

dari tautan dari situs resmi .

Pasang:

2. GTK Wave

GTKWave adalah penampil bentuk gelombang fitur lengkap dan juga memungkinkan Anda untuk mengkonversi file dari format vcd ke fst, lebih nyaman dan lebih cepat.

Pasang:

sudo apt-get install gtkwave

3. SYSTEMC

Bahasa untuk merancang dan memverifikasi model tingkat sistem yang diterapkan dalam bentuk pustaka C ++ sumber terbuka.

Seperti disebutkan sebelumnya, verilator mendukung systemc, jadi Anda perlu membuat proyek di mana tolok ukur pengujian akan dijelaskan pada systemc, dan file sumber pada Verilog yang disintesis. Untuk melakukan ini, kita memerlukan pustaka compiler g ++ yang disediakan oleh Accelera. Accellera Systems Initiative adalah organisasi nirlaba independen yang didedikasikan untuk menciptakan, mendukung, mempromosikan dan mempromosikan standar tingkat desain, simulasi dan verifikasi sistem untuk digunakan dalam industri elektronik global.

Unduh arsip:

http://accellera.org/images/downloads/standards/systemc/systemc-2.3.1a.tar.gzPasang:

tar -xvf systemc-2.3.1a.tar.gz cd systemc-2.3.1a mkdir objdir sudo ./configure --prefix=/usr/local/systemc-2.3.1a/ sudo make sudo make install cd ../

4. UVM untuk SYSTEMC

Artikel ini akan meninjau proyek yang mengimplementasikan alat verifikasi UVM. Verifikasi adalah konfirmasi kesesuaian produk akhir dengan persyaratan referensi yang telah ditentukan. Salah satu alat verifikasi mereka dapat berupa tes. Untuk menjalankan urutan pengujian pada model perangkat nyata di tingkat deskripsi RTL, perlu untuk mengembangkan lingkungan pengujian.

UVM - (Metodologi Verifikasi Universal) adalah metodologi verifikasi universal, standar yang memungkinkan pengembangan yang efisien dan penggunaan ulang lingkungan validasi blok IP. UVM adalah metodologi verifikasi yang tugasnya meliputi mengatur lingkungan yang efektif di sekitar unit yang diuji. Keuntungannya:

- struktur yang jelas dalam bentuk blok khusus yang memutuskan khusus

- tugas

- kemampuan untuk menggunakan kembali blok dalam proyek selanjutnya;

- otomatisasi maksimum verifikasi;

- informasi pelaporan terlengkap yang memungkinkan, ketika kesalahan terjadi, untuk mengidentifikasi penyebabnya secepat dan seakurat mungkin dan menyarankan solusi.

Metodologi UVM terdiri dari dua bagian: seperangkat aturan untuk membangun lingkungan pengujian dan perpustakaan blok kosong untuk verifikasi, misalnya, generator teks, pengumpul statistik, dll. Keuntungan utama dari UVM adalah fleksibilitas dan kompatibilitasnya dengan lingkungan pihak ketiga.

Karena systemc mendukung metodologi UVM, mari beralih ke menginstal perpustakaan yang diperlukan.

Unduh arsip:

https://www.accellera.org/images/downloads/drafts-review/uvm-systemc-1.0-beta2.tar.gzPasang:

tar -xvf uvm-systemc-1.0-beta2.tar.gz cd uvm-systemc-1.0-beta2/ mkdir objdir sudo ./configure --prefix=/usr/local/systemc_uvm/ --with-systemc=/usr/local/systemc-2.3.1a sudo make sudo make install

Kami membuat aliansi:

sudo mkdir /usr/local/uvm_systemc_aliance

Salin isi folder / usr / local / uvm_systemc_aliance / dan /usr/local/systemc-2.3.1/ ke folder ini

Unduh proyek yang sudah selesai di tautan:

https://github.com/paprikun/SYSTEMC/Buka folder contoh verilator.

Folder rtl berisi deskripsi perangkat. Dalam contoh ini, ini adalah pengontrol PWM.

Dalam folder sim file makefile untuk membangun proyek.

Di folder tb adalah kode untuk verifikasi. Folder tb / uvm berisi contoh lingkungan uvm. File utama adalah titik masuk dalam pengujian, menghubungkan perangkat yang sedang diuji dengan lingkungan uvm.

Kami mencoba membangun proyek dari folder sim dengan perintah make all. Kami melihat kesalahan:

/usr/local/uvm_systemc_aliance//include/systemc.h:120:16: error: 'std::gets' has not been declared using std::gets;

Kami memperbaikinya dengan mengganti baris 120:

#if defined(__cplusplus) && (__cplusplus < 201103L) using std::gets; #endif

Sekali lagi, kami mencoba menjalankan testbench dan menemukan peringatan:

/usr/local/uvm_systemc_aliance//include/sysc/packages/boost/get_pointer.hpp:21:40: warning: 'template<class> class std::auto_ptr' is deprecated [-Wdeprecated-declarations] template<class T> T * get_pointer(std::auto_ptr<T> const& p)

Ubah auto_ptr ke unique_ptr.

Perakitan dan simulasi proyek

Sekarang perpustakaan sudah terpasang dan berfungsi, kami sedang membangun proyek: make all. File executable simu akan muncul di folder sim. Ini adalah objek yang dibuat oleh kompiler. Kami memulainya dengan tim ./simu. Berikut ini akan muncul:

SystemC 2.3.1-Accellera --- Jun 28 2019 11:39:29 Copyright (c) 1996-2014 by all Contributors, ALL RIGHTS RESERVED Universal Verification Methodology for SystemC (UVM-SystemC) Version: 1.0-beta2 Date: 2018-10-24 Copyright (c) 2006 - 2018 by all Contributors See NOTICE file for all Contributors ALL RIGHTS RESERVED Licensed under the Apache License, Version 2.0 UVM_INFO @ 0 s: reporter [RNTST] Running test ... simulation real time = 9 sec UVM_INFO uvm_default_report_server.cpp(666) @ 179490249010 ps: reporter [UVM/REPORT/SERVER] --- UVM Report Summary --- ** Report counts by severity UVM_INFO : 1 UVM_WARNING : 0 UVM_ERROR : 0 UVM_FATAL : 0 ** Report counts by id [RNTST] 1 UVM_INFO @ 179490249010 ps: reporter [FINISH] UVM-SystemC phasing completed; simulation finished

Ketika simulasi selesai, rekaman wafeform berakhir. File simu.vcd dapat dibuka dengan gtkwave:

Untuk menampilkan sinyal di sebelah kiri, pilih SystemC, lalu tahan Shift pilih sinyal apa saja, dan klik Tambah. Tooltips muncul di bilah alat saat Anda mengarahkan kursor. Gulir mouse berfungsi, Anda harus menahan shift atau cntrl.

Ada juga cara untuk mengonversi file ini ke file lain yang lebih kecil.

Jika ada modelsim akan melakukan konversi. Di terminal, masukkan perintah vsim. Di modelsim terminal:

vcd2wlf simu.vcd simu.wlf

Atau menggunakan gtkwave di terminal linux:

vcd2lxt simu.vcd simu.lxt vcd2lxt2 simu.vcd simu.lxt2

Untuk membandingkan waktu simulasi, proyek serupa telah dibuat, tetapi sudah untuk

Modelsim . Map modelsim_example. Demikian pula menciptakan lingkungan UVM. Sintaksnya sama meskipun faktanya berbeda bahasa. Jika Anda menginstal Modelsim dengan dukungan uvm, Anda dapat menjalankan perintah make all.

Selain lingkungan di kedua proyek, simulasi pengukuran real-time juga dilakukan.

Akhirnya, perbedaannya adalah:

Seperti yang dapat Anda lihat dari tabel, verilator memiliki keuntungan. Data disajikan untuk PC dengan RAM 8GB, prosesor 8-inti, 800 MHz, memuat satu inti.

Bandingkan ukuran file:

Di sini verilator hilang, tetapi Anda dapat bereksperimen dengan membuat bentuk gelombang dan melacak kedalaman, periode perekaman (awal dan akhir rekaman bentuk gelombang dapat digeser). File mana yang harus dikerjakan terserah Anda.

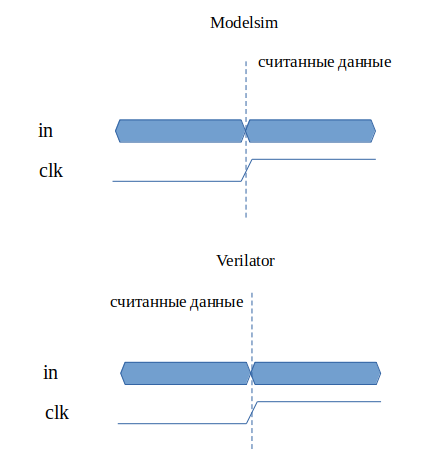

Selama pengujian, selain waktu simulasi itu sendiri, perbedaan ditemukan dalam pembacaan data input dari dalam bus. Jika data dari dalam bus berubah selama front clk, Modelsim membaca data setelah front, verilator sebelumnya:

input clk; input [7:0] in; reg [7:0] in_last_ ; ... always @(posedge clk) begin ... in_last_ <= in; ... end

Selama pengujian, poin ini perlu diperhitungkan, karena bagian dari lingkungan pengujian untuk berbagai simulator akan bekerja secara berbeda.

Juga, verilator tidak memperhitungkan keadaan "x" dari sinyal dan menerjemahkan semuanya menjadi "0";

UVM TESTBENCH

Pertimbangkan lingkungan pengujian, folder tb / uvm.

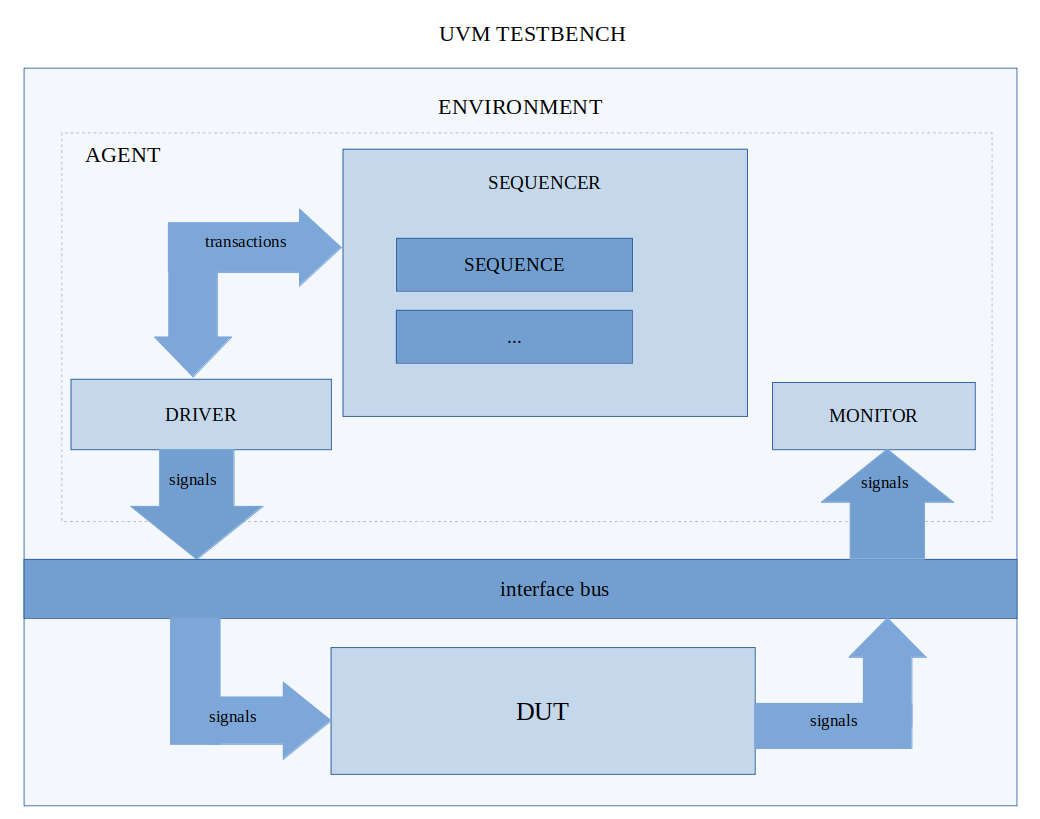

Testbench UVM adalah lingkungan di atas perangkat. Dalam contoh ini, perangkat adalah pengontrol PWM. Diagram lingkungan UVM:

Seperti yang Anda lihat dalam diagram, UVM terdiri dari blok (kelas). Setiap blok menjalankan fungsinya. Contoh menunjukkan salah satu tata letak yang mungkin dari lingkungan pengujian. Nama dan fungsionalitas masing-masing kelas sesuai dengan kelas dari mana ia diwarisi. Mari kita bahas masing-masing kelas secara lebih rinci.

File lingkungan env.h atau env.svh. Ini adalah kelas yang bisa berisi satu atau lebih kelas agen, di mana tiga kelas terhubung: sequencer, driver, monitor. Tidak ada agen dalam contoh, tetapi fungsinya diimplementasikan di kelas env. Untuk pengujian kita perlu menulis beberapa urutan tindakan - urutan.

Mari beralih ke kode awal pengurutan:

sequence_[n]->start(sqr, NULL);

Sequencer (sequencer) - file sequncer.h. Di sistem Verilog, ternyata menggunakan sequencer default. Kelas yang berisi satu atau lebih urutan (urutan) (file sequence_a.h, sequence_a.svh). Setiap urutan adalah rangkaian tindakan. Salah satu tindakan ini mungkin mengirim transaksi. Transaction - mentransfer data dari satu kelas ke kelas lain. Kelas di mana transaksi dijelaskan adalah bus_trans. Di bawah ini adalah deskripsi dari dua kelas, yang masing-masing secara ideologis memiliki fungsi spesifiknya sendiri: driver dan monitor.

Driver - file drv.h, drv.svh. Kelas yang menerima transaksi dari sequencer dan menerjemahkannya menjadi sinyal. Pengemudi berfungsi sebagai asisten sequencer di level yang lebih rendah. Pertimbangkan mengirim satu paket.

Urutan membuka jendela transaksi, pengemudi mendeteksi peristiwa ini dan mulai menerima data. Urutan menunggu respons dari pengemudi. Pengemudi mensimulasikan sinyal untuk perangkat, kemudian memberi sinyal sequencer bahwa jendela dapat ditutup. Idenya adalah bahwa sequencer bekerja pada level tinggi, dan driver pada level lebih rendah.

Sinyal terhubung melalui bus antarmuka ke perangkat. Antarmuka dijelaskan dalam file vip_if.h, vip_if.svh.

Selanjutnya, Anda perlu memeriksa apakah sinyal output cocok dengan yang diharapkan. Ada dua solusi:

- Menulis model untuk perangkat

- Verifikasi Sinyal melalui Agen UVM

Dalam contoh tersebut, opsi kedua dipertimbangkan. Untuk menguji perangkat pada level fungsional, perlu membandingkan output dengan yang diharapkan. Persyaratan untuk perangkat adalah kebenaran siklus tugas sinyal dan periode sinyal. Untuk memantau sinyal output, kelas baru ditulis - Monitor (file monitor.h, monitor.svh). Biasanya, dalam lingkungan pengujian, monitor mentransfer sinyal dalam transaksi (ke tingkat yang lebih tinggi) dan dikirim ke papan skor kelas pembanding.

Dalam contoh ini, sinyal diperiksa segera. Dalam hal perbedaan antara nilai yang diharapkan dan yang diukur, tes berhenti.