Proses manufaktur menengah, berbagai jenis transistor, dan banyak opsi lain menambah ketidakpastian pada proses manufaktur elektronik.

Pabrikan elektronik bersiap untuk gelombang berikutnya dari proses manufaktur mutakhir, tetapi pelanggan mereka akan bingung dengan banyak pilihan yang membingungkan - apakah akan mengembangkan chip menggunakan teknologi proses 5 nm, menunggu 3 nm, atau memilih sesuatu di antaranya.

Jalan menuju 5 nm didefinisikan dengan baik, tidak seperti 3 nm. Setelah itu, lanskap menjadi bingung karena pabrik menambahkan proses manufaktur menengah, seperti 6 nm dan 4 nm. Beralih ke salah satu dari proses teknis ini sangat mahal, dan manfaatnya tidak selalu jelas.

Penyebab lain yang perlu dikhawatirkan adalah menyusutnya basis manufaktur. Dalam kasus proses teknis paling maju, pilihan produsen kecil. Ada beberapa produsen terkemuka di industri ini, tetapi seiring waktu area ini telah menyempit karena kenaikan tajam dalam biaya dan penurunan basis pengguna. Secara umum, semakin sedikit produsen, semakin sedikit pilihan untuk teknologi dan label harga.

Saat ini, Samsung dan TSMC adalah

satu -

satunya dua produsen yang bekerja dengan proses teknologi 7 nm atau lebih rendah, meskipun ini dapat berubah. Intel dan SMIC perusahaan Cina sedang mengembangkan proses manufaktur tingkat lanjut. Intel, bukan pemain terbesar di bidang produksi komersial, sedang mengalami masalah dengan pengembangan teknologi proses 10 nm. Dan tidak jelas apakah SMIC akan dapat memberikan 7 nm, karena topik ini masih dalam tahap penelitian dan pengembangan (hal yang sama terjadi pada Intel dengan teknologi proses 10 nm).

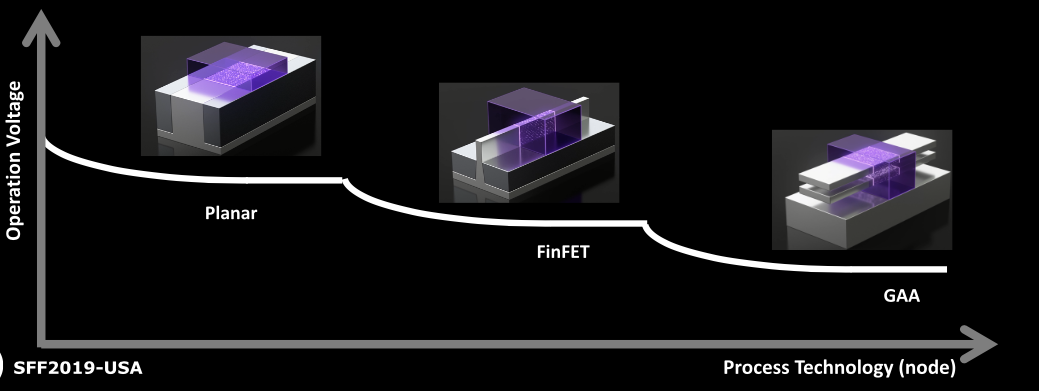

Adapun proses pembuatan yang lebih maju, Samsung dan TSMC bekerja dengan 7 nm menggunakan transistor finFET, dan kedua produsen akan melanjutkan ini pada 5 nm. Tidak seperti transistor planar tradisional, finFET adalah struktur tiga dimensi dengan kinerja yang lebih baik dan lebih sedikit kebocoran.

Kemudian pada 3 nm Samsung akan bergerak dari finFET ke arsitektur transistor FET nanosheet baru, yang merupakan pengembangan teknologi finFET. TSMC belum mengungkapkan rencananya untuk 3 nm, meninggalkan banyak pelanggan dalam kesulitan. TSMC, menurut sumber, menimbang berbagai pilihan, termasuk nanolayers, kawat nano dan finFETs paksa. Intel, TSMC, dan lainnya juga sedang mengerjakan bentuk kemasan canggih baru sebagai opsi yang memungkinkan untuk downscaling.

Namun, pada 3 nm ukuran teknologi transistor dapat bergerak ke arah yang berbeda. finFET masih bisa bermain, tetapi teknologi ini membutuhkan beberapa terobosan. Tampaknya, industri harus mempersiapkan transisi ke arsitektur baru teknologi proses 3 nm, dan teknologi proses menengah berikutnya pada 2 nm, dilihat dari rencana pengembangan satu organisasi yang bekerja di bidang ini.

"5 nm masih finFET," kata Naoto Horiguchi, direktur program di Imec. - Katakanlah pada 3 nm kita akan memasuki masa transisi dari finFET ke arsitektur lain. Kami percaya bahwa ini akan menjadi nanolayers. "

FET Nanolayer berhubungan dengan arsitektur gate-all-around transistor (GAA). Dan ini bukan satu-satunya pilihan. “Industri ini sangat konservatif. Para pesertanya akan mencoba memeras segala sesuatu dari finFET hingga batasnya, ”kata Horiguchi. - Pada proses manufaktur 3 nm, kami memiliki kesempatan untuk menggunakan finFET. Tetapi kita perlu membuat beberapa inovasi finFET, memperbaikinya secara umum. ”

Akankah produsen chip tetap menggunakan teknologi proses 7 nm, bermigrasi ke 5 nm, 3 nm atau ke perantara? 7 nm memberikan kinerja yang cukup untuk hampir semua aplikasi, sehingga proses ini akan hidup untuk waktu yang lama. Di luar ada beberapa opsi kinerja tinggi, dan semuanya harganya lebih mahal. Dan kita akan melihat apakah teknologi ini memiliki waktu untuk muncul tepat waktu.

Tegangan operasi dari berbagai proses pembuatan adalah transistor planar, finFET dan FET nanolayer.

Tegangan operasi dari berbagai proses pembuatan adalah transistor planar, finFET dan FET nanolayer.Kehancuran produksi

Chip terdiri dari banyak transistor yang bertindak sebagai sakelar. Selama beberapa dekade, kemajuan sirkuit terpadu konsisten dengan hukum Moore, yang menurutnya kepadatan transistor pada perangkat berlipat ganda dalam periode 18 hingga 24 bulan.

Dalam ritme yang sama, pabrikan memperkenalkan proses teknologi baru dengan kepadatan transistor yang lebih tinggi, yang memungkinkan industri untuk mengurangi biaya chip dalam hal jumlah transistor. Pada setiap proses manufaktur, pabrikan meningkatkan spesifikasi transistor 0,7 kali, memungkinkan industri meningkatkan produktivitas hingga 40% dengan konsumsi energi yang sama dan pengurangan dua kali lipat dalam area.

Industri sirkuit terpadu mengikuti formula ini dan berkembang. Sejak 1980-an, itu telah membuka jalan bagi PC cepat dengan harga diskon.

Pada tahun 2001, sudah ada setidaknya 18 produsen dengan pabrik-pabrik di mana mereka dapat memproduksi chip pada 130 nm, yang pada saat itu merupakan proses teknis lanjutan, menurut IBS. Juga, beberapa produsen baru muncul, membuat chip buatan-custom di pabrik orang lain. Selain itu, pembuatan chip dipraktekkan untuk laboratorium yang mengembangkannya, tetapi tidak memiliki produksinya sendiri.

Pada akhir dekade ini, biaya produksi dan proses manufaktur melonjak. Tidak dapat mengatasi kenaikan harga, banyak produsen chip beralih ke model fab lite. Mereka memproduksi beberapa keripik di rumah, dan sisanya di-outsourcing-kan.

Seiring waktu, semakin sedikit produsen chip yang membuat perangkat canggih di fasilitas mereka sendiri. Beberapa benar-benar menyingkirkan produksi atau meninggalkan bisnis ini.

Namun, pada 2000-an, model bisnis bengkel silikon muncul. Lokakarya tertinggal di belakang Intel dan perusahaan teknologi lainnya, tetapi memberi perusahaan desain akses ke berbagai proses.

Perubahan besar berikutnya terjadi pada tahap 20 nm, ketika transistor planar tradisional menabrak dinding dan mengalami

efek saluran pendek . Sebagai tanggapan, Intel beralih ke teknologi transistor generasi berikutnya, finFET, pada 22 nm pada tahun 2011. Lokakarya beralih ke finFET pada 16/14 nm.

FinFET memiliki beberapa keunggulan dibandingkan transistor planar. “Dalam skema ini, seluruh transistor memanjang secara vertikal sehingga saluran naik di atas substrat, dan katup membungkus di sekitar tiga sisi sirip. Area kontak yang meningkat dari katup memungkinkan kontrol yang lebih baik dari arus bocor, ”tulis Matt Kogorno dan Toshihiko Miyashita dari Bahan Terapan. Kogorno adalah direktur manajemen produk global, dan Miyashita adalah kepala teknolog.

FinFET juga merupakan perangkat yang lebih kompleks, lebih sulit untuk memproduksi dan menskalakannya untuk setiap proses teknis selanjutnya. Akibatnya, biaya R&D meningkat ke surga. Jadi sekarang ritme perubahan proses yang lengkap telah berkembang dari 18 bulan menjadi 2,5 tahun atau lebih.

Harga sirkuit terintegrasi juga terus meningkat. Biaya pengembangan perangkat planar pada 28 nm bervariasi dari $ 10 juta hingga $ 35 juta, menurut Gartner. Sebagai perbandingan, biaya merancang sistem chip tunggal (SoC) pada 7 nm bervariasi dari $ 120 juta hingga $ 420 juta.

"Biaya pengembangan sangat tergantung pada kompleksitas SoC," kata Samuel Wen, seorang analis di Gartner. - Dua pertiga pergi ke pengembangan chip. Sisanya adalah pengembangan kapal selam, biaya masker dan peningkatan output. Seiring waktu, biaya desain juga turun. "

Namun, tren harga telah mengubah lanskap dunia sirkuit terpadu. Seiring waktu, semakin sedikit perusahaan yang mampu membayar untuk desain chip untuk proses manufaktur paling maju. Banyak dari mereka bergantung pada bengkel untuk masalah produksi.

Penurunan jumlah pelanggan seiring dengan kenaikan biaya produksi memengaruhi lanskap bengkel yang memproduksi chip canggih. Misalnya, ada lima produsen / bengkel yang tersisa di pasar 16/14 nm: GlobalFoundries, Intel, Samsung, TSMC, dan UMC. SMIC juga bekerja dengan finFET pada teknologi proses 14 nm.

Dan pada 7 nm transisi lain terjadi. Proses teknologi dan biaya produksi terus tumbuh, dan laba atas investasi sudah dipertanyakan. Akibatnya, GlobalFoundries dan UMC tahun lalu berhenti berusaha mengembangkan teknologi proses 7 nm. Kedua perusahaan terus beroperasi di pasar 16/14 nm.

Berusaha mengembangkan lebih lanjut, Samsung dan TSMC bergegas dengan kecepatan penuh hingga pergantian 7 nm dan lebih tinggi. Setelah beberapa penundaan, Intel berencana untuk meluncurkan produksi pada 10 nm pada pertengahan 2019, dan pada 7 gm - pada tahun 2021. Sementara itu, SMIC tidak menjanjikan tenggat waktu.

Tetapi tidak semua pelanggan bengkel membutuhkan proses manufaktur tingkat lanjut. Ada pasar yang berkembang untuk chip 28 nm. "Itu semua tergantung pada karakteristik produk," kata Ven of Gartner. - Beberapa produk memerlukan kinerja maksimal. Pengembang masih dapat menggunakan proses teknis yang ketinggalan jaman. Dan chip untuk aplikasi yang tidak memerlukan kinerja tinggi dapat hidup pada proses pembuatan N-1 dan N-2. "

Lainnya menggemakannya. “Berapa banyak perusahaan yang mampu membeli silikon terbaru hari ini dari sudut pandang ekonomi? Jumlah mereka berkurang. Di pasar yang membutuhkan kinerja sangat tinggi, kebutuhan seperti itu akan selalu ada. Tetapi dalam rantai pasokan, dalam hal volume, bentuk pecah di tengah. Pelanggan yang paling menuntut membutuhkan proses teknologi pada 7, 5, dan mungkin suatu hari nanti 3 nm. Tetapi semua orang sedikit melambat, ”kata Walter Eun, wakil presiden manajemen bisnis di UMC.

Tetapi dalam kasus-kasus tertentu, ada kebutuhan untuk chip yang paling canggih - ini adalah server dan smartphone. Ada juga banyak startup baru yang terkait dengan chip AI. Banyak perusahaan mendesain chip untuk pembelajaran mesin dan pembelajaran mendalam.

“Tidak ada yang berpendapat bahwa kebutuhan untuk menghitung sesuatu 10 kali lebih cepat daripada hari ini akan selalu bermanfaat secara komersial dan kompetitif, bahkan di pasar non-teknis. Semua prestasi unik dari teknologi pembelajaran mendalam ini adalah bukti dari ini. Secara harfiah tidak ada akhir untuk permintaan daya komputer yang terus meningkat, ”kata Aki Fujimura, direktur D2S.

"Permintaan akan daya komputasi telah mengalami beberapa perubahan besar - pada awalnya itu adalah GPU, dan kemudian - pembelajaran yang mendalam," kata Fujimura. - Pembelajaran mendalam adalah teknologi besar untuk menemukan pola yang cocok, dan melatih jaringan saraf adalah tugas pengoptimalan yang konsisten. Sekarang dunia telah menciptakan mekanisme untuk memproses sejumlah besar data dan mengubahnya menjadi informasi yang berguna dalam bentuk program yang mampu menghasilkan kesimpulan logis, jumlah perhitungan yang diperlukan bertambah dengan jumlah data yang tersedia. Dan karena jumlah data di semua bidang tumbuh secara eksponensial, persyaratan untuk daya komputasi dijamin tumbuh secara signifikan, setidaknya di bidang pembelajaran yang mendalam. ”

Apakah chip AI memerlukan proses teknis 5 nm atau lebih masih belum jelas, tetapi pasti ada persyaratan untuk peningkatan daya komputasi. Tetapi migrasi ke proses teknologi ini tidak menjadi proses yang lebih mudah atau lebih murah.

5 nm vs 3 nm

Sementara itu, pada awal 2018 TSMC mencapai tonggak sejarah lain, menjadi produsen pertama di dunia yang menggunakan teknologi proses 7 nm. Samsung kemudian bergabung dengan balapan 7 nm. Proses pembuatan chip pada 7 nm terutama didasarkan pada finFET, dan terdiri dari chip manufaktur dengan langkah gerbang 56 hingga 57 nm dan langkah minimum menempatkan konduktor logam [pitch logam] pada 40 nm, menurut informasi dari IC Knowledge dan TEL.

Dalam versi pertama 7 nm, TSMC menggunakan

litografi perendaman 193 nm dan pola ganda. Tahun ini TSMC berjanji akan merilis versi baru 7 nm menggunakan ultraviolet lithography (EUV) ekstrim. EUV menyederhanakan langkah-langkah proses, tetapi ini adalah teknologi yang mahal dan memiliki serangkaian kesulitan sendiri.

TSMC sedang mempersiapkan teknologi proses 5 nm baru untuk rilis pada paruh pertama tahun 2020. Teknologi baru dari TSMC pada 5 nm akan 15% lebih cepat dari 7 nm, dan mengkonsumsi energi 30% lebih sedikit. Versi kedua dari teknologi proses 5 nm, yang keluar tahun depan, akan 7% lebih cepat. Kedua versi akan menggunakan EUV.

TSMC sudah mendapatkan pesanan pada 5 nm. "Pesanan besar diharapkan dari Apple, HiSilicon, dan Qualcomm," kata Handel Jones, Direktur IBS. "Volume media akan menjadi 40.000 - 60.000 per bulan pada kuartal keempat 2020."

Kecepatan transisi pada 5 nm untuk TSMC kurang dari 7 nm. Pertama, 5nm adalah proses yang sepenuhnya baru, dengan alat dan paten EDA yang diperbarui. Selain itu, harganya lebih mahal. Rata-rata, biaya pengembangan perangkat pada 5 nm bervariasi dari $ 210 juta hingga $ 680 juta, menurut Gartner.

Beberapa pembuat chip ingin menjauh dari 7nm tanpa menghabiskan uang sebanyak 5nm. Oleh karena itu, TSMC baru-baru ini memperkenalkan teknologi proses 6 nm baru, yang lebih murah, tetapi dengan beberapa kompromi.

"Angka-angka N6 dan N5 tampaknya tidak berbeda, tetapi pada kenyataannya kesenjangannya besar," kata S. S. Wei, direktur TSMC pada pertemuan terakhir. - Pada N5, dibandingkan dengan N7, kepadatan logis meningkat sebesar 80%. N6 dibandingkan dengan N7 hanya 18%. Seperti yang Anda lihat, ada perbedaan besar antara kepadatan logis dan efisiensi transistor. Hasilnya, konsumsi daya keseluruhan chip N5 lebih rendah. Ada banyak manfaat untuk beralih ke N5. Tapi N5 adalah proses teknis yang lengkap, dan butuh waktu bagi pelanggan untuk mengembangkan produk baru untuk itu. Keindahan N6 adalah bahwa jika mereka sudah memiliki proyek di bawah N7, maka mereka harus menghabiskan sedikit usaha. Mereka dapat meningkatkan ke N6 dan mendapatkan manfaat tertentu. Dan tergantung pada karakteristik produk dan pasar, pelanggan akan memutuskan apa yang harus dilakukan. "

Sementara itu, Samsung meluncurkan 5 nm, yang akan muncul pada paruh pertama tahun 2020. Dibandingkan dengan 7 nm, teknologi proses 5 nm baru Samsung di finFET memberikan pemadatan logika hingga 25% dan konsumsi daya 20% lebih sedikit, atau kecepatan 10% lebih banyak.

Samsung juga memperkenalkan teknologi proses 6 nm baru, memberi pelanggan pilihan lain. "6nm memiliki keunggulan skalabilitas dengan 7nm dan penggunaan kembali kekayaan intelektual," kata Ryan Lee, wakil presiden pemasaran untuk lokakarya di Samsung. Dan Samsung berencana sudah memiliki pengembangan teknologi proses 4 nm finFET. Sejauh ini, praktis tidak ada informasi terbuka tentang teknologi ini.

Setelah 5 nm, sejumlah proses manufaktur penuh memakan biaya 3 nm. Tapi 3 nm bukan untuk para pengecut. Biaya pengembangan perangkat untuk teknologi proses 3 nm berkisar dari $ 500 juta hingga $ 1,5 miliar, menurut IBS. Biaya proses pengembangan bervariasi dari $ 4 miliar hingga $ 5 miliar, dan produksi - dari $ 15 hingga $ 20. "Biaya 3 nm transistor harus 20-25% lebih dari 5 nm dari ketersediaan yang sama," kata Jones dari IBS. "Kita dapat mengharapkan peningkatan 15% dalam efisiensi dan pengurangan 25% dalam konsumsi energi dibandingkan dengan finFET 5 nm."

Samsung adalah satu-satunya perusahaan yang mengumumkan rencana untuk mengembangkan teknologi proses 3 nm. Untuk ini, bengkel akan beralih ke arsitektur transistor melingkar, nanolayer. TSMC belum mengungkapkan rencana, itulah sebabnya beberapa percaya bahwa perusahaan ada di belakang. "Pada 3nm, Samsung sangat mungkin untuk memasuki volume produksi pada tahun 2021," kata Jones. "TSMC mempercepat pengembangan dengan mencoba bersaing dengan Samsung."

Pada 3 nm, TSMC memeriksa FETs nanolayer, FET nanowire, dan bahkan finFET. Salah satu cara untuk memperluas teknologi finFET adalah dengan menggunakan bahan mobilitas tinggi di saluran, yaitu Jerman. Perangkat finFET saat ini menggunakan silikon atau silikon-germanium (SiGe) dalam saluran. Dengan meningkatkan campuran germanium, Anda dapat meningkatkan mobilitas saluran - yaitu, kecepatan perpindahan elektron melalui perangkat. Dan di sini masalahnya adalah manajemen cacat.

Memperluas teknologi finFET masuk akal. finFET pada 3 nm menyediakan jalur transisi dari 5 nm. Namun, ada masalah. Secara teoritis, teknologi finFET mengalami jalan buntu ketika lebar sirip mencapai 5 nm, yang mendekati kondisi saat ini. "Hari ini kami menggunakan dua sirip untuk NMOS dan tiga untuk PMOS dalam sel standar," kata Horiguchi dari Imec. - Salah satu aspek penting dari 3 nm adalah bahwa kita perlu beralih ke arsitektur sirip tunggal untuk desain sel standar. Satu sirip harus bekerja dengan cukup baik. Untuk memperluas teknologi finFET ke N3, kita membutuhkan teknologi khusus untuk meningkatkan kekuatan sirip tunggal dan mengurangi fenomena latar belakang palsu. ”

Selain mobilitas tinggi dari finFET, opsi selanjutnya adalah GAA. Pada 2017, Samsung memperkenalkan Multi Bridge Channel FET (MBCFET) selama 3 nm. MBCFET - Nanolayer FET. MBCFET uji coba Samsung akan tersedia pada tahun 2020.

Chip Nanolayer memiliki keunggulan dibandingkan finFET. Dalam finFET, rana membungkuk di sekitar sirip dari tiga sisi. Dalam nanolayer, rana terletak di empat sisi sirip, yang memberikan kontrol lebih besar terhadap arus.

Dibandingkan dengan 5 nm, FET nanolayer Samsung memberikan peningkatan efisiensi area logis hingga 45% dan pengurangan konsumsi daya 50% atau peningkatan kecepatan 35%. "Struktur finFET memiliki batasan sendiri pada skalabilitas, karena tegangan suplai tidak dapat diturunkan di bawah 0,75 V. Inovasi kami dengan penggunaan nanolayer mengurangi tegangan ke nilai kurang dari 0,7 V," kata Samsung Samsung.

Ada beberapa jenis teknologi GAA, termasuk nanolayer FET dan nanowire FET. GAA sendiri adalah langkah selanjutnya setelah finFET. Dalam sistem ini, finFET terletak di sisinya, dan kemudian dibagi menjadi potongan-potongan horisontal. Potongan membentuk saluran. Bahan rana membungkus setiap lapisan.

Dibandingkan dengan nanowire FET, sirkuit seperti ini memiliki saluran yang lebih luas, yaitu produktivitas dan arus eksitasi yang lebih tinggi. "Nanolayers memiliki lebar yang lebih efektif," kata Imec Horiguchi. "Nanowires jauh lebih baik dengan elektrostatik." Tetapi penampang mereka sangat kecil. Ini tidak akan memberikan keuntungan dalam hal lebar saluran yang efektif. "

Arsitektur GAA memiliki beberapa masalah. Biasanya mereka memberikan peningkatan yang sangat kecil dibandingkan dengan finFET pada 5 nm. Membuat keripik menggunakan teknologi ini cukup sulit.

"GAA generasi berikutnya pada 3 nm dan di bawah menambah tingkat kerumitan lain untuk manufaktur," kata Richard Gotshaw, wakil presiden dan direktur teknis, Lam Research . - Sekilas, sepertinya modifikasi untuk finFET. Namun, persyaratan meningkat dan kompleksitas arsitektur GAA ini secara signifikan lebih tinggi daripada finFET. "Dalam proses produksi chip nanolayer, langkah pertama adalah penempatan lapisan bolak tipis SiGe dan silikon pada substrat. “Kami mendapatkan setumpuk silikon, silikon-germanium, silikon. Kami menyebutnya superlattice, ”kata Namsun Kim, chief engineering officer di Applied Materials, dalam sebuah wawancara baru-baru ini. "Memiliki konten germanium, Anda perlu menyediakan lapisan isolasi yang baik."Minimal, paket harus terdiri dari tiga lapisan SiGe dan tiga silikon. Kemudian struktur lembaran kecil diterapkan pada paket. Setelah itu, isolasi dengan alur terbentuk, dan kemudian pembagi internal.Kemudian, lapisan SiGe dikeluarkan dari superlattice, meninggalkan lapisan silikon dengan ruang kosong di antara mereka. Setiap lapisan silikon membentuk dasar lembaran atau saluran dalam perangkat. Maka Anda perlu menerapkan bahan dengan konstanta dielektrik tinggi untuk membuat rana. “Ada jarak minimum antara kawat nano. Sangat kecil Masalahnya adalah menempatkan logam dengan ketebalan di sana, ”kata Kim.Industri ini telah bekerja selama bertahun-tahun untuk menciptakan teknologi GAA, tetapi masih ada beberapa masalah. "Salah satu yang utama adalah kapasitansi parasit," kata Kim. - Jika Anda bertanya kepada saya apa masalah utama teknologi GAA, maka ada dua di antaranya. Pembagi internal dan isolasi substrat. "Apa selanjutnya

Berapa lama teknologi GAA atau nanolayer cukup? “Nanolayers akan bertahan dua atau tiga dari teknologi proses selanjutnya. Lokakarya dapat membuat nanolayer di N3. Generasi berikutnya pasti. Dan setelah itu, Anda mungkin harus mengubah integrasi nanolayers atau arsitektur. Tapi itu akan tetap menjadi arsitektur nanolayer, ”kata Horiguchi dari Imec.Industri sedang menjajaki cara untuk meningkatkan teknologi GAA dan finFET dalam proses manufaktur maju. Perangkat GAA saat ini menawarkan sedikit keuntungan dibandingkan finFET. Misalnya, nada rana chip nano-lapisan Imec sebelumnya adalah 42 nm, dan nada minimum konduktor logam adalah 21 nm. Sebagai perbandingan, finFET pada 5 nm dapat memiliki pitch gate 48 nm dan pitch minimum konduktor logam 28 nm.Di laboratorium, Imec menunjukkan skalabilitas perangkat semikonduktor tipe-p dengan tumpukan ganda GAA dan germanium di saluran. Menggunakan sirkuit bebas ekstensi, Imec telah mengembangkan kawat nano dengan panjang gerbang sekitar 25 nm. Itu dapat diadaptasi untuk nanolayer. Seperti versi sebelumnya, ukuran kawat adalah 9 nm.Germanium dapat berperan dalam terus menggunakan finFET di luar teknologi proses 5 nm. Imec menunjukkan Ge nFinFET dengan rekor Gmsat / SSsat dan PBTI yang tinggi. Mereka dicapai dengan meningkatkan penggantian bahan dielektrik tinggi.Kami juga akan melihat apakah teknologi finFET dapat diperluas hingga 3 nm. Juga tidak jelas apakah chip nanolayer akan muncul tepat waktu. Ada banyak hal yang tidak diketahui dan ketidakpastian dalam lanskap yang berubah ini, dan tidak ada jadwal untuk mengklarifikasi situasi.