Akhirnya, sebuah

buku teks tentang SystemVerilog dirilis di Rusia

pada tingkat yang lebih tinggi daripada pemula . Buku teks ini menjelaskan teknologi dan teknik yang diminta untuk wawancara di NVidia, Intel, AMD, Apple dan perusahaan elektronik lainnya: penggunaan pernyataan bersamaan dan cakupan fungsional, yang sekarang tidak hanya membutuhkan insinyur verifikasi, tetapi juga desainer chip; algoritma simulator dengan siklus delta; penjelasan waras tentang analisis waktu statis; diagram komunikasi unit perangkat keras melalui antrian perangkat keras; implementasi komunikasi ini menggunakan mesin negara terbatas dengan jalur data, dll.

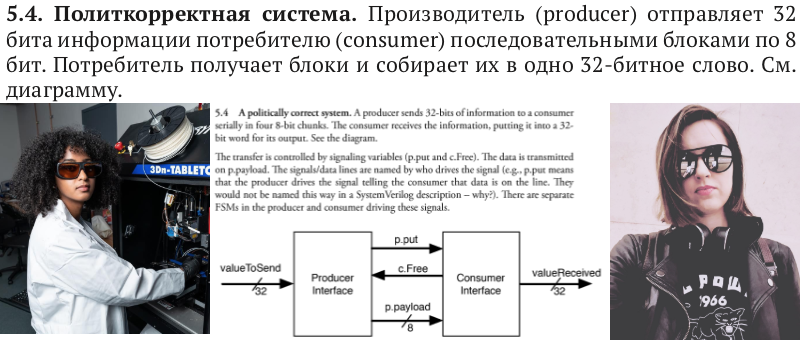

Dalam bab tentang yang terakhir, pembaca Rusia mungkin bingung dengan menyebutkan "sistem yang benar secara politis". Apa artinya itu? Ini mungkin merupakan singgungan terhadap

insiden yang terjadi di Los Angeles County pada tahun 2003. Pejabat Los Angeles meminta produsen, pemasok, dan kontraktor untuk berhenti menggunakan istilah "master / slave" untuk peralatan komputer, karena salah satu karyawan county diingatkan tentang masa lalu budak.

Sekarang penulis literatur teknis menghindari istilah master / slave. Insinyur Afrika-Amerika juga bekerja di Amerika modern (misalnya, Sofia Mvokani dari Kamerun - pada foto di sebelah kiri), dan penggunaan istilah lama terlihat kuno, seperti istilah "pan / slave" dalam literatur teknis Ukraina akan terlihat sebagai ganti "lead / lead" yang diterima ( "Pemimpin / budak" Rusia).

Ini bukan pertama kalinya bahwa tema perjuangan orang Afrika-Amerika untuk hak-hak sipil muncul dalam pendidikan elektronik Rusia. Sebagai contoh, Tatyana Volkova, seorang spesialis terkenal dalam pendidikan elektronik, mengenakan T-shirt dengan lambang "Black Panthers", gerakan California, yang pada suatu waktu menganggap protes damai tidak mencukupi, dan terlibat dalam protes bersenjata.

Gambar penuh lambang di bawah kulit Tatyana Alexandrovna ada di bawah luka, tetapi terutama saya akan berbicara tentang siklus delta dan mesin negara:

Di bawah ini adalah screenshot dari artikel tentang master / slave dan lambang Black Panther yang dijanjikan, setelah itu kita beralih ke buku seperti itu.

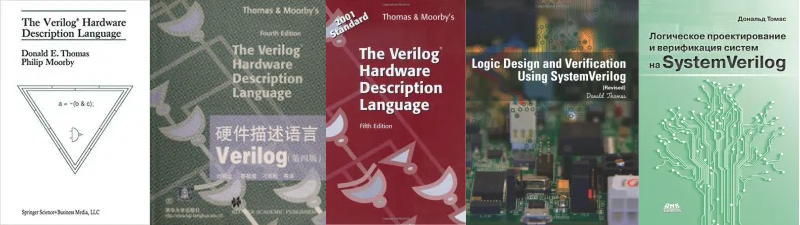

Pertama-tama, Donald Thomas, penulis buku

"Desain Logika dan Verifikasi Sistem pada SystemVerilog" (2019 dalam bahasa Rusia dari DMK-Press, 2016 dalam bahasa Inggris) adalah Donald Thomas yang sama, yang turut menulis bersama Philip Murbi menulis sebuah buku 1991 Perangkat Keras Verilog Deskripsi Bahasa oleh Donald Thomas dan Philip Moorby. Kemudian, pada tahun 1991, banyak perusahaan elektronik masih merancang microchip dengan cara lama, menggambar mereka dengan mouse di layar; teknologi sintesis logis baru saja meninggalkan laboratorium untuk produksi; bahasa deskripsi perangkat keras dianggap dimaksudkan untuk menulis model dan pengujian, dan bukan kode sumber untuk membuat sirkuit akhir; selain VHDL dan Verilog ditutup pada waktu itu, ada banyak bahasa kecil dan eksklusif seperti Abel, CUPL, PALASM; dan Intel dan MIPS memiliki bahasa deskripsi perangkat keras internal.

Dalam lingkungan seperti itu, buku Thomas dan Murbi keluar, yang menjadi sama untuk para desainer sirkuit digital tahun 1990-an seperti buku untuk Kernigan-Richie untuk programmer untuk C, dan buku-buku Bjarni Straustrup untuk programmer C ++. Buku ini telah bertahan lima edisi - dari tahun 1991 hingga 2002, tetapi untuk era iPhone jelas tidak cukup. Dan pada tahun 2016, Donald Thomas memutuskan untuk mengejar ketinggalan dan merilis sebuah buku baru di mana ia menggambarkan inovasi kunci dalam bahasa dan metodologi selama 25 tahun. Sangat 25 tahun di mana Verilog telah menjadi pangkalan bersama untuk seluruh industri, skema ditulis untuk semuanya mulai dari iPhone terkenal dan mengendalikan komputer di Tesla hingga helikopter militer Rusia.

Selanjutnya, saya akan menyoroti komentar saya dengan teks biru untuk memisahkannya dari gambar-gambar dari buku.

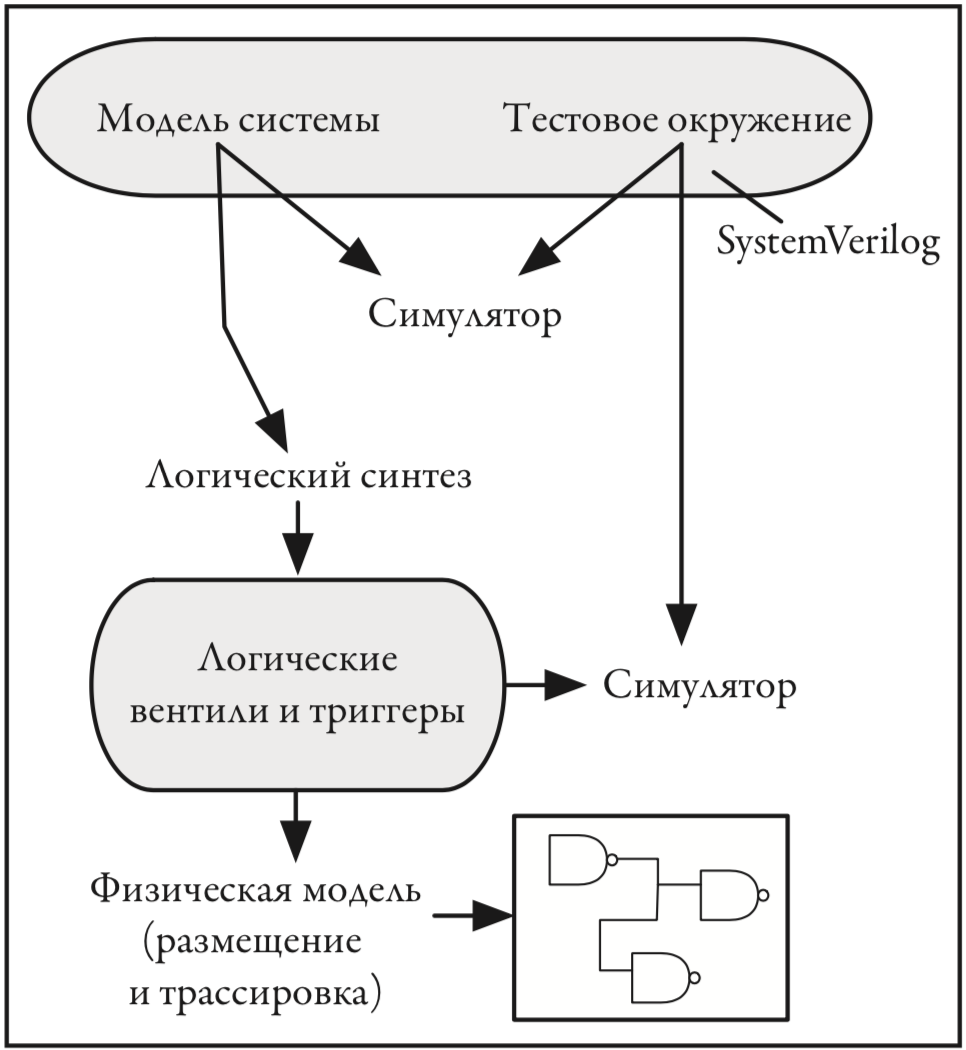

Bahkan sebelum teks utama buku ini, ada bab pra-"Konteks: Desain di Tingkat Transfer Register", sehingga seorang programmer, anak sekolah, atau, katakanlah, seorang pecinta olahraga dengan papan prototyping, mengambil buku ini dari rak dan segera memahami apa yang dikatakan dan bagaimana mereka dapat menggunakan buku. Dikatakan:Sistem digital sedang diproduksi dengan miliaran transistor pada sebuah chip. Seorang amatir, tentu saja, dapat menggambar beberapa gerbang logika dan menghubungkannya dengan kabel sebagai spesifikasi (untuk implementasi pada papan tempat memotong roti), tetapi untuk proyek komersial ini adalah cerita kuno ... Sistem modern ditentukan dalam bahasa deskripsi perangkat keras seperti SystemVerilog.

Pada saat yang sama, inilah gambaran yang disederhanakan untuk menggambarkan bagaimana teks pada veril berubah menjadi trek dan transistor dari rangkaian mikro di pabrik:

Kata pertama dalam buku setelah kata pengantar adalah "simulator". Untuk memahami bahasa deskripsi perangkat keras, Anda harus menyadari bahwa subset verilog yang disintesis bukan bahasa pemrograman, tetapi bahasa untuk menggambarkan rangkaian listrik. Seperti katakanlah HTML bukan bahasa pemrograman, tetapi bahasa untuk menggambarkan halaman web. Sementara bahasa pemrograman dimaksudkan untuk dikompilasi menjadi rantai instruksi prosesor, bahasa deskripsi perangkat keras dimaksudkan untuk dikonversi (khususnya) menjadi besi prosesor seperti itu. Dalam hal ini, sebelum melakukan pengecoran ke dalam besi, kode dalam bahasa deskripsi perangkat keras perlu diperiksa, untuk keperluan apa juru bahasa khusus, yang disebut simulator, berfungsi.

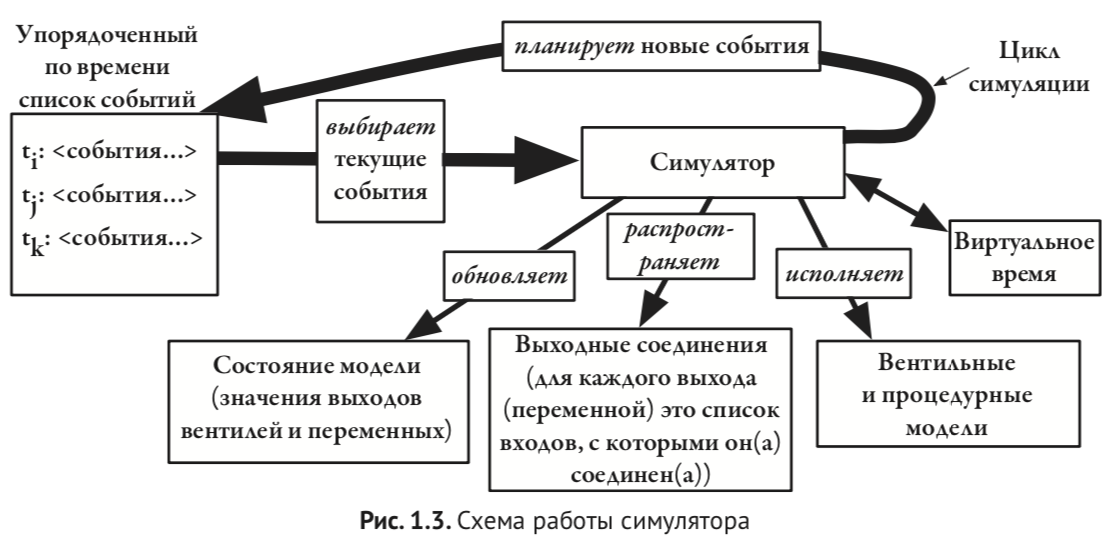

Di awal buku, Donald Thomas menunjukkan gambar sederhana dari simulator, dan di akhir buku ia menjelaskan dan menambahkannya:

Simulator memiliki antrian acara dan waktu simulasi:

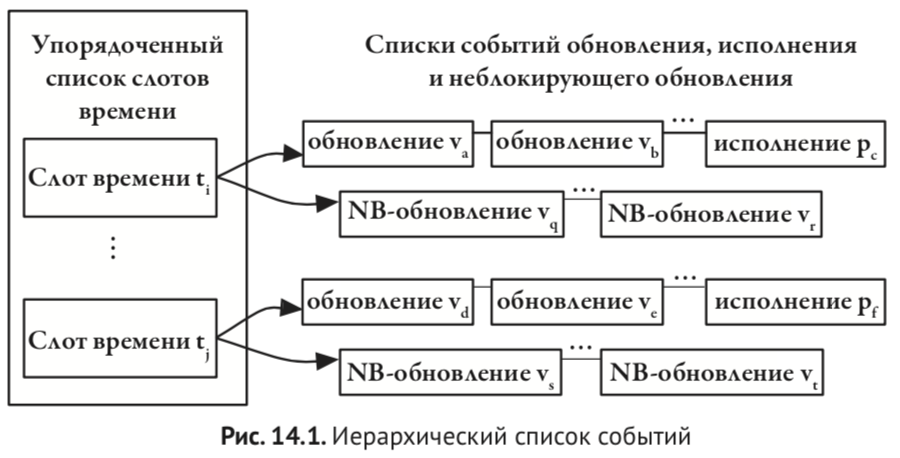

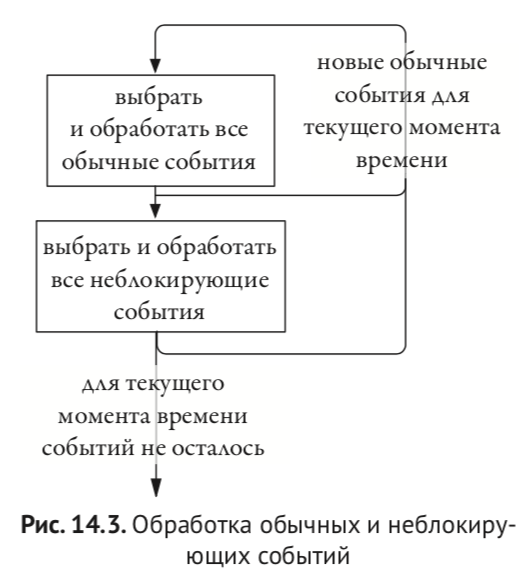

Suatu peristiwa dapat memunculkan peristiwa baru, baik pada saat simulasi saat ini (dalam siklus delta saat ini) dan di masa mendatang. Dalam siklus delta saat ini, semua peristiwa yang dihasilkan oleh apa yang disebut tugas pemblokiran diproses terlebih dahulu, dan kemudian peristiwa yang dihasilkan oleh tugas non-pemblokiran diproses. Ini diperlukan untuk simulasi semantik paralel yang benar dari perambatan sinyal listrik pada besi:

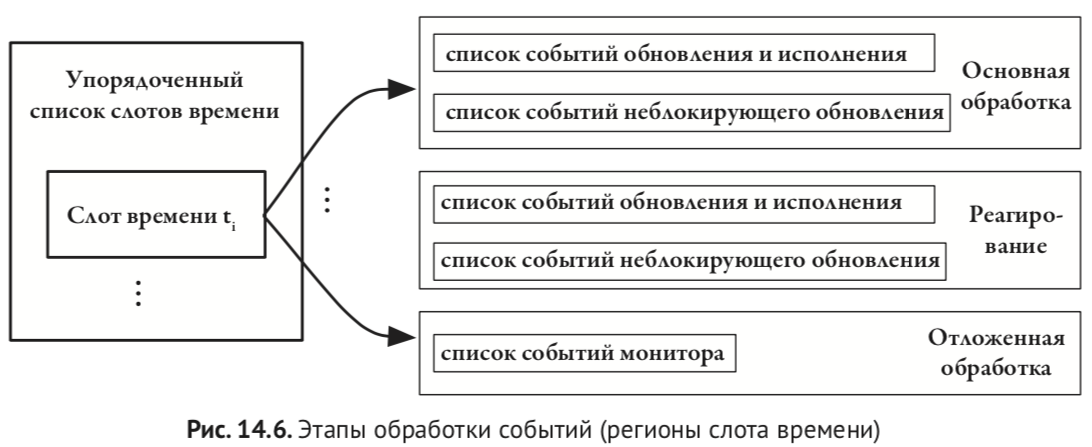

Selain subset disintesis dari Verilog, ada juga subset yang tidak disintesis. Ini dimaksudkan untuk menggambarkan lingkungan pengujian dan pengujian, dan sekarang dapat dianggap sebagai semacam bahasa pemrograman. Untuk acara dan monitor lingkungan pengujian, langkah-langkah simulator tambahan diperkenalkan:

Pengetahuan yang akurat tentang algoritma simulator sangat berguna untuk menghindari berbagai bug yang terkait dengan apa yang disebut ras (kondisi lomba). Ketika saya campur tangan insinyur, saya selalu meminta mereka untuk memberikan contoh kondisi balapan di Verilog. Terlebih lagi, jika bagi para Desain RTL dan Insinyur Verifikasi Desain muda, pengetahuan seperti itu sangat diinginkan, tetapi tidak dalam semua aspek yang diperlukan 100%, yaitu profesi di mana uang dibayarkan langsung untuk pengetahuan ini. Saya berbicara tentang programmer yang bekerja di tim Synopsys VCS, Cadence IES, dan Mentor ModelSim.

Synopsys dan Cadence adalah dua perusahaan yang berlokasi di California dalam 15 menit berkendara satu sama lain. Mereka hanya mempekerjakan beberapa ribu orang, tetapi mereka mengendalikan pengembangan sirkuit mikro di seluruh dunia - di Intel, Apple, Samsung, Huawei, bahkan di lembaga rahasia Rusia yang membuat chip untuk peralatan militer.

Jika kawan-kawan Putin, Rogozin dan Vekselberg benar-benar ingin memperkenalkan substitusi impor di Rusia, maka mereka dapat membiayai pengembangan analog Rusia Synopsys VCS (untuk mensimulasikan verilog), Synopsys Design Compiler (untuk sintesis logis dari verilog) dan Synopsys IC Compiler (untuk penempatan fisik hasil sintesis logis) ) Mungkin ada beberapa ribu programmer yang mengerti secara matematis di Rusia.

Meskipun lisensi untuk produk-produk perangkat lunak ini cukup mudah untuk dihancurkan, menggunakannya tanpa dukungan itu sulit. Jika Huawei terputus dari Synopsys dan Cadence, mereka dalam beberapa hal akan lebih buruk daripada ketika terputus dari Android dan bahkan core ARM.

Ya, jadi di sini adalah algoritma yang disempurnakan di akhir buku Donald Thomas. Jika Anda tidak mempelajarinya dengan hati, tidak ada gunanya campur tangan dalam kelompok simulasi di Synopsys, Cadence, Siemens / Mentor, Xilinx, dan mereka akan meminta Anda untuk menggambarnya di papan tulis dan menyarankan cara mengoptimalkan kasus tertentu:

Setelah mengklarifikasi simulasi di awal buku, Donald Thomas menggambarkan bahasa SystemVerilog. Bahasa ini muncul sebagai superset Verilog pada tahun 2002, sebagai hasil dari penggabungan bahasa Verilog-2001, Vera dan Superlog, dan dengan tambahan gagasan dari Bahasa Spesifikasi Properti (PSL), yang diubah menjadi SystemVerilog Assertions (SVA).

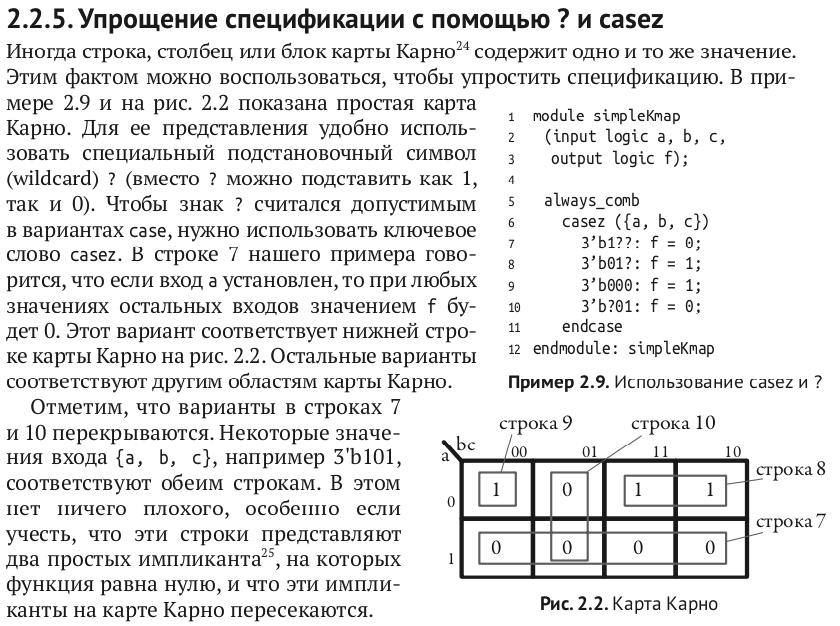

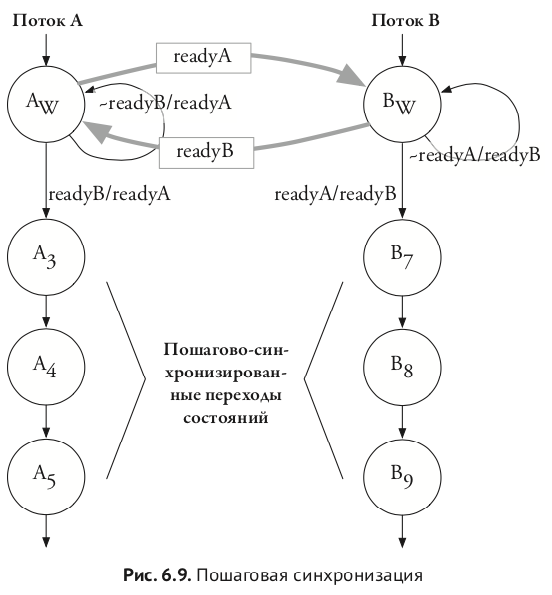

Donald Thomas percaya bahwa Anda telah mempelajari dasar-dasar desain digital di suatu tempat, dan karena itu menjalin ke dalam narasi berbagai karya terkenal seperti kartu Carnot. Peta Carnot digunakan untuk desain sirkuit manual pada 1960-an, setelah itu metode ini digantikan oleh optimasi otomatis logika menggunakan algoritma Quine-McClusky dan Espresso pengoptimal logika otomatis. Oleh karena itu, kartu Carnot hadir di semua buku teks universitas tentang desain logika digital, tetapi mereka tampaknya menggantung di udara. Dan di sini Donald Thomas menempelkan peta Carnot ke kehidupan seorang desainer pada verilo abad ke-21:

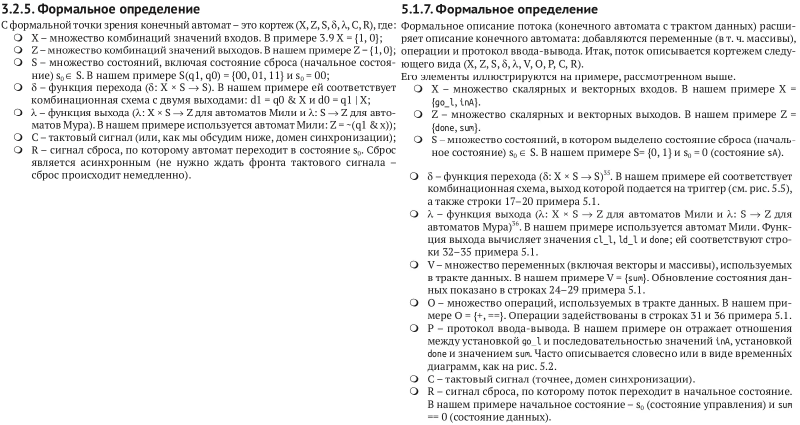

Selanjutnya, Donald Thomas menulis tentang mesin negara yang terbatas, dan dia memberikan 1) definisi matematika yang ketat; 2) diagram; 3) kode; 4) setelah itu mulai memperluas mereka ke mesin negara yang terbatas dengan jalur data - arus perangkat keras; 5) setelah itu aliran ini mulai berinteraksi dengannya, baik menurut protokol "benar secara politis" sederhana (lihat di atas), dan menggunakan antrian perangkat keras.

Berikut adalah kode untuk otomat sederhana dengan jalur data yang dikutip Thomas sebagai contoh pertama:

Selanjutnya, Thomas memiliki bab tentang analisis waktu statis. Tidak ada yang istimewa, tetapi lebih bersih daripada di banyak situs India populer, "Bagaimana cara melewati wawancara VLSI." Dan juga lebih lengkap daripada di beberapa buku tentang Veril, yang dengan susah payah mengunyah sintaks bahasa, tetapi tidak benar-benar menunjukkan cara menggunakannya.

Mengapa kita memerlukan analisis pewaktuan statis? Dalam perangkat keras nyata, berbeda dengan ilusi yang ditunjukkan prosesor kepada programmer, setiap perhitungan melewati interval waktu ketika semua sampah ada di kabel - tidak hanya dengan jelas menghitung nol dan yang, tetapi juga gangguan acak apa pun, yaitu, kesalahan, dan umumnya nilai non-digital di zona terlarang. Misalnya, jika Anda memiliki semua tegangan di atas 0,7 volt dianggap sebagai unit digital, dan semua tegangan di bawah 0,3 volt sebagai nol digital, maka 0,4 volt dapat muncul pada kabel.

Pada akhirnya, semua sinyal dalam rangkaian berjalan dengan caranya sendiri dan situasi menjadi tenang, tetapi "pada akhirnya" ini harus kurang dari siklus sinyal clock (jam). Siklus ini berbanding terbalik dengan frekuensi di mana sirkuit beroperasi (gigahertz, megahertz).

Jika hasil perhitungan atau operasi logis tidak jatuh ke pemicu D (elemen memori minimum) pada saat aperture (interval sekitar perubahan sinyal seperti itu), keadaan sirkuit akan menjadi sampah - satelit atau reaktor akan meledak, iPhone akan berhenti menjawab panggilan. Seluruh perancang peralatan perlu tahu tidak kurang dari logika.

Mengapa analisisnya statis? Pada 1980-an, itu dinamis - penundaan diklarifikasi melalui simulasi. Ini ternyata tidak dapat diandalkan untuk rangkaian dengan ratusan ribu, jutaan dan milyaran transistor, dan sekarang semua penundaan dihitung secara statis, berdasarkan analisis jalur sinyal setelah sintesis.

Sinyal clock juga dapat datang ke berbagai bagian chip dengan beberapa penundaan, yang menambah ketidakpastian lain pada dapur ini yang perlu dihilangkan (untungnya, tidak secara manual, tetapi dengan bantuan program pohon sintesis jam dan metode lain):

Dalam bab tentang arus, Thomas membahas beberapa opsi dasar tentang bagaimana mesin status operasi paralel dengan jalur data dapat bertukar informasi, termasuk menggunakan buffer dan antrian. Seperti dalam desain / sirkuit itu sendiri, pada tingkat transfer register, demikian juga dalam model perilaku atau lingkungan pengujian sirkuit. Saat membaca Thomas, senang menulis dan men-debug contoh sendiri untuk semua kasus protokol yang dijelaskan olehnya. Faktanya adalah bahwa mereka suka menulis kode pada topik-topik seperti itu (mesin keadaan terbatas pengontrol kecil, aliran data antara dua modul, jalur data yang disalurkan melalui pipa atau hanya kode untuk antrian perangkat keras) di papan tulis atau di komputer selama wawancara tingkat kedua di perusahaan elektronik. Jika Anda dapat menulis contoh untuk salah satu kombinasi yang dijelaskan oleh Thomas dalam 20 menit dengan kode 30-50 baris, maka Anda akan membuat kesan yang baik. Sulit dipelajari - mudah dalam pertempuran.

Lingkungan pengujian untuk router (Gbr. 8.3) dengan antrian untuk beberapa port adalah contoh populer yang digunakan untuk menjelaskan metodologi verifikasi. Mungkin karena beberapa metodologi ini ditemukan oleh Cisco dan perusahaan lain yang merancang chip untuk perangkat keras jaringan.

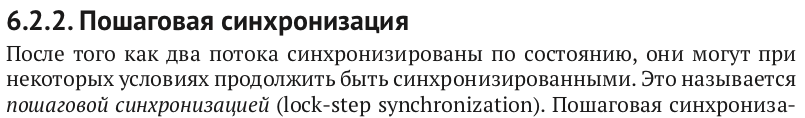

Dalam bab 6.2.2. Thomas menjelaskan salah satu opsi untuk interaksi utas - sinkronisasi langkah-demi-langkah (Kunci-langkah). Salah satu aplikasi kunci-langkah adalah sistem keandalan tinggi, misalnya dalam elektronik otomotif. Kasus khusus: dua prosesor dapat menjalankan program yang sama dengan penundaan beberapa siklus, dan selama pelaksanaan ini sirkuit khusus dapat memverifikasi bahwa mereka memiliki hasil yang sama.

Thomas jelas peduli dengan keandalan, karena selain langkah-kunci, ia mengutip penggunaan CRC, kode redundan siklikal untuk mendeteksi kesalahan dalam transfer data. Pada saat yang sama, Thomas memberi tahu cara menghitung CRC menggunakan LFSR, register shift umpan balik linier. Baik itu dan yang lain harus bisa menjadi insinyur muda. Ini adalah keuntungan dari buku Thomas - meskipun tidak selalu menggali dalam-dalam, buku ini menyentuh banyak topik dan menunjukkan tempat untuk menggali:

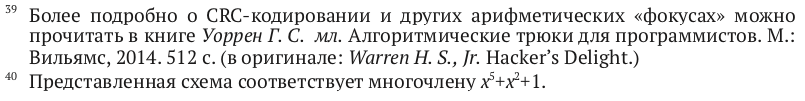

Dalam menggambarkan CRC, Thomas merujuk pada buku yang sangat menarik dan disalahpahami di Rusia oleh Hacker's Delight :

Donald Thomas dalam buku barunya menyentuh tiga teknologi yang sama sekali tidak ada dalam buku lama:

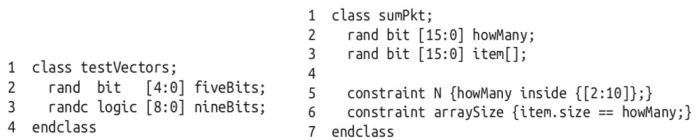

- Pembuatan transaksi pseudo-acak otomatis dengan aturan terbatas (transaksi acak terbatas / pemecah kendala).

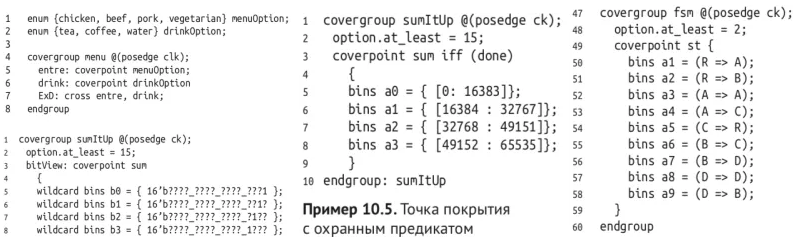

- Akuntansi untuk cakupan skenario menarik yang timbul selama pengeboman desain oleh transaksi acak terbatas, cakupan fungsional.

- Bahasa pernyataan logika temporal (pernyataan bersamaan) dan penggunaannya baik dalam simulasi maupun dalam bukti otomatis properti desain menggunakan program verifikasi formal.

Ketiga teknologi ini memasuki industri dengan baik hanya pada abad ke-21, tetapi mereka masuk dengan cukup kuat. Pada awalnya, mereka semua digunakan untuk membuat lingkungan pengujian oleh insinyur verifikasi, tetapi sekarang pengetahuan tentang cakupan fungsional dan Bahasa Asisten Temporal (SystemVerilog Assertions - SVA) juga membutuhkan desainer. Thomas memiliki batas minimum tertentu yang akan membantu Anda tidak terputus dalam wawancara telepon, tetapi untuk pekerjaan nyata Anda perlu tahu lebih banyak. Selain itu, tidak hanya bahasa pernyataan temporal seperti itu, tetapi juga praktik debugging dengan bantuannya mesin negara terbatas paralel yang dihasilkan oleh simulator untuk setiap pernyataan, serta penggunaan program verifikasi formal. Verifikasi formal berbasis pernyataan dalam beberapa tahun terakhir telah banyak diimplementasikan dalam Apple, AMD dan perusahaan sejenis lainnya.

Saya memiliki seorang teman yang mengunduh

buku ini tentang bahasa pernyataan temporal dan mempelajarinya sepanjang liburan Tahun Baru alih-alih perjalanan ke Hawaii bersama gadis-gadis. Dari sini Anda dapat memahami bagaimana SystemVerilog Assertions (SVA) penting untuk karier dan industri. Benar, demi kelengkapan, saya harus menyebutkan bahwa dia adalah putra emigran dari Taiwan, dan mereka memiliki sikap yang lebih buruk terhadap hal-hal seperti itu daripada orang Rusia.

Inilah cara Thomas berurusan dengan menghasilkan transaksi pseudo-acak (transaksi dengan bidang rand dan pembatasannya menggunakan konstruk kendala):

Dan di sini adalah bagaimana Thomas berhubungan dengan cakupan fungsional - covergroup / coverpoint / bins, dengan mempertimbangkan kombinasi beberapa penutup variabel (lintas), menggunakan wildcard bins, rentang nilai, serta cakupan transisi di mesin negara:

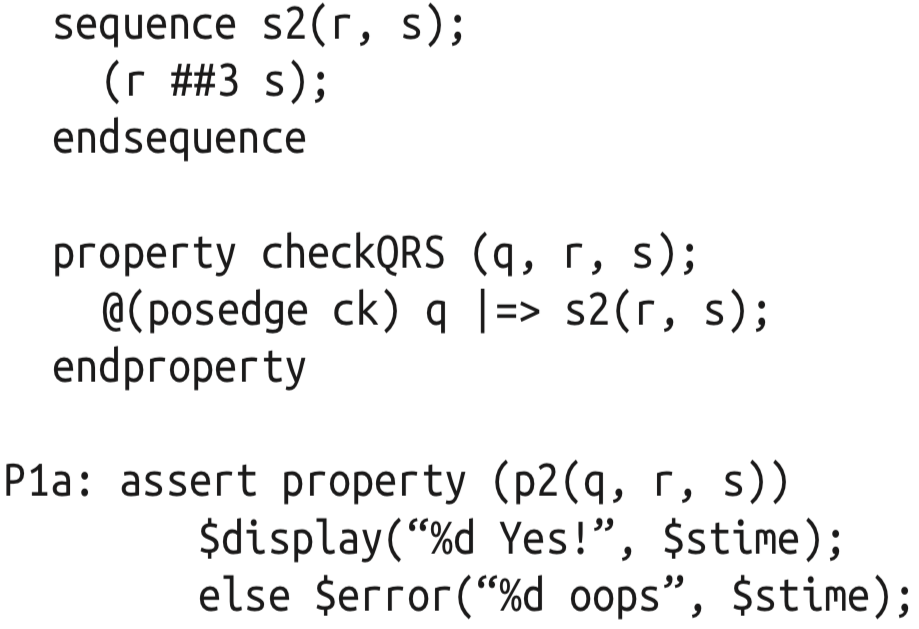

Berikut adalah contoh pernyataan temporal yang paling sederhana "jika q benar pada tepi positif sinyal clock, maka urutan s2 harus dieksekusi melalui siklus, di mana r adalah true pertama, dan s adalah dalam tiga siklus lagi":

Apa yang harus dibaca sebelum dan sesudah buku "Desain Logis dan Verifikasi Sistem pada SystemVerilog" oleh Donald Thomas?

Jika Anda sama sekali tidak mengerti apa pun dalam posting saya, maka Anda dapat mencoba membaca buku

"Sirkuit Digital dan Arsitektur Komputer" oleh David Harris dan Sarah Harris . Buku Harris & Harris dapat dipahami oleh semua orang yang dapat membaca dan menghitung, asalkan pembaca memiliki motivasi. Buku ini dimulai di tingkat sekolah menengah - voltase, angka biner - dan berakhir dengan desain prosesornya sendiri di veril.

Spoiler: David Harris dan Sarah Harris bukan suami-istri dan bahkan bukan saudara laki-laki dan perempuan. Mereka hanyalah senama yang secara tidak sengaja mulai bekerja sebagai guru di universitas yang sama, di mana mereka menulis buku.

Di sini di sebelah kiri dalam foto adalah gadis Irina dari Novosibirsk Academgorodok memegang Harris & Harris edisi bahasa Inggris, dan di sebelah kanan adalah edisi Rusia-nya.

Setelah buku karya Donald Thomas, saya sarankan mengunduh artikel oleh Cliff Cummings. Dia adalah pelatih veril paling terkenal untuk sintesis dan verifikasi. Saat membaca buku Donald Thomas, saya mendapat ide "sering kali akan menyenangkan untuk memasukkan potongan ini dan itu dari Cliff Cummings" untuk kelengkapan.

Cliff mengambil $ 1.000 - $ 3.000 untuk setiap siswa di seminar, tergantung pada durasi seminar (dari hari ke minggu), dan perusahaan elektronik membayar untuk meningkatkan kualitas insinyur mereka yang tidak terlatih dengan baik di universitas. Bahkan di Stanford, sayangnya, tidak semua orang mengetahui hal ini - saya memiliki seorang magang dari Stanford, saya tahu itu darinya. Jika Anda mengunduh semua artikel gratis dari Cliff Cummings setelah membaca Donald Thomas, maka Anda akan menghemat semua uang ini.Kedua artikel ini diperlukan - mereka ingin bertanya di mana-mana dalam wawancara:Teknik Desain & Verifikasi Jam Domain Crossing (CDC) Menggunakan Simulasi Sistem Verilogdan Teknik Sintesis untuk Desain FIFO Asynchronous dengan Asynchronous Pointer Comparisons, , FSM c FSM «case (1'b1) // synopsys parallel_case… state[STATE_N]: ...», , Sun Microsystems, :

Asynchronous & Synchronous Reset Design Techniques — Part DeuxCoding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free OutputsSynthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 EnhancementsDan di sini ada artikel yang ingin tahu di mana Anda akan melihat kurangnya pemikiran tentang Verilog, yang tetap ada sejak 1980-an. Meskipun sekarang, di era analisis pewaktuan statis, ini tidak begitu relevan, tetapi penundaan inersia dan transportasi kadang-kadang disebutkan dalam literatur dan kode, dan Anda harus tahu cara memodelkannya:Metode yang Benar Untuk Menambahkan Penundaan ke Verilog Model PerilakuIni adalah saya dengan Cliff Cummings: