Jika Anda berpikir bahwa "geng" Intel adalah pendukung

hukum Moore yang paling loyal, maka Anda mungkin belum pernah mendengar bagaimana Philip Wong menyebarkan masalah ini. Wong, wakil presiden penelitian perusahaan di Taiwan Semiconductor Manufacturing Corp (TSMC), membuat presentasi di konferensi Hot Chips baru-baru ini yang menyatakan bahwa hukum Moore tidak hanya hidup dan sehat, tetapi dengan serangkaian trik teknologi yang cukup beragam, itu masih tidak benar kurang dari tiga dekade.

"Dia belum mati," katanya kepada yang hadir di Hot Chips. "Dia tidak melambat, dia bahkan tidak batuk."

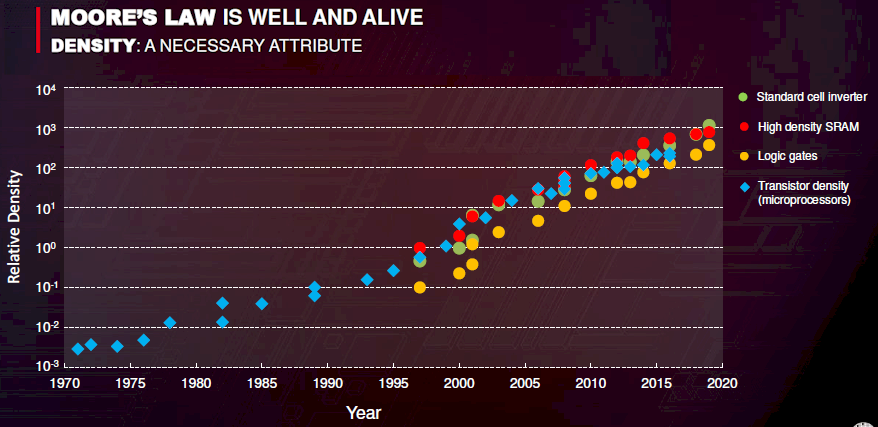

Dengarkan Wong, jadi satu-satunya tindakan yang diperlukan untuk mempertahankan hukum Moore adalah meningkatkan kepadatan. Dan meskipun ia mengakui bahwa frekuensi clock telah mencapai puncaknya, menandai berakhirnya

hukum skala Dennard , ia mengatakan bahwa itu adalah kepadatan transistor yang akan meningkatkan kecepatan dan efisiensi energi.

Hukum Moore adalah Hidup

Hukum Moore adalah HidupPada akhirnya, tidak masalah seberapa besar kepadatan yang dicapai. Wong percaya bahwa hal utama adalah perusahaan dapat memasukkan lebih banyak transistor ke dalam volume yang lebih kecil dengan efisiensi energi yang lebih baik. Dalam jangka pendek, ini dapat dicapai dengan cara lama yang sudah terbukti, yaitu dengan meningkatkan teknologi pembuatan CMOS sehingga menghasilkan transistor dengan panjang gerbang yang lebih pendek.

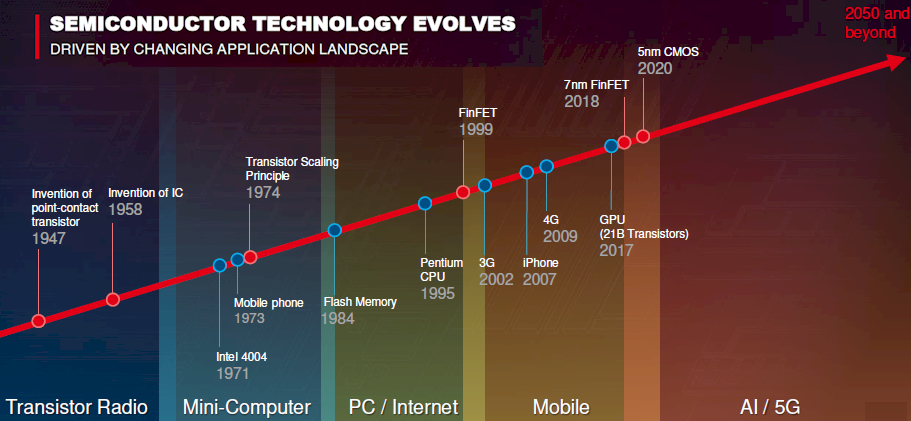

TSMC telah menguasai teknologi proses 7 nm dan bergerak menuju 5 nm. Wong mengatakan bahwa ekosistem pengembangan teknologi proses 5 nm sudah siap, dan perusahaan telah memulai produksi sampel berisiko - yaitu, teknologi proses dan alat pengembangan siap, dan substrat kerja sedang diproduksi. Pada pertemuan pemegang saham terakhir, TSMC mengumumkan bahwa mereka berencana untuk memulai produksi massal chip pada 5 nm pada paruh pertama tahun 2020. Ternyata rencana perusahaan sudah mencakup teknologi proses 3 nm.

Tetapi semua teknologi ini didasarkan pada chip

planar , dan Wong mengakui bahwa pendekatan ini pada akhirnya akan berhenti berskala. "Jika kita mengikuti jalur peningkatan dua dimensi, maka kita telah mencapai beberapa ratus atom, dan segera semua atom kita akan habis," jelasnya.

Namun ini bukan berarti akhir dari peningkatan kepadatan. Dia mencatat bahwa beberapa inovasi dalam industri semikonduktor mendukung grafik kepadatan ke atas bahkan pada akhir penskalaan Dennard. Secara khusus, teknologi silikon tegang dan

dielektrik k tinggi muncul , dan kemudian FInFet (Fin Field Effector Transistor), teknologi struktur tiga dimensi, mengikuti. Sekarang, untuk melampaui 7 nm, teknologi DTCO (Design Technology Co-Optimization) sedang diselidiki.

Semua inovasi ini terjadi karena itu perlu untuk mengembangkan platform komputasi baru yang membutuhkan perangkat keras yang lebih cepat dan lebih hemat energi. Evolusi ini melahirkan komputer mini pada 1970-an, PC pada 1980-an, Internet pada 1990-an, dan sekarang, perangkat seluler. Setiap tahap membutuhkan peningkatan kepadatan melalui perbaikan manufaktur semikonduktor. Wong percaya bahwa permintaan berikut akan datang dari kecerdasan buatan dan 5G.

Evolusi Teknologi Semikonduktor

Evolusi Teknologi SemikonduktorInovasi apa yang akan diperlukan untuk memastikan Partai Hukum Moore tidak berhenti?

Dalam jangka pendek, kepadatan komputasi keseluruhan dan kepadatan memori akan meningkatkan penggunaan chipset yang digunakan untuk membuat kasus multi-chip struktur 2.5D, bahkan jika chip itu sendiri tidak menjadi lebih padat. Wong mengatakan bahwa proses ini sudah membuat teknologi proses spesifik dari chiplet individual sebagai parameter yang kurang penting daripada kemampuan untuk mengintegrasikan komponen-komponen ini dalam satu paket.

TSMC memiliki versi sendiri dari sasis 2.5D dengan teknologi Chip-on-Wafer-on-Substrate (CoWoS) (Embedded Multi-die Interconnect Bridge, atau EMIB, dari Intel yang bersaing dengan teknologi ini). CoWoS memungkinkan Anda membuat penutup multi-chip, memperbaiki chipset, dan memori yang sesuai pada interposer, dan menghubungkannya menggunakan kontak vertikal TSV. Implementasi CoWoS yang paling menarik dianggap sebagai Akselerator GPU Nvidia Tesla V100, di mana GPU GV100 dikemas dengan memori bandwidth tinggi (HBM). Lebih banyak chipset yang terintegrasi oleh Intel, AMD dan Xilinx.

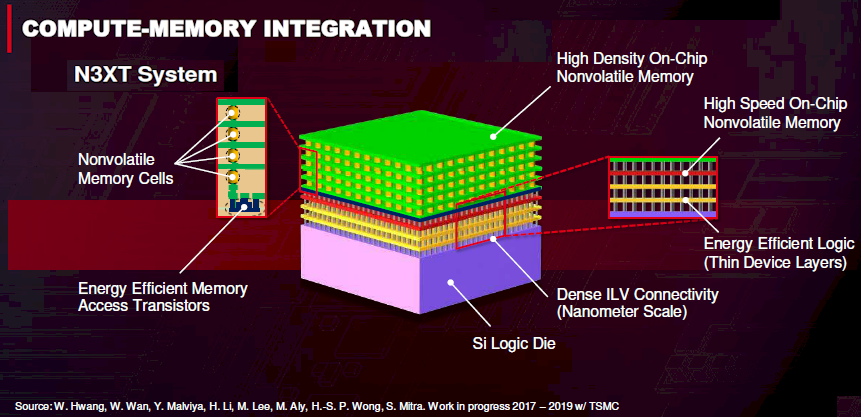

Tetapi kemungkinan 2.5D untuk meningkatkan kepadatan tidak terbatas. Solusi yang lebih terukur akan membutuhkan teknologi penempatan transistor tiga dimensi. Untuk ini, menurut Wong, teknologi N3XT tiga dimensi monolitik paling sesuai berdasarkan bahan baru dan integrasi memori yang ketat dengan logika. N3XT, "teknologi rekayasa nano sistem komputasi", telah dibahas di dunia akademis sejak 2015, tetapi sekarang perusahaan seperti TSMC telah mulai menganggapnya serius, N3XT memiliki peluang yang baik untuk komersialisasi.

Wong menunjukkan slide dengan diagram bagaimana perangkat seperti itu terlihat. Ini terdiri dari lapisan logika hemat energi (kuning), memori kecepatan tinggi (merah) dan memori non-volatile kapasitas tinggi (hijau), disusun bergantian satu di atas yang lain. Dan semua ini berada pada kristal silikon logika biasa (ungu).

Sistem N3XT

Sistem N3XTHal utama di sini adalah untuk menggabungkan berbagai lapisan melalui ILV, Inter-Layer-Via (akses vertikal antar pemain). Tidak seperti skala mikrometer TSV, ILV dapat dibentuk pada skala nanometer. Walaupun ini adalah bagian yang sangat penting dari teknologi N3XT, Wong tidak bisa mengatakan banyak tentang itu. Jelas, bagaimanapun, bahwa TSMC sedang bekerja erat di dalamnya dan telah mendaftarkan beberapa paten yang terkait dengannya.

Dalam chip tiga dimensi, interleaving memori dan logika sangat penting, karena memungkinkan Anda untuk mengurangi jarak di antara mereka, sehingga memastikan throughput tinggi dan latensi rendah transfer informasi, yang akan diperlukan untuk aplikasi seperti AI dan 5G. Dalam CMOS, memori dan logika tidak dapat disisipkan, karena etsa transistor logika memerlukan suhu urutan 1000 derajat Celcius, yang akan menghancurkan lapisan tetangga dalam produksi. Ini membutuhkan sesuatu yang dapat diproduksi pada suhu urutan 400 derajat.

Ternyata dalam beberapa tahun terakhir, para peneliti telah mempelajari bahan-bahan baru yang tampaknya cocok untuk produksi transistor berkecepatan tinggi pada suhu yang relatif rendah. Tidak seperti bahan silikon yang digunakan dalam produksi saat ini, monolayer logam transisi dichalcogenide (TMD) digunakan di sana berdasarkan unsur-unsur seperti molibdenum, tungsten dan selenium.

Materi TMD menunjukkan mobilitas pembawa muatan yang tinggi - elektron melintasinya dengan sangat mudah - dengan saluran yang sempit. Apa yang nyaman, hanya karakteristik seperti itu diperlukan untuk membuat transistor dengan ukuran kurang dari 2-3 nm. Wong mengatakan laboratorium TSMC sedang menguji substrat TMD eksperimental berdasarkan tungsten disulfida.

Kandidat lain untuk nanomaterial adalah karbon nanotube. Wong mengatakan variasi eksperimental mereka dibuat, menunjukkan perilaku material yang baik sebagai semikonduktor. Prototipe kerja logika dan SRAM berbasis karbon nanotube telah dirakit, termasuk varian RISC-V dari para peneliti di MIT.

Sedangkan untuk memori, menurut Wong, kandidat yang paling mungkin untuk integrasi tiga dimensi adalah: SST-MRAM (memori transfer torsi-magnetik torsi-transfer-transfer, memori akses magnetoresistif acak yang menggunakan transfer momentum putaran elektron untuk merekam); PCM

mengubah fase memori ;

akses acak memori resistif ReRAM; memori berdasarkan metalisasi sel CBRAM yang dapat diprogram; Memori

akses acak ferroelektrik FERAM. Semua ini adalah memori non-volatile dengan akses acak, yang tidak memerlukan operasi menghapus sel sebelum menulis informasi baru padanya. Beberapa opsi sudah ada di pasaran - Everspin MRAM, Samsung MRAM, Crossbar ReRAM dan Intel 3D XPoint (yang, menurut sebagian besar, adalah varian dari PCM).

Jenis memori baru

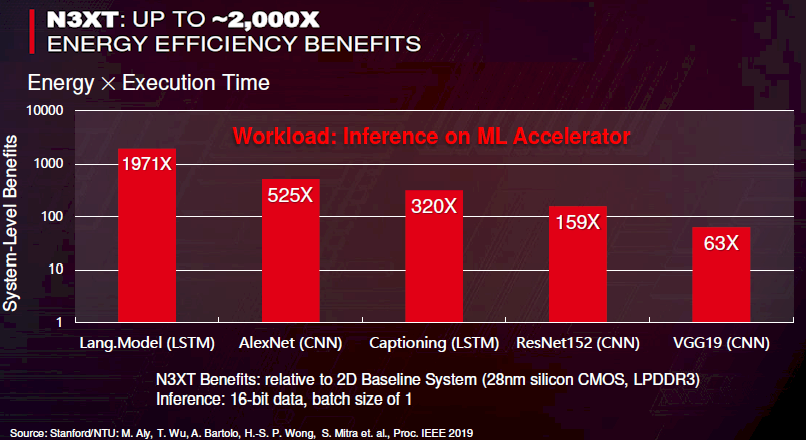

Jenis memori baruPara peneliti mensimulasikan kinerja perangkat N3XT dan membandingkannya dengan chip dua dimensi tradisional dengan logika dan kapasitas memori yang hampir sama. Menurut penelitian mereka, di mana berbagai metode pengukuran kecepatan algoritma pembelajaran mesin digunakan, perangkat teknologi N3XT ternyata 63-1971 kali lebih efisien daripada yang dua dimensi.

Keuntungan dari N3XT dibandingkan sistem dua dimensi

Keuntungan dari N3XT dibandingkan sistem dua dimensiKedengarannya menjanjikan. Tetapi Wong tidak menyebarkan bagaimana tepatnya teknologi ini dalam 30 tahun ke depan akan dapat mempertahankan kecepatan peningkatan teknologi yang diperlukan untuk hukum Moore. Misalnya, transisi ke material nano baru akan memberi kita peningkatan kepadatan transistor satu kali terhadap komponen dua dimensi. Tetapi di sana, pada akhirnya, kita akan menghadapi pembatasan atom.

Secara teoritis, jika Anda dapat menggandakan ketinggian perangkat tiga dimensi setiap 18 bulan, Anda dapat mencapai peningkatan kepadatan per luas permukaan persegi. Tentu saja, untuk perangkat seluler dan tertanam, pendekatan ini akan dengan cepat menjadi terlalu rumit, dan chip untuk komputer di pusat data setelah tujuh hingga delapan generasi akan beristirahat di langit-langit 4 meter.

Agar semuanya dapat terus bekerja selama beberapa dekade, dan kepadatan untuk terus masuk ke dalam kurva hukum Moore, inovasi teknis lainnya yang tidak disebutkan oleh Wong perlu dikembangkan. Tetapi jika Anda menghasilkan chip seperti TSMC, Anda harus menerima bahwa para peneliti akan terus memberi Anda kandidat baru untuk teknologi yang hanya akan membutuhkan permintaan dari tugas baru yang lebih menuntut untuk memasuki pasar. Dan jika Anda mengingat kembali ceritanya, maka tugas-tugas seperti itu pasti akan muncul.