Pendahuluan

Suatu kali saya perlu menerapkan blok kecil CAM (memori asosiatif). Setelah membaca bagaimana Xilinx melakukan ini pada BRAM (blok memori statis) atau pada SRL16 (register geser 16-bit), saya sedikit sedih, karena implementasi mereka memakan banyak ruang. Saya memutuskan untuk mencoba melakukannya sendiri. Opsi pertama adalah implementasi dahi. Ke depan, itu datang hampir kepada saya segera dan, yah, frekuensi target untuk desain hanya 125 MHz.

Arsitektur

Untuk memulai, pertimbangkan pernyataan masalahnya. Jadi, kita perlu CAM kecil dengan lebar kata 8-64 bit dan kedalaman 16-1024 kata. Saya membutuhkan pencarian biner di CAM, tetapi kemudian ternyata membuat TCAM (memori asosiatif ternary) darinya cukup murah dalam hal sumber daya dan sedikit mempengaruhi waktu. Batas frekuensi yang lebih rendah adalah 125 MHz pada keluarga Kintex7 . Ayo mulai! CAM kami akan terdiri dari baris-baris ini, yang masing-masing akan sesuai dengan satu alamat dan menyimpan satu kata:

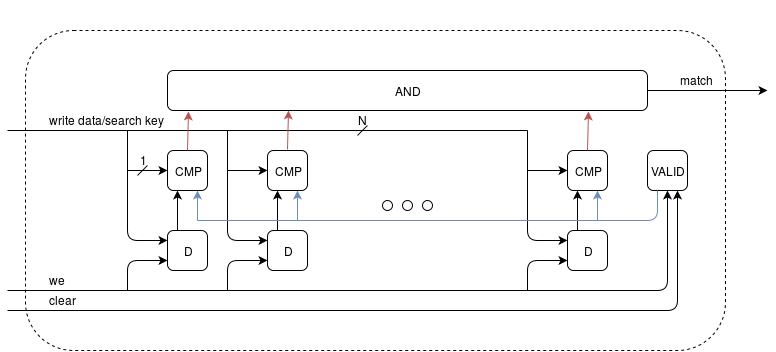

Gambar 1. Struktur satu baris CAM

Pada Gambar. 1, D adalah pemicu-D biasa untuk menyimpan data, jumlah pemicu ini di baris sesuai dengan lebar kata input data dalam CAM. VALID - D-trigger, yang menyimpan '1' jika data dalam baris relevan. CMP adalah pembanding yang membandingkan nilai bit bus kunci pencarian yang sesuai jika VALID = '1'. tulis data - tulis data bus, bitwise terhubung ke D yang sesuai ( N - CAM lebar kata), kita - tulis bendera, jelas - reset VALID (tidak valid dari baris data). AND - logical AND dari N output dari komparator, flag cocok berubah menjadi '1' jika pencarian di baris ini berhasil.

Jadi, kami memiliki satu baris di mana kami dapat mencari. Sekarang gabungkan mereka:

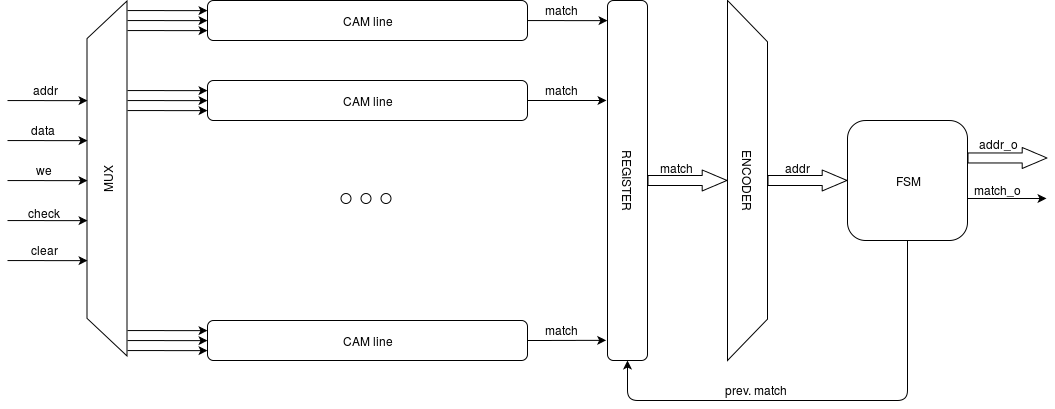

Gambar 2. Struktur CAM

Pada Gambar. 2, CAM_line adalah garis CAM sebenarnya dari Gambar. 1, MUX adalah multiplexer alamat input, MATCH REGISTER adalah register yang menyimpan nilai-nilai flag pertandingan, ENCODER adalah decoder yang mengubah bus pertandingan ke alamat pertandingan terendah yang ditemukan. FSM adalah mesin keadaan terbatas pengendali, yang berlaku . pertandingan menghapus dari MATCH REGISTER bit yang sesuai dengan alamat yang dikirim sehingga ENCODER beralih ke alamat yang ditemukan berikutnya. Antarmuka CAM kami adalah sebagai berikut:

Tabel 1. CAM Interface

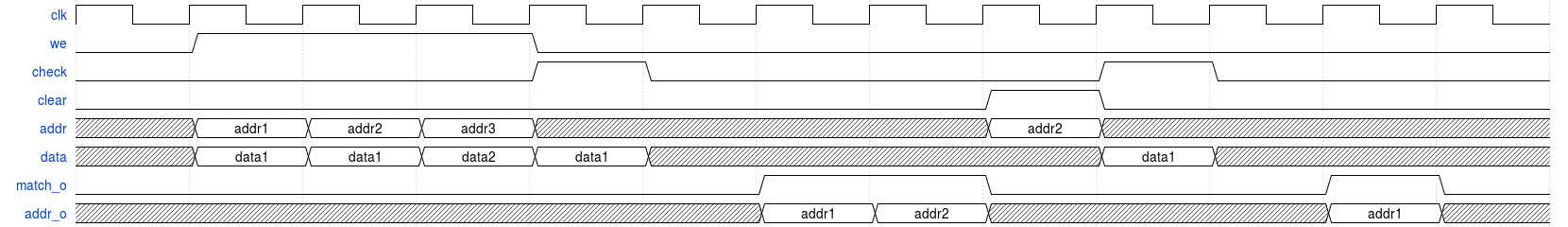

Di bawah ini pada Gambar. 3 adalah diagram waktu dari operasi antarmuka ini, yang menunjukkan pertama kali rekaman tiga kata dalam CAM, kemudian pencarian yang berhasil, penghapusan dan pencarian lagi:

Gambar 3. Diagram waktu antarmuka untuk CAM

Jadi, kami memiliki deskripsi CAM, mari beralih ke sintesis.

Sintesis

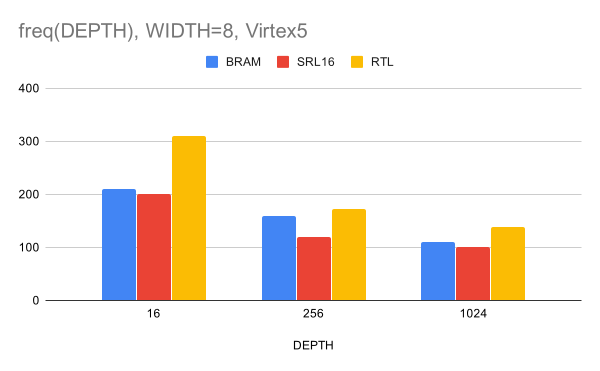

Kami akan mensintesis di Xilinx ISE untuk membandingkan hasil dengan yang diperoleh di XAPP1151 .

Gambar 4. Ketergantungan frekuensi setelah XST (synthesizer sebagai bagian dari ISE) pada kedalaman CAM untuk lebar bus data 8-bit

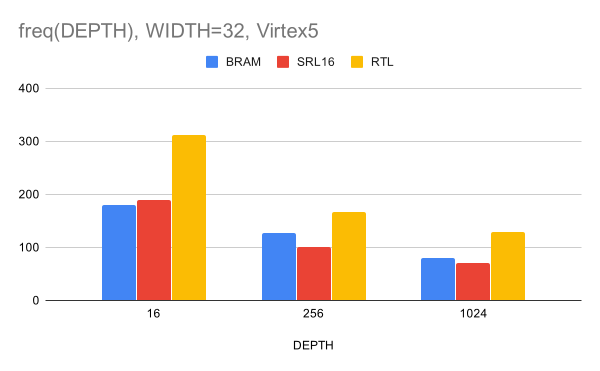

Gambar 5. Frekuensi setelah XST versus kedalaman CAM untuk lebar bus data 32-bit

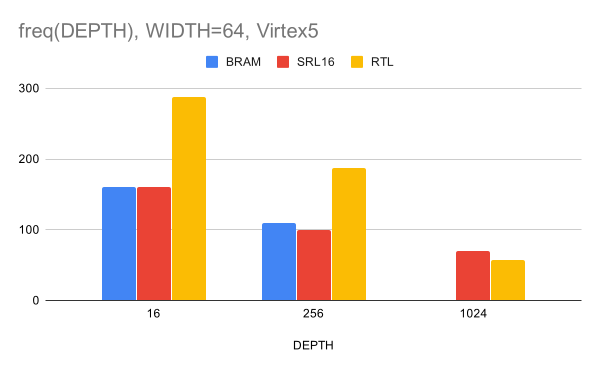

Gambar 6. Frekuensi setelah XST versus kedalaman CAM untuk lebar bus data 64-bit

Pada Gambar. 6, tidak ada data untuk Virtex5 , karena CAM dengan ukuran ini tidak cocok dengan BRAM yang ada. Kami juga mencatat bahwa untuk lebar 64 bit dan kedalaman 1024, hasil kami sedikit lebih buruk daripada implementasi pada SRL16. Sekarang mari kita beralih ke sintesis Vivado untuk XC7K325T . Hasilnya adalah sebagai berikut:

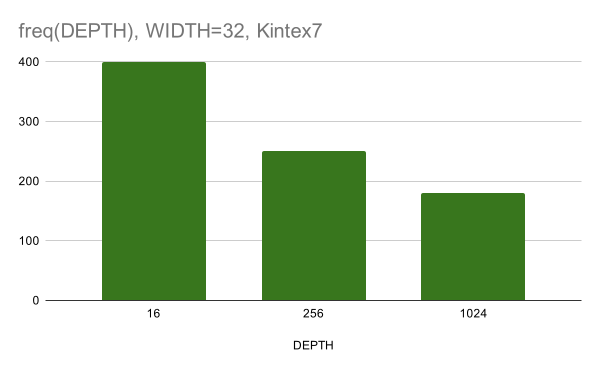

Gambar 7. Ketergantungan frekuensi setelah PnR (penempatan blok pada chip dan pelacakan sinyal) pada kedalaman CAM untuk lebar bus data 32-bit

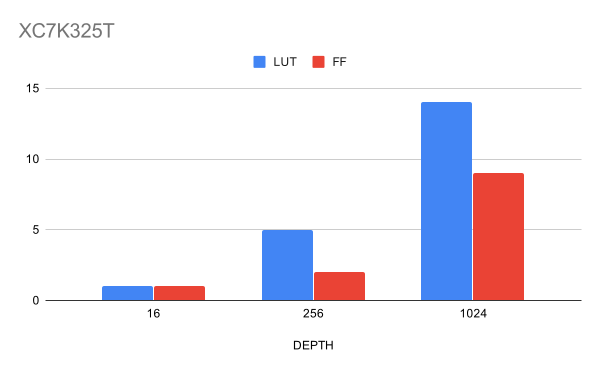

Gambar 8. Pemanfaatan sumber daya untuk berbagai kedalaman CAM untuk lebar data 32 bit dalam%

Penting untuk dicatat bahwa hasil pada Vivado diperoleh setelah PnR, yang berarti bahwa desain tidak mengalami kesulitan dengan penelusuran.

TCAM

Seperti disebutkan di atas, mendapatkan dengan pendekatan ini dari CAM TCAM bukanlah masalah khusus. Cukup menambahkan bus data masking untuk bit data dan mendistribusikannya sedikit demi sedikit ke dalam pembanding sehingga ketika membandingkan data dengan kunci, mereka memperhitungkan nilainya. Perubahan seperti itu tidak menyebabkan penurunan frekuensi atau peningkatan serius dalam sumber daya yang dikonsumsi, jadi kami mendapat TCAM gratis.

Kesimpulan

Jadi, kami bisa menyelesaikan tugas. Desain yang dihasilkan memungkinkan keluarga Xilinx FPGA ke-7 menerima CAM yang cukup besar dengan frekuensi di atas target 125 MHz. Hasil perbandingan dengan XAPP1151 ternyata tidak terduga bagi saya, saya berasumsi bahwa implementasi pada BRAM, meskipun sangat mahal dalam hal sumber daya, akan menyalip implementasi frontal dalam frekuensi. Namun, jangan merayakan kemenangan secepat ini , dokumen ini menjelaskan inti Xilinx CAM IP, yang memungkinkan, misalnya, untuk mendapatkan CAM dengan kedalaman 32K sel dan frekuensi 155 MHz, berdasarkan BRAM. Hasil ini mungkin dapat dicapai dalam versi yang diusulkan dalam artikel, baik dengan menambahkan tahapan pipa, atau dengan mengumpulkan CAM besar dari yang kecil, tapi saya tidak dapat langsung memprediksi apakah itu akan masuk ke dalam chip. Di masa depan saya akan mencoba menerapkan sesuatu yang serupa pada BRAM, tetapi untuk sekarang, terima kasih atas perhatian Anda.