Baru-baru ini, kami terlibat dalam pemulihan komputer kontrol on-board Apollo, sebuah komputer yang bertanggung jawab untuk mengendalikan, menavigasi, dan memantau kapal-kapal misi Apollo yang terbang ke Bulan. Komputer bersejarah ini adalah salah satu yang pertama kali menggunakan sirkuit terintegrasi (IC), dan prosesornya sepenuhnya dibangun di atas katup NOR (jenis IC kedua, amplifier pembacaan, digunakan dalam memori komputer). Pada artikel ini, saya akan menjelaskan arsitektur dan desain CPU.

Arsitektur Komputer Kontrol Apollo

Baki yang terpisah dari komputer kontrol Apollo. Baki kiri berisi logika berdasarkan gerbang NOR. Di sebelah kanan - memori dan komponen tambahan.

Baki yang terpisah dari komputer kontrol Apollo. Baki kiri berisi logika berdasarkan gerbang NOR. Di sebelah kanan - memori dan komponen tambahan.Apollo Guidance Computer (AGC) dikembangkan pada 1960-an untuk memungkinkan misi Apollo terbang ke bulan. Pada saat sebagian besar komputer mengambil ruang dari kulkas ukuran penuh ke seluruh ruangan, AGC adalah sesuatu yang unik - cukup kecil untuk masuk ke dalam pesawat ruang angkasa Apollo, beratnya 32 kg dan tidak lebih dari 0,03 m

3 (30 liter).

Komputer AGC adalah 15-bit. Sungguh aneh untuk memenuhi ukuran kata yang bukan kekuatan dua, tetapi pada 1960-an, bahkan sebelum byte menjadi populer, komputer menggunakan berbagai ukuran kata. 15 bit memberikan akurasi yang cukup untuk mendarat di bulan (dan menggunakan data dengan akurasi ganda dan tiga jika diperlukan), jadi 16 bit hanya akan menambah ukuran dan berat komputer secara tidak perlu.

Instruksi AGC terletak dalam kata 15-bit, dan terdiri dari 3 bit, menunjukkan kode operasi, dan 12 bit, menunjukkan alamat dalam memori. Sayangnya, volume ini masih belum cukup, sehingga komputer menggunakan banyak trik dan solusi, dan arsitekturnya ternyata agak canggung. Alamat memori 12-bit hanya dapat mengakses kata-kata 4K. Pada saat yang sama, AGC memiliki 2K kata dalam RAM utama dan 36K kata dalam memori inti. Untuk mengakses semua memori, AGC menggunakan sistem switching bank memori yang canggih dan beberapa register. Dengan kata lain, memori hanya dapat diakses dalam potongan 256 kata, dan ROM - dalam ukuran yang sedikit lebih besar.

3 bit untuk kode operasi tidak cukup untuk secara langsung menunjukkan 34 instruksi yang mungkin, oleh karena itu, AGC menggunakan trik dengan perluasan nilai instruksi dan dengan fakta bahwa beberapa instruksi masuk akal untuk dieksekusi hanya dengan sel memori tertentu. Selain itu, trik seperti alamat "ajaib" dalam memori digunakan - misalnya, menulis ke sel "register kanan" melakukan pergeseran bitwise, sehingga menghilangkan kebutuhan akan instruksi "shift kanan" yang terpisah. Ada juga instruksi yang menggabungkan beberapa tindakan sekaligus.

Arsitektur AGC cukup sederhana, bahkan menurut standar tahun 1960-an. Meskipun itu diciptakan di era mainframe yang kompleks dan kuat, kemampuan AGC sangat terbatas; dalam hal kekuatan dan arsitektur, ini sebanding dengan mikroprosesor awal. Kekuatannya adalah ukurannya yang ringkas dan kemampuan yang hebat untuk menyediakan input dan output data real-time.

Diagram arsitektur di bawah ini menunjukkan komponen utama AGC. Saya menyoroti bagian-bagian yang saya ingat dengan lebih detail. AGC memiliki satu set register kecil, dan modul aritmatika sederhana hanya berurusan dengan penambahan. Dia hanya memiliki 36K kata ROM dan 2K kata RAM. "Bus tulis" adalah cara utama untuk mentransfer data antar komponen. Instruksi decoding dan generator urutan menghasilkan pulsa kontrol untuk AGC.

Diagram blok AGC

Diagram blok AGCSekitar setengah dari diagram ditempati oleh memori, yang mencerminkan fakta bahwa dalam banyak aspek arsitektur AGC dikembangkan di sekitar memorinya. Seperti kebanyakan komputer di tahun 1960-an, AGC menggunakan memori inti, menyimpan setiap bit dalam cincin ferit kecil (inti) yang digantung di kawat. Karena setiap bit memerlukan inti fisik yang terpisah, jumlah memori tersebut secara radikal lebih kecil dari semikonduktor modern. Fitur khas memori pada inti adalah bahwa membaca kata dari memori menghapusnya, jadi setelah setiap akses nilai ini harus ditulis ulang. AGC juga memperbaiki memori ROM,

inti yang dijahit terkenal - mereka digunakan untuk menyimpan program, dan secara fisik dijahit dengan kabel (lihat di bawah).

Memori close-up pada inti yang dijahit

Memori close-up pada inti yang dijahitAtau katup

AGC adalah salah satu komputer pertama yang menggunakan IP. Kemungkinan IP pertama ini sangat terbatas; pada chip AGC (di bawah) hanya ada enam transistor dan delapan resistor, dan bersama-sama mereka mengimplementasikan gerbang NOR dengan tiga input.

Katup NOR ganda dengan tiga input dari AGC. Sepuluh kabel di luar kristal tersambung ke kontak eksternal IC.

Katup NOR ganda dengan tiga input dari AGC. Sepuluh kabel di luar kristal tersambung ke kontak eksternal IC.Penunjukan skema katup NOR diperlihatkan di bawah ini. Ini adalah gerbang logika paling sederhana: jika semua input sama dengan nol, maka output sama dengan satu. Anda mungkin terkejut, tetapi satu NOR-gate sudah cukup untuk membuat komputer. NOR adalah katup universal: katup logis lainnya dapat dibuat atas dasar itu. Misalnya, saat menggabungkan semua input NOR, kami mendapatkan inverter. Setelah menempatkan inverter pada output NOR, kami mendapatkan katup OR. Dengan menempatkan inverter pada input gerbang NOR, kita mendapatkan gerbang AND. Dan dari gerbang ini Anda dapat membangun logika yang lebih kompleks: pemicu, penambah, dan penghitung.

Katup NAND memiliki fleksibilitas yang sama. Di sirkuit modern, untuk alasan teknis, NAND digunakan lebih sering daripada NOR. Dalam kursus populer "

Dari NAND ke Tetris " menjelaskan cara membuat komputer dari NAND-katup, hingga implementasi game "Tetris". Pertama, satu set gerbang logika dibangun dari NAND (BUKAN, DAN, ATAU, XOR, multiplexer, demultiplexer). Kemudian, blok bangunan yang lebih besar dibuat darinya (trigger, adder, counter, ALU, register), dan dari mereka - komputer.

Gerbang NOR memberikan 1, jika memiliki 0 pada semua input, jika setidaknya satu input memiliki 1, maka NOR memberikan 0.

Gerbang NOR memberikan 1, jika memiliki 0 pada semua input, jika setidaknya satu input memiliki 1, maka NOR memberikan 0.Sangat sering dalam AGC menemukan komponen seperti pemicu RS (set-reset, set / reset). Sirkuit ini terbuat dari dua gerbang NOR dan menyimpan satu bit data. Bit 1 disimpan pada input yang ditetapkan, dan bit 0 disimpan pada input reset, yaitu pulsa 1, diterapkan untuk mengatur input, mematikan katup atas dan menghidupkan katup yang lebih rendah, sehingga output 1. Ternyata pulsa 1, diterapkan untuk mengatur ulang input, melakukan yang sebaliknya . Jika 0 diterapkan pada kedua input, pemicu mengingat status sebelumnya, memainkan peran drive. Di bagian selanjutnya, kami akan menunjukkan bagaimana register dibuat dari pemicu.

RS memicu dua gerbang NOR. Satu katup, ketika dihidupkan, mematikan yang lain. Baris di atas salah satu output menunjukkan bahwa itu melengkapi yang lain.

RS memicu dua gerbang NOR. Satu katup, ketika dihidupkan, mematikan yang lain. Baris di atas salah satu output menunjukkan bahwa itu melengkapi yang lain.Daftar

AGC memiliki set register kecil untuk penyimpanan sementara nilai di luar memori utama. Register utama adalah drive (A) yang digunakan dalam banyak operasi aritmatika. Ia juga memiliki register register Z, register blok aritmatika X dan Y, buffer B, alamat pengirim Q, dan beberapa lainnya (komputer modern menggunakan stack untuk memanggil subrutin dan kembali dari mereka, tetapi di era itu, programmer perlu menulis stack sendiri untuk rekursi ) Untuk akses ke memori, ada register alamat memori S, dan untuk data, register buffer memori G. Juga, AGC memiliki register di memori utama - misalnya, penghitung input / output.

Diagram di bawah ini menunjukkan skema register AGC, disederhanakan untuk kasing dengan satu bit dan dua register. Setiap bit register memiliki pemicu menggunakan skema yang dijelaskan sebelumnya (biru dan ungu). Data ditransfer ke dan dari register melalui bus tulis (merah). Untuk menulis ke register, pemicu diatur ulang oleh sinyal yang jelas (CQG atau CZG, hijau). Kemudian sinyal "tulis" (WQG atau WZG, oranye) memungkinkan data yang berjalan di sepanjang bus tulis untuk mengatur pemicu register yang sesuai. Untuk membaca register, sinyal baca (RQG atau RZG, cyan) melewatkan output trigger melalui penguat perekaman ke bus perekaman, dan digunakan di bagian AGC lainnya. Skema register lengkap lebih kompleks, ia memiliki beberapa register 16-bit, tetapi skema dasarnya adalah sebagai berikut.

Operasi register AGC yang disederhanakan

Operasi register AGC yang disederhanakanDaftar grafik menggambarkan tiga poin utama. Pertama, sirkuit register dibangun dari gerbang NOR. Kedua, pergerakan data dibangun di sekitar bus tulis. Akhirnya, tindakan register tergantung pada sinyal kontrol tertentu yang tiba pada waktu yang tepat.

Modul aritmatika

Sebagian besar komputer memiliki

perangkat logika aritmatika yang melakukan operasi aritmatika dan Boolean. Dibandingkan dengan komputer modern, modul aritmatika AGC sangat terbatas: ia hanya melakukan penambahan jumlah 16-bit, oleh karena itu disebut modul aritmatika dan bukan modul aritmatika-logis (sisa operasi dilakukan melalui berbagai trik; misalnya, pengurangan dilakukan melalui penambahan, sebelum itu untuk salah satu argumen, bit dibalik, dll.).

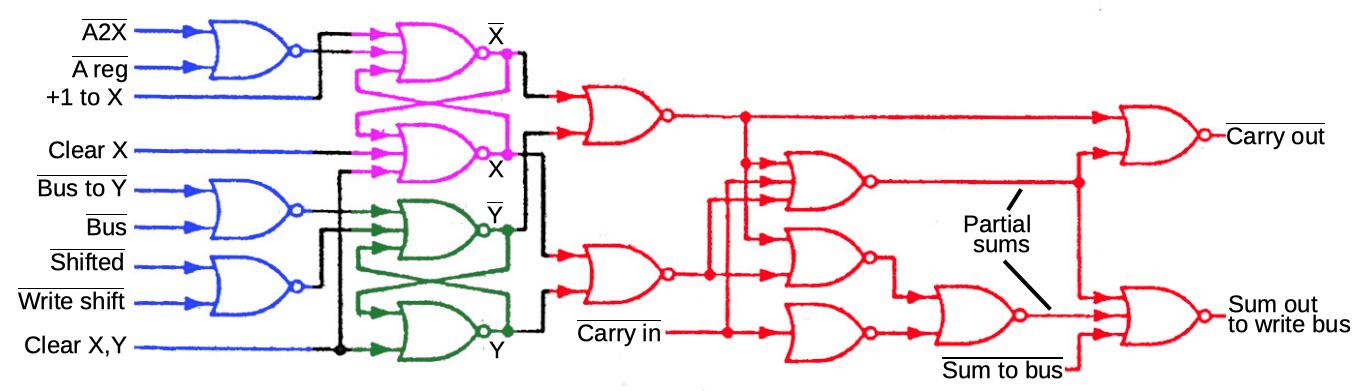

Diagram di bawah ini menunjukkan satu bit dari modul aritmatika AGC.

Penambah penuh (merah) menghitung jumlah dua bit dan membawa. Transfer ditransfer ke penambah berikutnya - dengan cara ini mereka dapat digabungkan untuk menambahkan kata-kata yang lebih panjang (untuk mempercepat transfer transfer dalam kasus-kasus seperti 111111111111111 +1, AGC menggunakan penambah dengan loncatan

transfer ).

Register X dan Y (ungu dan hijau) menyediakan dua bit input ke adder. Mereka diimplementasikan menggunakan pemicu yang sudah dijelaskan pada katup NOR. Loop biru menulis nilai-nilai ke register X dan Y sesuai dengan sinyal kontrol. Skema ini cukup rumit, karena memungkinkan Anda untuk menyimpan konstanta dan nilai dengan perubahan register, tetapi saya tidak akan membahas topik ini. Perhatikan sinyal kontrol A2X, yang mentransfer nilai register A ke register X; kita akan kembali padanya nanti.

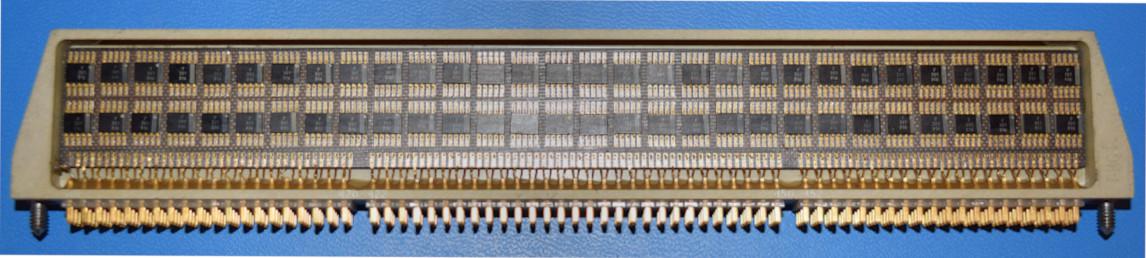

Foto di bawah ini menunjukkan implementasi fisik dari sirkuit AGC. Modul ini mengimplementasikan empat bit untuk register dan modul aritmatika. Kotak hitam adalah IP datar; setiap modul memiliki dua papan dengan masing-masing 60 chip, dan total 240 gerbang NOR. Modul dan register aritmatika disusun dari empat modul yang identik, yang masing-masing memproses empat bit; ini mirip dengan bagian

mikroprosesor .

Modul dan register aritmatika disusun dari empat modul yang identik. Modul dipasang dalam slot dari A8 ke A11.

Modul dan register aritmatika disusun dari empat modul yang identik. Modul dipasang dalam slot dari A8 ke A11.Eksekusi instruksi

Bagian ini menjelaskan urutan operasi yang dilakukan AGC untuk melaksanakan instruksi. Secara khusus, saya akan menunjukkan bagaimana instruksi ADS (add to storage) bekerja. Instruksi ini membaca nilai dari memori, menambahkannya ke drive (daftar A), dan menyimpan jumlahnya di penambah dan memori. Ini adalah instruksi tunggal, tetapi untuk pelaksanaannya AGC mengambil beberapa langkah dan banyak nilai dipindahkan ke sana-sini.

Timer instruksi diimplementasikan karena subsistem memori pada inti magnetik. Secara khusus, membaca nilai dari memori menghapus nilai yang disimpan, jadi setelah setiap pembacaan, nilai tersebut harus ditulis kembali. Juga, ketika mengakses memori, ada penundaan antara penunjukan alamat dan penerimaan data. Akibatnya, setiap siklus jam menghabiskan 12 langkah untuk membaca dan merekam selanjutnya. Setiap interval waktu (dari T1 ke T12) berlangsung sedikit kurang dari mikrodetik, dan seluruh siklus berlangsung 11,7 μs, dan disebut waktu siklus memori (MCT).

Modul memori inti magnetik yang dapat dihapus dari AGC. Ini menyimpan 2 kilo lembar, setiap bit disimpan menggunakan cincin ferit kecil yang terpisah.

Modul memori inti magnetik yang dapat dihapus dari AGC. Ini menyimpan 2 kilo lembar, setiap bit disimpan menggunakan cincin ferit kecil yang terpisah.MCT adalah unit dasar memori untuk menjalankan instruksi. Instruksi tipikal memerlukan dua siklus clock: satu untuk mengekstrak instruksi dari memori, yang kedua untuk melakukan operasi. Oleh karena itu, instruksi tipikal mengambil dua MCT (23,4 μs), yang memberi kita 43.000 instruksi per detik (dibandingkan dengan prosesor modern dan milyaran instruksi per detik, ini sangat lambat).

AGC memproses instruksi, memecahnya menjadi sub-perintah, yang masing-masing membutuhkan satu siklus clock memori. Misalnya, instruksi ADS terdiri dari dua sub-perintah: ADS0 (penambahan) dan STD2 (memanggil instruksi berikutnya). Diagram di bawah ini menunjukkan pergerakan data dalam AGC untuk menjalankan instruksi ADS0. 12 langkah dari kiri ke kanan.

Langkah-langkah paling penting adalah sebagai berikut:

T1: alamat operan disalin dari register instruksi B ke register alamat memori S untuk mulai membaca dari memori.

T4: Operan dibaca dari memori ke register data memori G.

T5: Operand disalin dari G ke adder Y. Nilai drive A disalin ke adder X.

T6: Penambah menghitung jumlah U, dan menyalinnya ke register data memori G.

T8: Penghitung program Z disalin ke register alamat memori S sebagai persiapan untuk menerima instruksi berikutnya dari memori.

T10: Jumlah dari register data memori G ditulis kembali ke memori.

T11: Jumlah U disalin ke drive A.

Meskipun ini adalah instruksi penjumlahan yang sederhana, banyak data yang dikirim berulang kali di sini selama 12 slot waktu. Dan dengan masing-masing tindakan ini sinyal kontrol spesifik dikaitkan; misalnya, sinyal A2X dalam interval T5 menyalin nilai dari drive A ke register X. Untuk menyalin register G untuk mendaftarkan Y, diperlukan dua pulsa kontrol: RG (baca G) dan WY (tulis Y). Pada bagian selanjutnya, saya akan menjelaskan bagaimana modul kontrol AGC menghasilkan sinyal kontrol yang diperlukan untuk setiap instruksi.

Modul kontrol

Seperti kebanyakan komputer, modul kontrol AGC menerjemahkan setiap instruksi dan menghasilkan sinyal kontrol yang memberi tahu seluruh prosesor apa yang perlu dilakukan. AGC menggunakan modul kontrol yang sudah diprogram yang terdiri dari katup NOR untuk menghasilkan sinyal. AGC tidak menggunakan mikrokode; ia tidak memiliki mikrostruksi dan memori kontrol, karena ini akan memakan terlalu banyak ruang fisik.

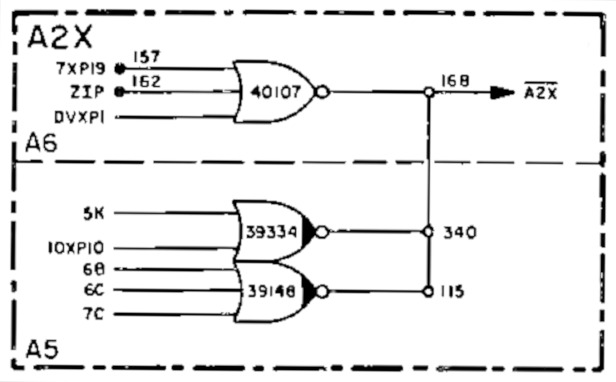

Jantung dari modul kontrol AGC disebut generator crosspoint. Dibutuhkan subperintah dan salah satu periode waktu dan menghasilkan sinyal kontrol untuk kombinasi ini. Dapat dibayangkan dalam bentuk kisi, di mana subperintah pergi dalam satu arah, dan segmen waktu di yang lain, dan masing-masing titik persimpangan memiliki sinyal kontrol sendiri.

Generator persimpangan memerlukan banyak komponen dan dibagi menjadi tiga modul; Ini adalah modul A6. Perhatikan kabel yang ditambahkan yang mengubah sirkuit. Ini adalah versi awal dari modul untuk pengujian di lapangan; modul penerbangan sudah tidak memiliki kabel.

Generator persimpangan memerlukan banyak komponen dan dibagi menjadi tiga modul; Ini adalah modul A6. Perhatikan kabel yang ditambahkan yang mengubah sirkuit. Ini adalah versi awal dari modul untuk pengujian di lapangan; modul penerbangan sudah tidak memiliki kabel.Untuk efisiensi, modul kontrol akhir sangat dioptimalkan. Instruksi dengan perilaku serupa digabungkan dan diproses bersama oleh generator persimpangan, yang mengurangi ukuran sirkuit yang diperlukan. Misalnya, AGC memiliki instruksi "tambahkan ke drive dengan presisi ganda" (DAS). Karena kira-kira setara dengan dua penambahan kata tunggal, sub-perintah DAS1 dan ADS0 dalam generator persimpangan memiliki logika yang sama. Diagram di bawah ini menunjukkan rangkaian generator persimpangan untuk interval waktu T5, dan logika dari sub-perintah ADS0 (menggunakan sinyal DAS1) disorot. Misalnya, sinyal 5K dihasilkan dari kombinasi DAS1 dan T5.

Tetapi apakah sinyal 5K dan 5L itu? Ini adalah optimasi lain. Banyak pulsa kontrol sering disatukan, jadi alih-alih menghasilkannya secara langsung, generator persimpangan menghasilkan sinyal perantara untuk persimpangan. Sebagai contoh, 5K menghasilkan pulsa kontrol A2X dan RG, dan 5L menghasilkan pulsa kontrol WY. Diagram di bawah ini menunjukkan bagaimana sinyal A2X dihasilkan: salah satu dari 8 sinyal yang berbeda (termasuk 5K) menghasilkan A2X. Sirkuit serupa menghasilkan sinyal kontrol lainnya. Optimalisasi ini memungkinkan untuk mengurangi ukuran generator persimpangan, tetapi masih tetap besar, dan tumbuh menjadi sebanyak tiga modul.

Ringkasnya, kita dapat mengatakan bahwa modul kontrol bertanggung jawab untuk memberi tahu CPU apa yang harus dilakukan untuk menjalankan instruksi. Pertama, instruksi dipecah menjadi sub-perintah. Generator persimpangan menghasilkan pulsa kontrol yang diperlukan untuk setiap interval waktu dan subperintah, memberi tahu register, modul aritmatika, dan memori apa yang harus mereka lakukan.

Biasanya, instruksi terdiri dari dua sub-perintah, tetapi ada pengecualian. Beberapa instruksi, seperti perkalian atau pembagian, mengharuskan penggunaan banyak sub-perintah, karena terdiri dari banyak langkah. Sebaliknya, instruksi lompat di TC menggunakan satu sub-perintah, karena hanya perlu memanggil instruksi berikutnya.

Prosesor lain menggunakan pendekatan berbeda untuk menghasilkan sinyal kontrol. 6502 dan banyak mikroprosesor awal lainnya menerjemahkan instruksi menggunakan array logika yang dapat diprogram (PLA) yang mengimplementasikan logika AND / OR melalui memori hanya baca.

Mikroprosesor 6502.

Mikroprosesor 6502.Kesimpulan

Itu adalah tur yang menarik dari komputer kontrol on-board Apollo. Agar tidak terlalu melar, saya berkonsentrasi pada instruksi penambahan ADS dan beberapa pulsa kontrol (A2X, RG dan WY). Saya harap Anda mendapat ide tentang cara merakit komputer dari elemen primitif seperti katup NOR.

Bagian yang paling terlihat dari arsitektur adalah jalur data: modul aritmatika, register dan bus data. Register AGC didasarkan pada pemicu sederhana dari gerbang NOR. Dan meskipun modul aritmatika AGC hanya dapat melakukan penambahan, komputer masih dapat menangani seluruh rangkaian operasi, termasuk operasi perkalian, pembagian, dan Boolean.

Namun, jalur data hanya bagian dari komputer. , , . , AGC, , .

, AGC , «», . , 60% 1963. AGC NOR-.

AGC , Tektronix

AGC , Tektronix