Boris Tsirlin dan Alexander Kushnerov

10/30/2019

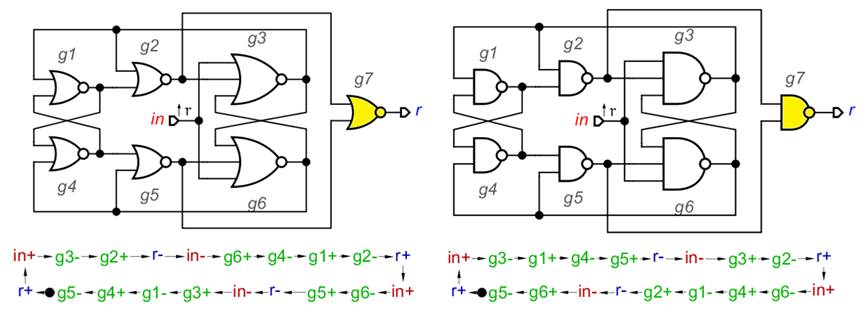

Tidaklah sulit bagi perancang sirkuit yang berpengalaman untuk menemukan sirkuit yang dikenalinya, tidak peduli dalam bentuk apa ia dibuat. Pada artikel ini, kami menunjukkan bahwa dua rangkaian transistor dari paten adalah varian pemicu penghitungan asinkron (AST). Dibandingkan dengan sirkuit standar, beberapa transistor hilang dari paten. Ini dapat dianggap sebagai kerusakan. Kami akan menunjukkan bahwa jika kesalahan yang sama terjadi di sirkuit standar, ia akan terus bekerja dengan benar. AST diimplementasikan hanya pada elemen OR-NOT [1] atau hanya pada elemen AND-NOT yang dikenal sebagai pemicu Harvard. Kedua varian skema ditunjukkan pada Gambar. 1, di mana g7 adalah indikator penyelesaian sementara. Di masa depan, kami tidak akan mempertimbangkannya. Dalam Fig. Gambar 1 juga menunjukkan grafik transisi sinyal (STG) [2] yang dibangun di Workcraft [3].

Fig. 1. Asynchronous counting trigger (AST) dan STG-nya.

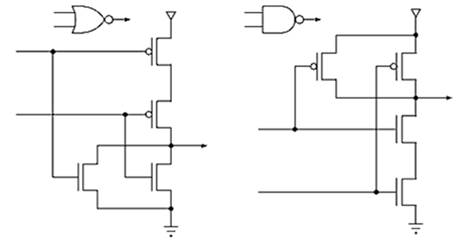

Perhatikan bahwa dalam kedua versi AST ada tiga pasang elemen (g1, g2), (g4, g5) dan (g3, g6) yang memiliki input yang sama. Rangkaian transistor elemen 2I-NOT dan 2OR-NOT ditunjukkan pada Gambar. 2. Tiga elemen input disusun dengan cara yang sama dan berisi 6 transistor.

Fig. 2. Rangkaian transistor elemen 2I-NOT dan 2OR-NOT.

Kami mengambil dua elemen 2OR-NOT dan memilih pada setiap input, di mana transistor p-MOS terhubung ke Upit. Hubungkan input ini bersama-sama dan hubungkan ke ground (log. 0). Kedua transistor akan terbuka dan tegangan pada salurannya sama dengan Upit. Apakah ini cukup untuk menghubungkan saluran dengan aman dan mengganti dua transistor dengan satu, seperti yang ditunjukkan pada Gambar. 3? Tidak. Anda perlu memeriksa apa yang terjadi jika Anda login pada input yang dibagikan. 1. Output dari kedua elemen akan terhubung ke tanah, dan kita akan memiliki rangkaian jembatan empat transistor p-MOS. Untuk dua input yang tersisa, kami memiliki empat kombinasi 0 dan 1. Mudah untuk menunjukkan bahwa tidak satupun dari mereka ada hubungan pendek antara Upit dan ground.

Fig. 3. Dua elemen 2OR-NOT berbagi input yang sama.

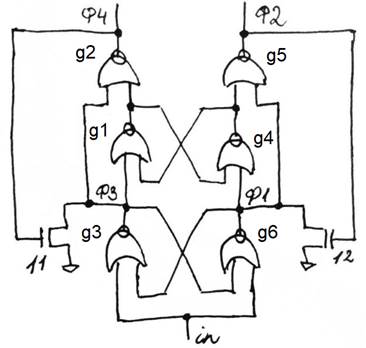

Kami sekarang mempertimbangkan sirkuit distributor pulsa [4] pada Gambar. 4. Menggunakan Gambar. 3, kita dapat menggambar ulang diagram ini seperti yang ditunjukkan pada Gambar. 5. Sudah dimungkinkan untuk mengenali AST pada Gambar. 1, namun, di sana elemen g3 dan g6 memiliki 3 input.

Fig. 4. Skema distributor pulsa dari [4].

Fig. 5. Varian dari sirkuit pada Gambar. 4.

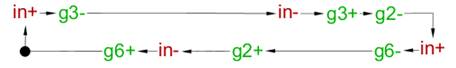

Gerbang transistor 11 dan 12 dapat dianggap sebagai input elemen 3OR-NOT di mana transistor p-MOS ketiga disingkat. Apakah ini memengaruhi operasi rangkaian yang benar? Pertimbangkan urutan penampilan sinyal di, g2, dan g6 pada input elemen g3. Untuk melakukan ini, hapus semua sinyal lain dalam STG yang sesuai pada Gambar. 1 seperti yang ditunjukkan pada Gambar. 6.

Fig. 6. STG untuk ATAU TIDAK. Sinyal masuk, g2, g6 dan g3.

Karena p-MOS transistor ketiga disingkat, switching g3 + dapat terjadi setelah beralih in- dan g6- (dalam urutan apa pun) tanpa mengizinkan switching g2-. Namun, seperti yang dapat dilihat dari Gambar. 6, pada bagian dari g2 + ke g2- hanya ada di- dan g6 +, oleh karena itu, perpindahan g3 + terlarang tidak terjadi. Sebelum beralih g2 +, elemen g3 sudah pada 0, dan pada inputnya g6 masih 0, yaitu Transistor p-mos pertama terbuka. Switching g2 + membuka transistor 11 dan harus mematikan transistor p-MOS korsleting. Ini tidak terjadi, apalagi, beralih membuka transistor p-MOS kedua. Jadi, melalui dua transistor p-MOS terbuka dan transistor terbuka 11, arus mulai mengalir dari Upit ke ground. Ini berlanjut untuk waktu yang singkat sampai saklar g6 + berikutnya menutup transistor p-MOS pertama. Selama ini, transistor 11 menyediakan 0 pada output g3. Bagaimana tepatnya? Misalkan resistansi transistor p-MOS dan n-MOS terbuka adalah sama dan sama dengan R, maka setelah beralih tegangan g3 melonjak dari 0 ke (1/3) Upit, tetapi ini dalam kasus yang ideal. Dalam praktiknya, ada beberapa kapasitansi parasit antara g3 dan tanah, tegangan yang meningkat dengan lancar dan mungkin tidak mencapai (1/3) Upit. Dengan satu atau lain cara, tegangan ini akan kurang dari (1/2) Upit dan berarti log. 0. Untuk transistor 12, semuanya mirip, ia menyediakan waktu singkat 0 pada output g6. Dengan demikian, penundaan elemen g6 dan g3 menentukan dua periode waktu ketika pemicu mengkonsumsi arus besar kira-kira sama dengan Upit / (3R).

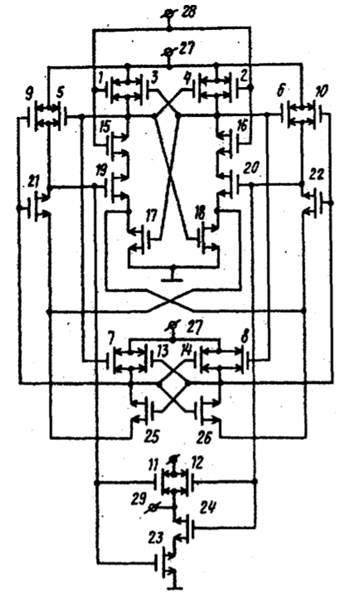

Sekarang mari kita pertimbangkan sirkuit pemicu penghitungan [5] pada Gambar. 7. Di sini transistor 11, 12, 24, 23 membentuk elemen 2I-NOT, yang, tampaknya, merupakan indikator AST pada Gambar. 1. Elemen lain 2I-NOT dibentuk oleh transistor 7, 13, 25 dan 18. Mari kita perhatikan fakta bahwa transistor 18 terhubung ke ground dan mirip dengan contoh pada Gambar. 3, umum untuk tiga elemen DAN TIDAK. Elemen kedua 2I-NOT, yang meliputi transistor 18, dibentuk oleh transistor 5, 9, 21, dan yang ketiga adalah 3I-NOT pada transistor 2, 4, 16, 20. Sejalan dengan transistor 2 dan 4, harus ada transistor p-MOS ketiga tapi dia tidak ada. Sirkuit pada Gambar. 7 simetris, untuk pemahaman yang lebih baik kita menggambar ulang seperti yang ditunjukkan pada Gambar. 8.

Fig. 7. Skema pemicu terhitung dari [5].

Fig. 8. Varian dari sirkuit pada Gambar. 7.

Apakah akan ada keluaran g3 dan g6 pada Gambar. 8 beralih dengan benar jika transistor p-mos ketiga secara paralel hilang? Ini akan dipahami setelah menganalisis STG pada Gambar. 9, yang, seperti dalam kasus sebelumnya, diperoleh dari STG yang sesuai pada Gambar. 1 dengan menghapus semua sinyal kecuali di, g2, g6, dan g3.

Fig. 9. STG untuk NAND. Sinyal masuk, g2, g6 dan g3.

Elemen g3 adalah 3I-NOT, jadi setelah beralih di +, g6 + dan g2 + (dalam urutan apa pun), g3- akan beralih. Saklar terbalik in-, g6-, atau g2- harus menyebabkan sakelar g3 +. Namun, g2- tidak dapat membuka transistor p-MOS yang hilang, sehingga g3 akan tetap pada 0 dan akan menunggu in- atau g6- untuk beralih. Seperti dapat dilihat dari Gambar. 9, pada bagian dari g3- ke g3 + tidak ada switching g2- dan transistor p-MOS tidak diperlukan di sini. Di sisi lain, transistor ini harus menyediakan log. 1 ke g3 saat di dan g6 beralih secara sewenang-wenang. Pertimbangkan dalam Gbr. Bagian ke-9 dari g3 + ke g2 +. Switching g2- menutup transistor 19. Selanjutnya, beralih + menutup transistor 1 dan membuka transistor 15. Elemen g6 tetap pada 1, yaitu transistor 17 terbuka, dan transistor 3 ditutup. Dengan demikian, dalam + memutuskan g3 dari bumi dan Upit. Namun, log disimpan di g3. 1, karena dalam praktiknya ada kapasitansi parasit antara g3 dan ground, yang diisi hingga Upit. Beralih g6- membuka transistor 3 dan menghubungkan kapasitansi ini ke Upit. Untuk paruh kedua skema, semuanya serupa. Dengan demikian, keterlambatan elemen g6 dan g3 menentukan waktu selama keadaan disimpan di tangki. Dalam praktiknya, penting bahwa arus bocor dari transistor 19 dan 20 kecil, jika tidak kapasitansi dapat mengalir di bawah (1/2) Upit dalam waktu yang ditentukan.

Dibandingkan dengan AST standar pada Gambar. 1, dalam diagram pada Gambar. 5 dan Gambar. 8, fungsi pengaturan ke 1 elemen 3 ATAU TIDAK dan fungsi reset ke 0 dari elemen 3 ATAU TIDAK rusak. Ini berarti bahwa AST standar akan terus bekerja dengan benar, bahkan jika kerusakan yang terjadi terjadi pada elemen g6 dan g3. Untuk rangkaian standar (tanpa g7), diperlukan 28 transistor. Untuk sirkuit pada Gambar. 4 dan Gambar. 7 (tanpa transistor 11, 12, 24, 23) Anda masing-masing membutuhkan 23 dan 22 transistor. Jika Anda mengembalikan transistor p-MOS yang hilang, sirkuit ini akan bekerja lebih andal. Jumlah minimum transistor dalam rangkaian pada Gambar. 7 tidak selalu berarti bahwa itu lebih baik daripada sirkuit pada Gambar. 4 dan sirkuit yang lebih baik pada Gambar. 1. Selain jumlah transistor dan konsumsi saat ini, ada parameter penting lainnya, misalnya,

- kompleksitas sirkuit tambahan untuk mengatur kondisi awal

- kapasitas muat (laju muat ulang kapasitas muat)

- tingkat keluar dari negara metastable

- jumlah dan nilai kapasitansi parasit

- jumlah dan nilai arus bocor

Analisis komparatif dari parameter-parameter ini, serta diskusi tentang skema AST yang diterapkan pada elemen lain, berada di luar cakupan artikel ini.

Sastra

[1] GT Osborne, "Tahap register biner asinkron dengan flip-flop dan gate menggunakan pluralitas sirkuit NOR yang saling berhubungan." Paten US3139540, 30 Juni. 1964.

[2] L. Ya. Rosenblum dan A. V. Yakovlev, "Pada bentuk grafik baru untuk menggambarkan esensi dari penemuan ini," Issues of Invention, No. 11, hlm. 36-40, 1988.

[3] https://workcraft.org

[4] V. I. Goryachev, B. M. Mansurov, Ya D. Martynenko dan R. G. Talibov, “Distributor pulsa empat fase”. Sertifikat hak cipta SU342299, 06/14/1972.

[5] V. I. Varshavsky, N. M. Kravchenko, V. B. Marakhovsky dan B. S. Tsirlin, “Menghitung pemicu pada transistor CMOS”. Sertifikat hak cipta SU1398069, 05.23.1988.