Dalam kondisi modern, insinyur desain perlu terus-menerus mendapatkan pengetahuan baru agar permintaan di pasar tenaga kerja. Seringkali, informasi baru harus diterima, sehingga untuk berbicara, "tanpa gangguan dari produksi": selama bekerja pada suatu proyek, pada perjalanan ke tempat kerja, dll. Dunia digital modern memungkinkan ini, itu akan menjadi keinginan. Namun, terkadang kualitas pengetahuan yang didapat dapat menurun. Informasi diasimilasi oleh seseorang secara dangkal atau bahkan dalam bentuk yang menyimpang.

Berkomunikasi dengan pelacak perangkat lunak yang bekerja dalam perangkat lunak CAD untuk Cadence OrCAD / papan sirkuit cetak Allegro, saya kadang-kadang memperhatikan bahwa orang tidak terlalu mementingkan indikasi warna bidang dalam editor aturan Constraint Manager. Yaitu: pengguna tidak memperhatikan fakta bahwa beberapa kolom dicat dengan warna kuning.

Bahkan, warna kuning pada editor aturan Cadence berarti bahwa pemeriksaan ini tidak dapat dilakukan karena alasan apa pun. Alasannya mungkin berbeda:

- Validasi dinonaktifkan oleh pengguna.

- Jalur konduktif tidak diletakkan sama sekali atau tidak selesai.

- Alasan lain

Dalam kebanyakan kasus, tidak ada situasi fatal di mana kesalahan muncul yang menyebabkan perangkat lunak tidak dapat dioperasikan. Karena OrCAD PCB Editor memiliki mekanisme multi-tahap untuk memeriksa proyek pada DRC, seperti itu, Anda tidak dapat mematikannya dalam sekali jalan. Namun, kadang-kadang karena kesenjangan pengetahuan yang mengganggu, atau karena kurangnya perhatian, situasi dibuat yang mengarah pada situasi yang salah dalam proyek.

Sebagai contoh, satu pengembang mengatakan kepada saya bagaimana ia secara tidak sengaja mematikan memeriksa korslet baris yang berlawanan satu sama lain. Selain itu, perangkat lunak CAD tidak akan melaporkan kesalahan dalam situasi ini, karena verifikasi dinonaktifkan oleh pengguna.

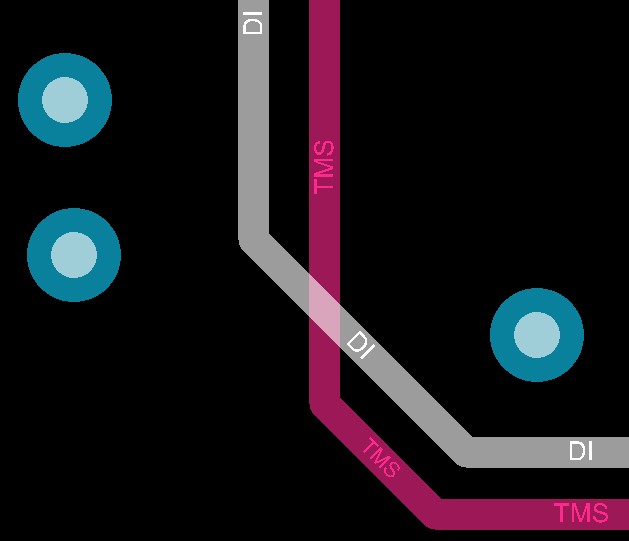

Persimpangan satu konduktor dengan yang lain tanpa pesan kesalahan

Persimpangan satu konduktor dengan yang lain tanpa pesan kesalahanGambar tersebut menunjukkan bahwa konduktor dari garis yang berlawanan berpotongan satu sama lain. Namun, pesan kesalahan tidak terjadi. Alasan perilaku program ini tidak jelas bagi pengembang, karena selama pelacakan online semua celah yang diatur dalam manajer konstan disimpan dan dipelihara.

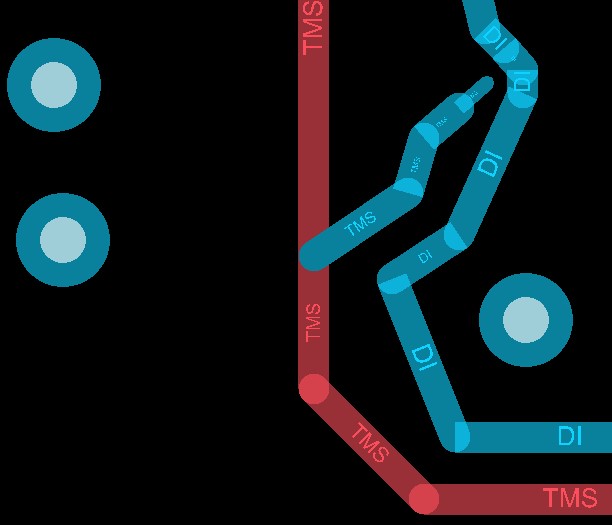

Kesenjangan dan aturan di kawasan didukung saat melacak

Kesenjangan dan aturan di kawasan didukung saat melacakKurangnya token DRC terletak tepat di pengaturan Constraint Manager.

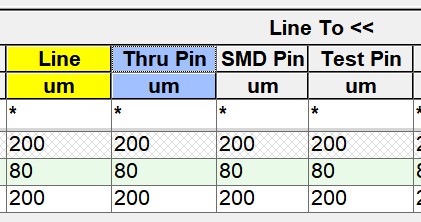

Seperti inilah verifikasi yang dinonaktifkan pada Constraint Manager

Seperti inilah verifikasi yang dinonaktifkan pada Constraint ManagerWarna kuning pada bagian pemeriksaan celah Line-to-Line berarti bahwa pemeriksaan tidak dilakukan (atau tidak dapat dilakukan). Karena itu, penanda DRC tidak muncul. Tentu saja, penonaktifan sebagian pemeriksaan terkadang sangat mudah dan dapat mengurangi total waktu untuk memeriksa suatu proyek, tetapi .... Hal ini dapat mengakibatkan konsekuensi fatal jika, ketika mengirimkan proyek dan menghasilkan file untuk produksi, pengembang tidak menyertakan semua pemeriksaan yang diperlukan dan tidak melakukan pemeriksaan DRC akhir dengan mereka.

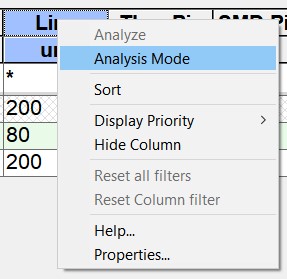

Menonaktifkan atau mengaktifkan pemeriksaan tertentu dalam Cadence sangat sederhana: cukup klik pada header sel yang diinginkan dan pilih Mode Analisis dari menu drop-down.

Aktifkan atau nonaktifkan jenis pemeriksaan tertentu dengan cepat

Aktifkan atau nonaktifkan jenis pemeriksaan tertentu dengan cepatKetika cek dihidupkan, warna tutupnya abu-abu, ketika cek dinonaktifkan, warna tutupnya kuning.

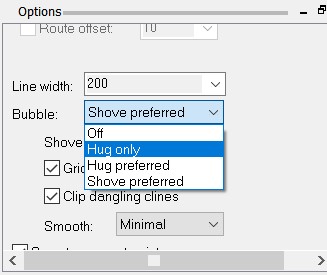

Mengapa, ketika pengecekan dinonaktifkan di Constraint Manager, celah yang diperlukan masih didukung selama pelacakan, dan OrCAD PCB Designer mencegah pengguna agar tidak sengaja membuat kesalahan? Hal ini disebabkan oleh fakta bahwa sistem verifikasi DRC terdiri dari dua bagian: Online-time DRC check, dan Batch Mode DRC on-demand cek. Mode Batch DRC dimatikan secara paksa di Constraint Manager. DRC online terus berfungsi jika dalam mode jejak nilai parameter Bubble di jendela Options berbeda dari keadaan OFF.

Nilai yang mungkin diambil parameter Bubble

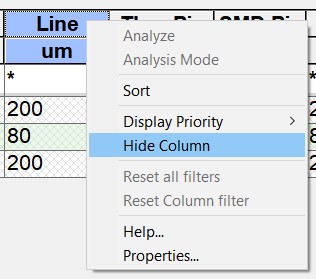

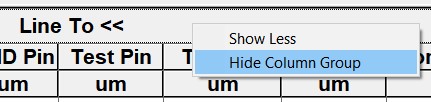

Nilai yang mungkin diambil parameter BubbleJika seorang insinyur tidak ingin melihat pemeriksaan yang dinonaktifkan atau beberapa bagian dalam editor aturan Constraint Manager, maka mereka dapat dengan mudah disembunyikan.

Sembunyikan kolom atau bagian dari pertimbangan

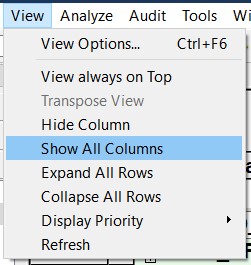

Sembunyikan kolom atau bagian dari pertimbanganKetika pemeriksaan menjadi perlu lagi, itu dapat dikembalikan di bidang kolom yang ditampilkan.

Kembalikan kolom yang tersembunyi

Kembalikan kolom yang tersembunyiPerlu dicatat bahwa editor tabel aturan CAD Cadence Allegro / OrCAD, dengan semua kekuatannya, sangat mudah dan mudah untuk dikonfigurasikan, dan pemeriksaan itu sendiri dilakukan dengan cukup cepat, sehingga seringkali tidak perlu memaksakan sesuatu untuk dimatikan.

Di sisi lain, jika perlu untuk menonaktifkan beberapa pemeriksaan yang sangat lambat, pengembang pertama-tama dapat menyimpan file "teknologi" yang berisi pengaturan untuk semua pemeriksaan yang diperlukan, kemudian menonaktifkannya untuk sementara, dan ketika mengeluarkan dokumentasi desain setelah pelacakan selesai, muat kembali file teknologi tersebut dengan semua cek dan jalankan DRC final.

Ya, omong-omong, jika Anda ingat pengembang yang mematikan tes hubung singkat antara sirkuit - untungnya, produsen PCB ketika ia mulai memesan menarik perhatiannya pada masalah sirkuit di antara sirkuit, sehingga mereka berhasil menghindari kerugian finansial dan waktu. Tetapi, dari pengalaman di sebuah perusahaan yang bergerak dalam pembuatan papan sirkuit cetak, saya dapat mengatakan bahwa masalah penonaktifan cek "tidak perlu" sangat sering ditemui, oleh sebagian besar pelanggan, dan tidak bergantung pada pengembang CAD mana yang bekerja. Jadi jangan lupa untuk memasukkannya di waktu yang tepat!