Anotasi

Antarmuka MIPI saat ini menjadi antarmuka yang semakin populer untuk menghubungkan kamera dan tampilan. Karena alasan ini, semakin banyak kit debugging berbasis-FPGA berisi konektor antarmuka MIPI di papan - baik untuk menghubungkan kamera dan tampilan. Untuk mulai bekerja dengan teknologi baru atau hanya untuk melihat seperti apa, pengembang berusaha menemukan panduan yang sesuai di Internet, yang akan menggambarkan nuansa kerja yang relevan. Di satu sisi, test case seharusnya naik pada debugging kit, dan di sisi lain, case tersebut harus memberikan pemahaman yang cukup sederhana dan luas tentang apa yang terjadi dalam test case ini.

Tujuan artikel ini adalah untuk menunjukkan cara mulai bekerja dengan antarmuka MIPI menggunakan salah satu debugging terbaru dari Xilinx -

SP701 , kamera dengan antarmuka MIPI dari Digilent

PCAM-5C dan lingkungan pengembangan Vivado + VITIS (SDK) dari Xilinx

Daftar peralatan

Dimulai dengan rilis pertama VITIS dan Vivado 2019.2, Xilinx memberi pengembang kesempatan untuk menghasilkan test case untuk bekerja dengan antarmuka MIPI pada papan

SP701 . Sebelumnya, proyek tersedia untuk papan

ZCU102 , namun, karena contohnya membutuhkan kamera yang agak spesifik, kami tidak memiliki kesempatan untuk menjalankan proyek uji. Dengan dirilisnya anggaran

SP701 , yang juga menghubungkan kamera anggaran PCAM-5C, kesempatan seperti itu muncul.

PS0: panduan ini tidak akan memberi tahu Anda apa itu MIPI, terdiri dari apa, atau teori lain yang dapat ditemukan di Internet. Di sini kita akan fokus pada bagaimana menghasilkan proyek pengujian. Selanjutnya, dengan menggunakan proyek ini, Anda sendiri dapat memasang modul tambahan dan pemrosesan video yang ditentukan dalam kerangka acuan untuk proyek Anda.

PS1: Kami tidak akan berteriak-teriak, tetapi fokus pada tindakan. Hanya gambar, hanya hardcore.Mari kita mulai.

Perangkat Lunak yang Diperlukan

Untuk panduan ini, kita perlu Vivado 2019.2 dan VITIS, yang diunduh dari

tautan . VITIS berisi Vivado, jadi tidak perlu mengunduh VITIS dan Vivado, cukup unduh dan instal VITIS. Vivado akan diinstal secara otomatis.

Langkah 1: Buat Proyek Vivado

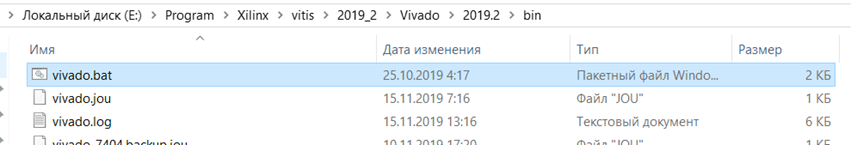

1. Luncurkan Vivado 2019.2

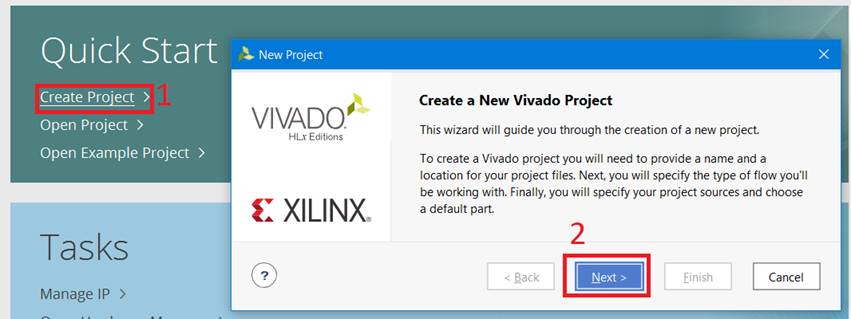

2. Klik “Buat proyek” (1) :: Klik “Selanjutnya” (2)

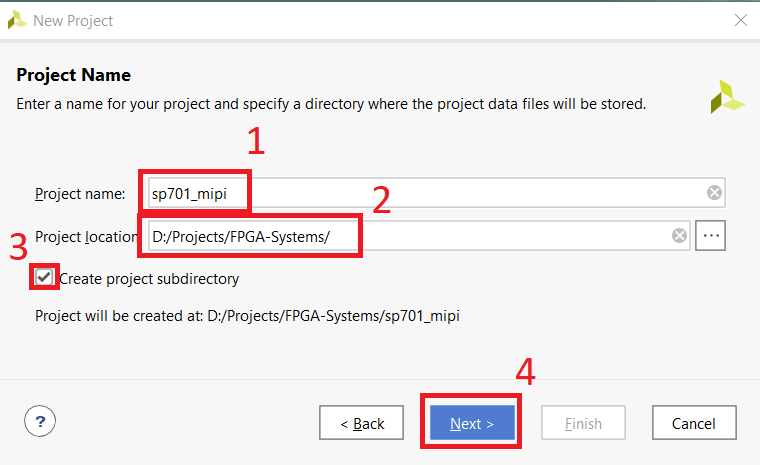

3. Tentukan "Nama proyek" (1) :: Tentukan direktori proyek (2) :: Centang kotak (3) :: Klik "Next" (4)

4. Pilih jenis proyek (1) :: Setel kotak centang (2) :: Klik “Selanjutnya” (3)

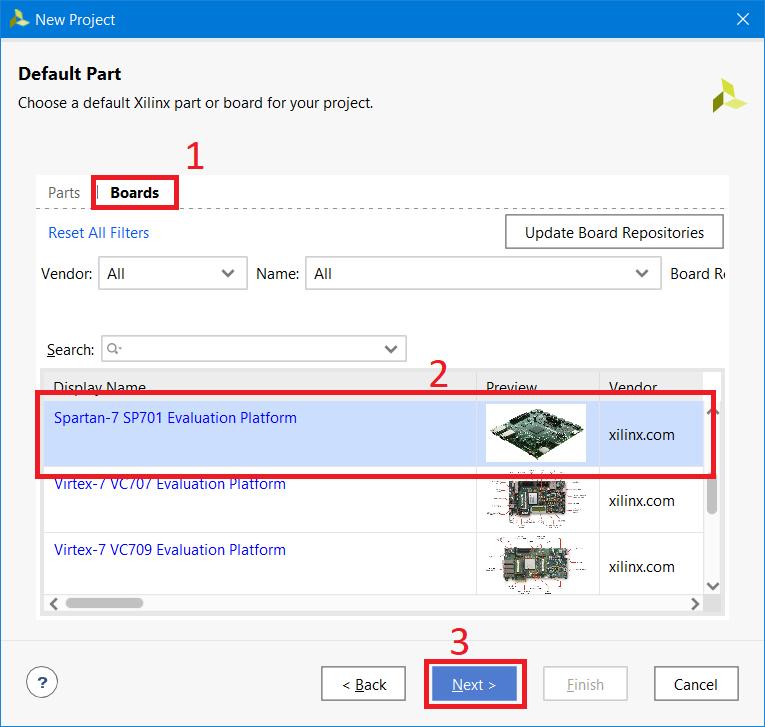

5. Buka tab "Papan" (1) :: Temukan dan pilih SP701 (2) :: Klik “Selanjutnya” (3)

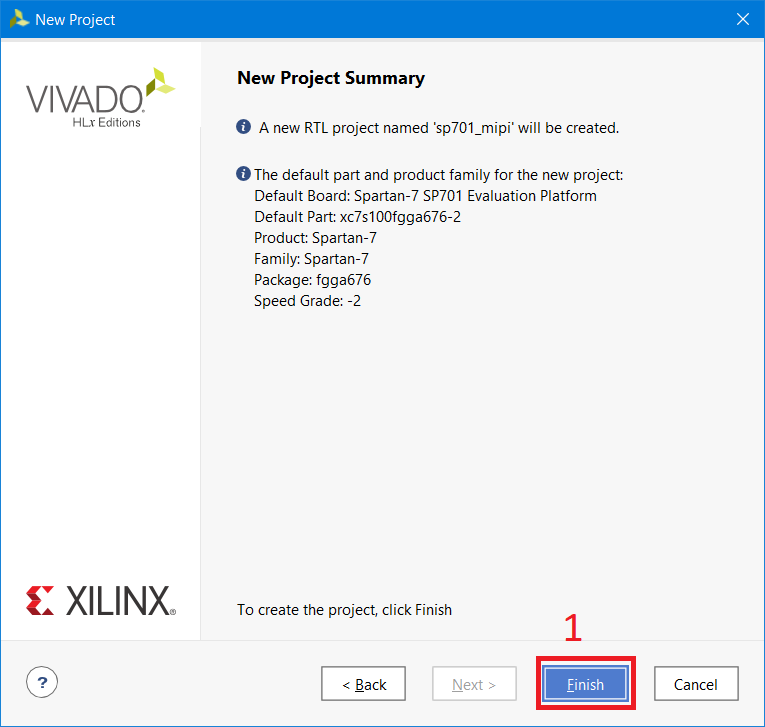

6. Klik "Selesai" (1)

Langkah 2: Instal Lisensi

Mengingat bahwa kita akan menggunakan IP Core, yang memerlukan lisensi, kita perlu membuat dan menginstalnya. Proyek uji menggunakan IP untuk menghubungkan kamera (MIPI CSI-Rx) dan layar (MIPI DSI-Tx), di mana Xilinx menawarkan lisensi uji coba untuk jangka waktu 120 hari.

PS: Dalam proyek pengujian, output gambar diduplikasi ke antarmuka HDMI, keberadaan tampilan dengan antarmuka MIPI tidak diperlukan, tetapi lisensi DSI-Tx diperlukan.

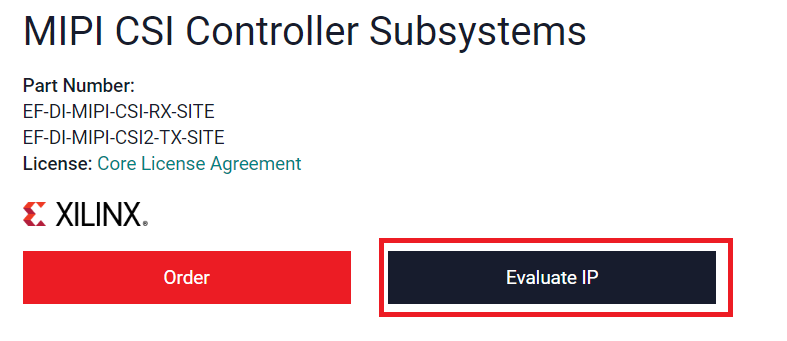

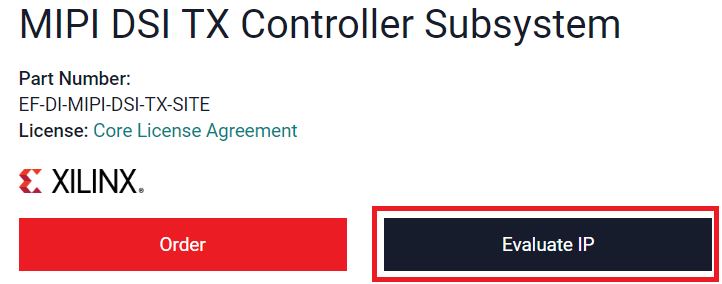

7. Dapatkan lisensi untuk CSI-Rx (koneksi kamera) dengan mengklik

tautan dan klik "Evaluate IP". Kemudian ikuti instruksinya.

8. Dapatkan lisensi untuk DSI-Tx (koneksi layar) dengan mengklik

tautan dan klik "Evaluate IP". Kemudian ikuti instruksinya.

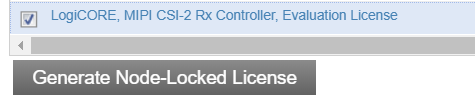

9. Unduh file lisensi.

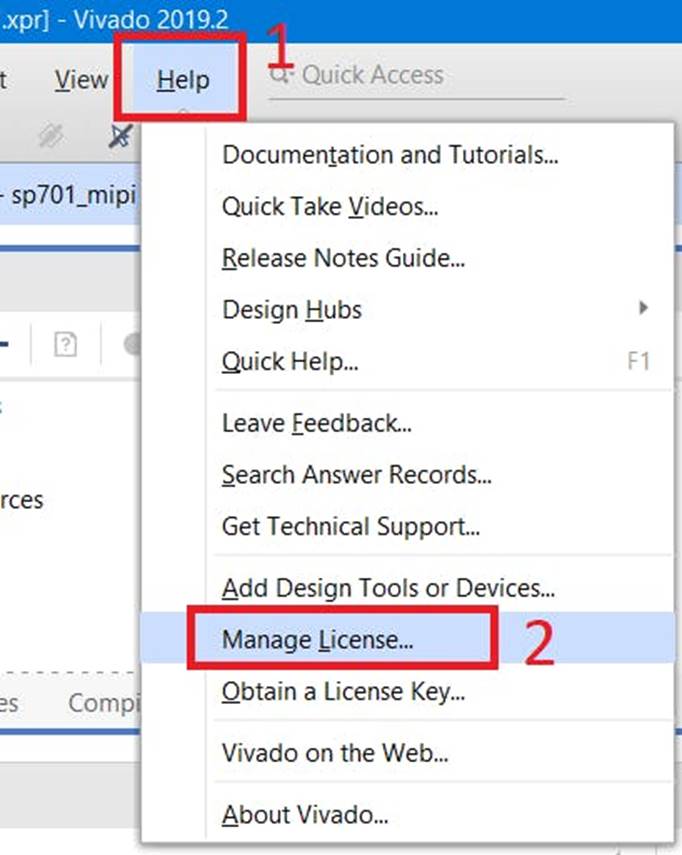

10. Di jendela Vivado, klik "Bantuan" (1) :: Pilih "Kelola Lisensi" (2)

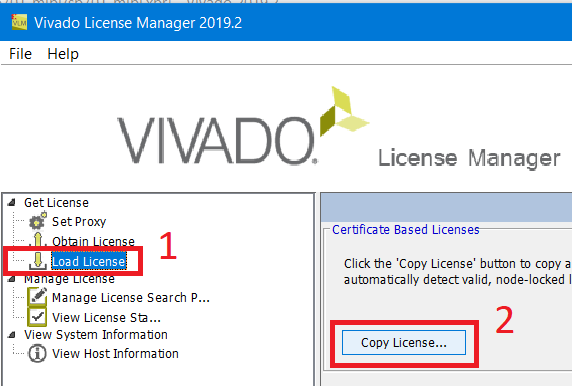

11. Di manajer lisensi, pilih "Muat lisensi" (1) :: Lalu "Salin lisensi" (2). Pilih lisensi .lic yang diunduh untuk core IP CSI dan DSI

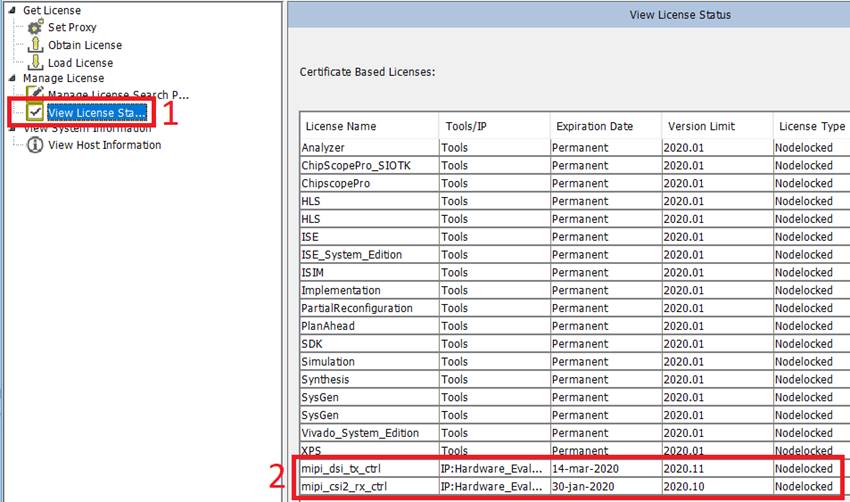

12. Di manajer lisensi, pilih "Lihat Status Lisensi" (1) :: Pastikan lisensi diambil dengan benar (2)

Langkah 3: Buat Proyek Uji

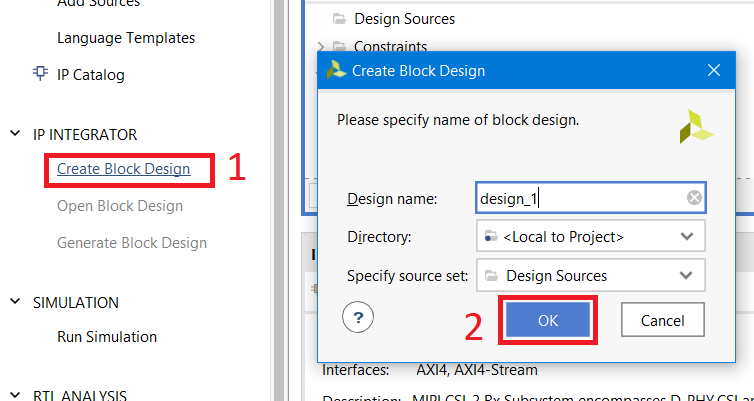

13. Di Vivado, klik “Buat desain blok” (1) :: Klik “OK” (2)

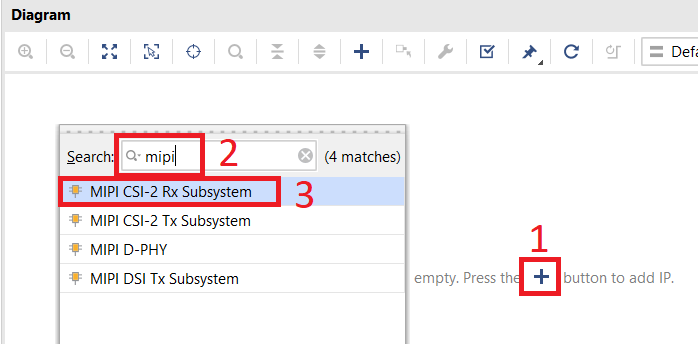

14. Pada bidang IP Integrator, klik "+" atau "ctrl + i" (1) :: Ketik "mipi" di bidang "Search" (2) :: Klik dua kali pada "Subsistem MIPI CSI-2 Rx" (3)

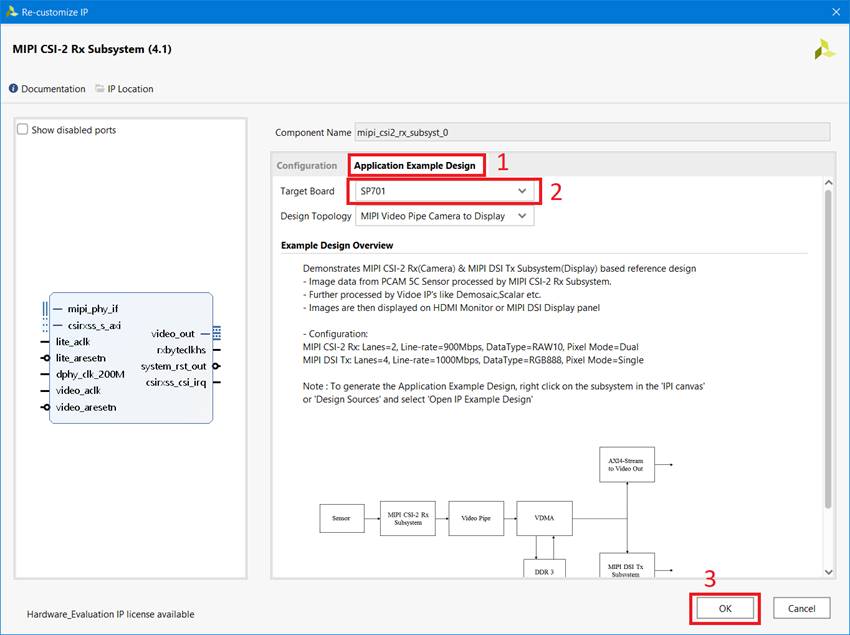

15. Klik kanan pada IP yang dibuat (1) :: Pilih “Customize Block” (2)

16. Buka tab "Aplikasi Contoh Desain" (1) :: Pilih "SP701" (2) :: Klik "OK" (3)

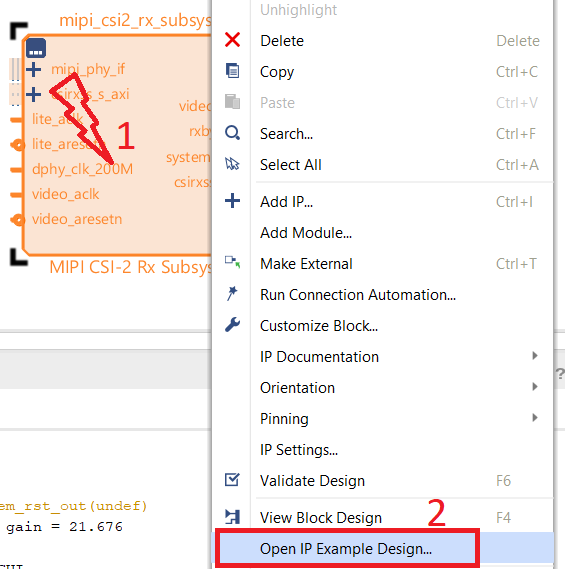

17. Klik kanan pada IP (1) :: Pilih “Open Example Design” (2)

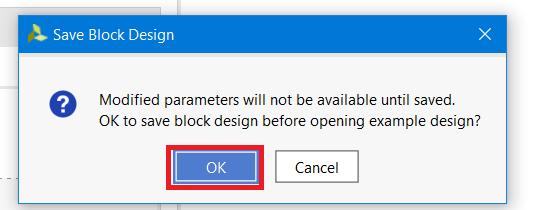

18. Klik "OK" untuk menyimpan perubahan proyek.

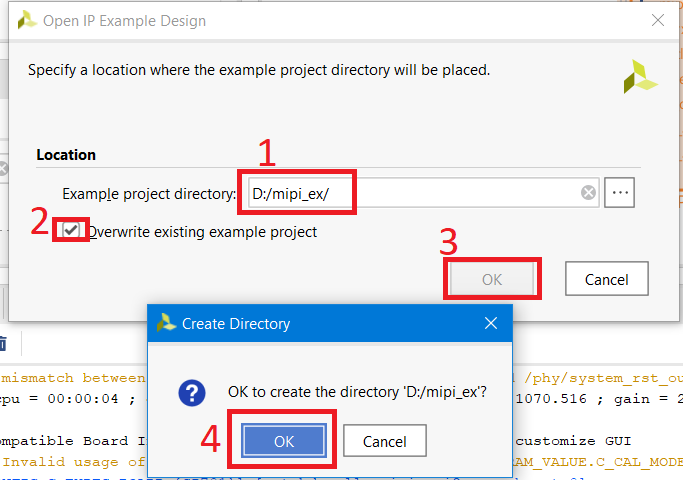

19. Tentukan direktori tempat proyek uji akan ditempatkan (Harap dicatat bahwa bagi pengguna Windows jalur ke folder harus sesingkat mungkin, jika jalur ke kernel IP internal proyek dapat melebihi 260 karakter, yang akan menyebabkan kesalahan saat membuat proyek) (1) :: Instal kotak centang (2) :: Klik “OK” (3) :: Klik “OK” (4)

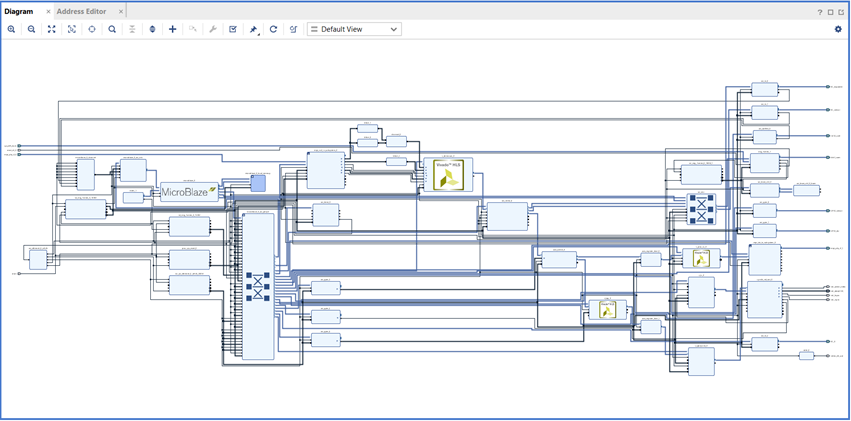

20. Proyek uji akan terbuka di jendela Vivado baru. Tunggu hingga pembuatan proyek. Ini akan memakan waktu beberapa menit.

21. Di jendela proyek uji, klik "Generate bitstream" (1) :: Klik "Ya" (2)

22. Pilih jumlah yang lebih disukai dari IP yang disintesis secara bersamaan (1) :: Klik “OK”

23. Tunggu hingga file firmware FPGA dibuat (bitstream)

Langkah 4: Pengaturan dan Koneksi

24. Hubungkan kamera PCAM-5C ke konektor MIPI CSI pada board SP701

25. Sambungkan monitor HDMI dan / atau tampilan MIPI ke SP701

26. Sambungkan kabel uUSB ke papan SP701

27. Nyalakan kekuatan SP701

28. Buka aplikasi terminal untuk port serial (misalnya, Tera Term). Karena tiga port COM yang berbeda diakui dalam Tera Term, kami membuka tiga sesi Term Tera yang berbeda. Kecepatan UART di mana pesan akan dialirkan memiliki kecepatan 9600 (periksa pengaturan Uartlite IP dalam proyek uji)

Luncurkan dan debugging

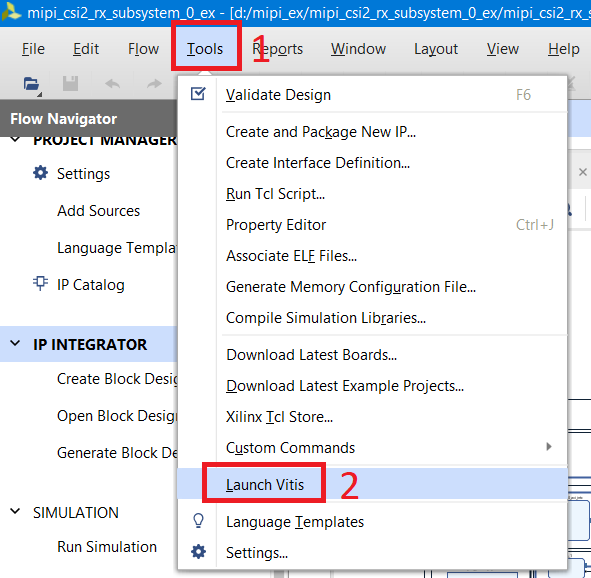

29. Luncurkan VITIS dari Vivado. Klik "Alat" (1) :: Klik "Luncurkan VITIS" (2)

30. Tentukan direktori kerja. Itu terletak di dalam direktori proyek uji “mipi_ex :: mipi_csi2_rx_subsystem_0_ex :: SW :: xmipi_app” (1) dalam kasus kami :: Klik “Luncurkan” (2)

31. Tutup tab "Selamat Datang" di VITIS

32. Sekarang kami memiliki akses ke komponen perangkat lunak proyek kami, yaitu program untuk prosesor perangkat lunak MicroBlaze. Periksa kodenya jika Anda mau.

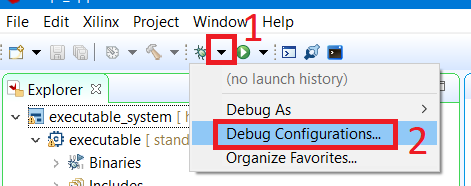

33. Klik panah di sebelah ikon bug (1) :: Klik “Debug Configurations” (2)

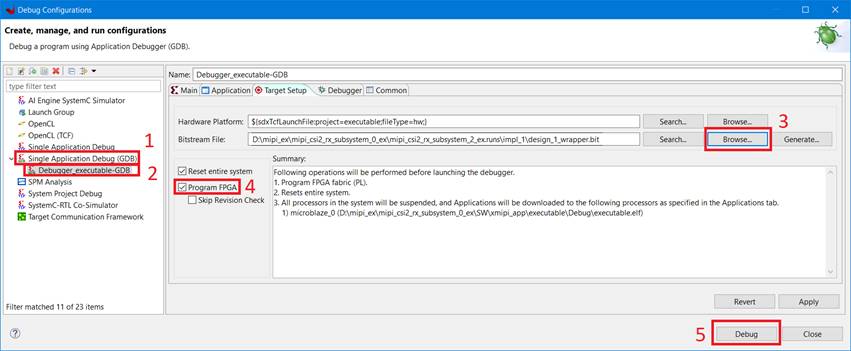

34. Klik dua kali pada "Debugger Aplikasi Tunggal (GDB)" (1) :: Pilih "Debugger Eksekusi" (2) :: Tentukan file firmware FPGA (.bit) yang dibuat oleh Vivado (3) :: Instal kotak centang (4): : Klik "Debug" (5)

35. Tekan tombol mulai dan ikuti instruksi yang muncul di terminal Tera Term

36. Itu saja (jangan lupa melepas tutup pelindung dari kamera;)

Kesimpulan

Seperti yang telah kita lihat, membuat proyek uji dengan antarmuka MIPI cukup sederhana. Hanya butuh VITIS / Vivado dan ketersediaan perangkat keras yang sesuai (papan dan kamera). Hampir semua inti IP dari Xilinx memiliki kemampuan untuk menghasilkan proyek pengujian dan dalam artikel ini kami menunjukkan cara melakukan ini.