Minggu ini, Intel berbagi rencana jangka panjangnya untuk pengenalan proses manufaktur baru. Sekitar tahun 2029, Intel

bermaksud untuk memperkenalkan teknologi proses dengan standar 1,4 nm. Setelah 10 tahun, tim manajemen perusahaan tidak mungkin sama dengan hari ini. Jadi rencana-rencana ini secara halus mengingatkan pada perumpamaan Khoja Nasreddin tentang keledai, khan, dan guru hewan yang membaca dengan baik dalam pribadi Khoja sendiri. Menjelang siang, terdakwa mungkin tidak ada di sana. Tapi ini bukan tentang itu. Direncanakan, maka kami menerima sebagai panduan untuk bertindak.

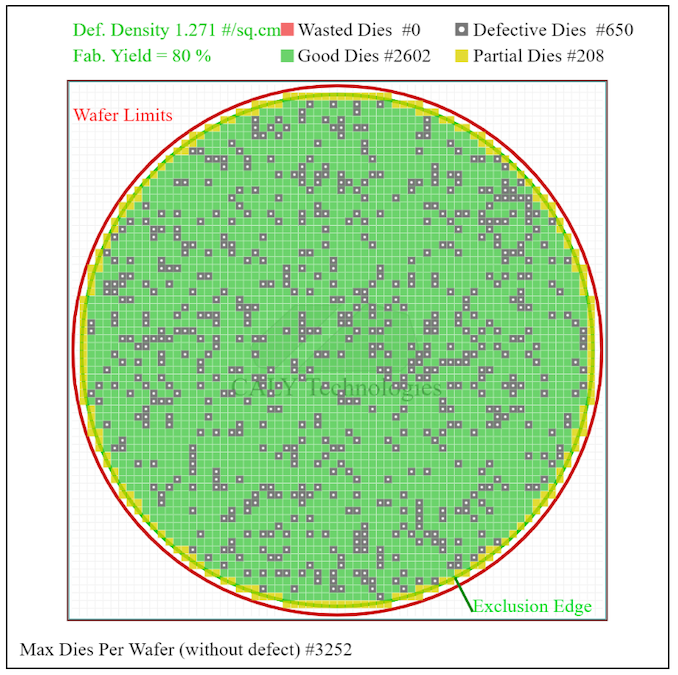

Di kamp produsen semikonduktor terkemuka, ada sedikit kejelasan, yang dikonfirmasi oleh produksi berisiko chip TSMC dengan standar 5 nm (

hari ini , tingkat cacat hanya 20% pada tingkat 3-8% untuk kristal dengan luas 17,92 mm

2 , untuk chiplet AMD Zen 2 akan memiliki tingkat penolakan yang lebih tinggi - hingga 60%). Namun, sebelum rilis prosesor AMD dengan standar 5 nm, setidaknya satu setengah tahun lagi akan berlalu.

/ gambar dari situs web AnandTech

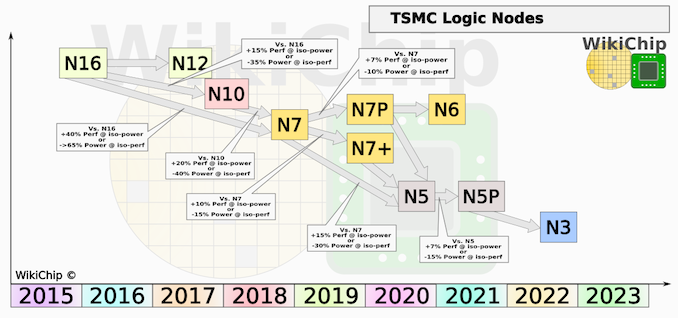

/ gambar dari situs web AnandTechTahun depan, mulai kuartal kedua, teknologi proses TSMC dengan standar 5 nm akan digunakan untuk produksi serial SoC pada core ARM. Pada 2022, TSMC jelas akan memulai produksi berisiko chip 3-nm (apa pun nanometer ini), dan dalam beberapa tahun, perusahaan berjanji untuk memulai produksi solusi 2-nm. Itu akan terjadi pada 2024-2025, atau dua atau tiga tahun lebih awal dari Intel akan memperkenalkan teknologi proses yang sama.

Untuk Samsung, proses dengan standar 5 nm dan 4 nm akan menjadi

evolusi dari teknologi proses 7-nm, yang akan diekspresikan dalam pengurangan bertahap kecil dalam langkah-langkah metalisasi di bawah elemen FinFET seperti saluran dan gerbang. Secara umum, struktur transistor (jumlah tepi) akan tetap sama karena struktur sel SRAM tidak akan berubah. Samsung akan memulai produksi chip menggunakan teknologi proses 4-nm di bidang 2021. Pada tahun yang sama, perusahaan berjanji untuk memulai produksi berisiko menggunakan teknologi proses 3-nm. Dan beberapa sumber Korea Selatan

mengklaim bahwa ini bisa terjadi pada tahun 2020, yang tampaknya tidak mungkin.

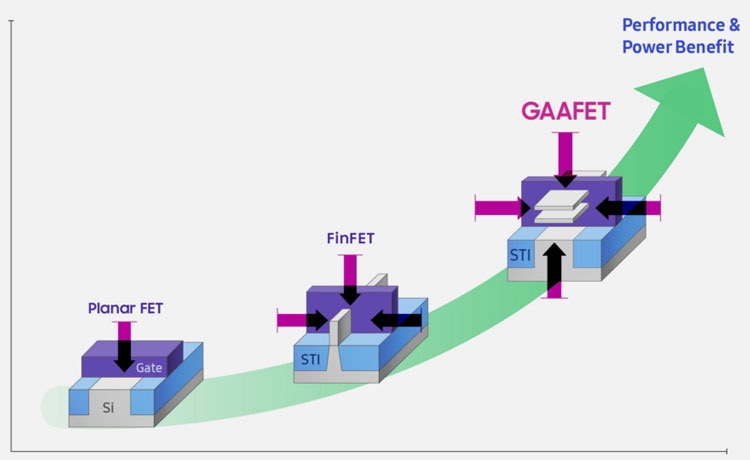

Pada artikel ini, kami tertarik pada fakta bahwa, hingga teknologi proses 4-nm, Samsung dan, jelas, Intel dan TSMC akan menggunakan transistor FinFET - sirip gerbang tinggi, yang di dalamnya saluran vertikal memotong dan menembus. Dalam transistor seperti itu, medan elektromagnetik gerbang menembus saluran dari tiga sisi, dan dua atau tiga saluran di masing-masing transistor secara total menyediakan arus yang diperlukan agar katup dapat beroperasi.

/ Gambar Samsung

/ Gambar SamsungDimulai dengan teknologi proses 3nm, Samsung akan menghentikan praktik ini. Konsep FinFET akan berhenti bekerja seperti sebelumnya. Gerbang transistor FinFET akan terlalu kecil dan tidak akan dapat berganti transistor. Kebutuhan untuk mengurangi tegangan suplai dari transistor hanya akan memperburuk situasi ini. Oleh karena itu, untuk teknologi proses 3-nm, sebuah transistor dengan cincin GAA (Gerbang-All-Around) akan

diperkenalkan .

/ Gambar Samsung

/ Gambar SamsungSamsung memberi transistor baru nama komersial MBCFET (Multi Bridge Channel FET). Dalam praktiknya, ini adalah pengembangan ide transistor, yang

dibuat bersama oleh para peneliti dari IBM, Samsung dan GlobalFoundries. Diasumsikan bahwa transistor yang serupa dalam struktur akan terlibat dalam transisi ke teknologi proses dengan standar 5 nm. Namun pada kenyataannya, struktur katup ini akan muncul dalam chip hanya dengan awal produksi 3nm Samsung. Transistor MBCFET akan terdiri dari saluran yang disusun secara horizontal di atas satu sama lain dalam bentuk nanopages, bukan punggung vertikal, seperti pada FinFET. Karakteristik transistor MBCFET akan mudah dikendalikan baik dengan memvariasikan jumlah halaman yang terletak satu di atas yang lain, dan dengan mengubah lebar halaman. Setiap halaman adalah saluran. Jumlah variabel-variabel ini akan menentukan transistor yang kita miliki: kuat dan cepat, atau lemah, tetapi daya rendah. Akan ada lebih dari dua gradasi - dari lima menjadi tujuh.

/ Gambar Samsung

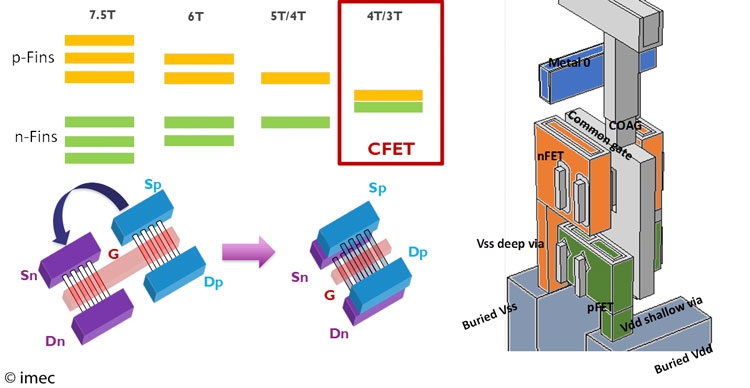

/ Gambar SamsungHal yang paling menarik, untuk kepentingan catatan ini dikandung, bahwa transistor MBCFET hanya dapat muncul dalam kerangka kerja teknologi proses 3-nm, dan teknologi proses dengan standar 2 nm lagi akan memerlukan perubahan dalam struktur transistor. Transistor baru dengan nama Forksheet diusulkan oleh pusat penelitian Belgia Imec. Untuk pertama kalinya, perwakilan Imec

berbicara secara rinci tentang struktur transistor dengan halaman terpisah (nano) musim semi ini di acara tahunan. Tapi Anda tidak bisa memberi makan burung bulbul dengan dongeng. Kami akan merasakannya. Anda belum bisa merasakannya, tetapi Belgia melakukan simulasi transistor Forksheet pada TCAD, yang

dilaporkan tiga hari lalu.

Sebelum mempertimbangkan data, kami menjelaskan bahwa transistor Forksheet adalah modifikasi dari transistor dengan nanopages - MBCFET atau Gate-All-Around yang sama, jika kita mengabaikan istilah Samsung. Sirip rana vertikal dalam transistor Forksheet sedikit lebih lebar daripada MBCFET, tetapi nanopage dari saluran transistor terbelah dua dan dipisahkan oleh lapisan dielektrik. Faktanya, satu transistor MBCFET dengan gerakan pergelangan tangan berubah menjadi sepasang transistor pelengkap dari transistor tipe-p dan n.

Struktur yang diusulkan menghancurkan penghalang serius dalam penyegelan transistor dalam bentuk kompleksitas untuk membawa p- dan n-transistor sedekat mungkin dan pada saat yang sama menghindari pengaruh negatif timbal balik dari gerbang.

Jelas, pendekatan yang diusulkan akan meningkatkan kepadatan transistor pada chip, tetapi pemodelan telah menunjukkan bahwa kinerja dan konsumsi daya juga akan meningkat. Beralih ke transistor dengan halaman terpisah akan mengurangi area kristal hingga 20%, dan dengan mengurangi kapasitansi palsu dan kebocoran, kinerja perangkat elektronik akan meningkat hingga 10%. Jika Anda tidak menambah frekuensi, maka Anda dapat mengurangi konsumsi daya hingga 24%.

Dalam stok, Imec memiliki

teknologi lain yang dapat lebih meningkatkan kepadatan transistor. Ini dapat diterapkan baik pada tahap produksi chip 3-nm, dan dengan standar produksi yang lebih rendah. Idenya adalah untuk membuat pasangan pelengkap transistor di atas satu sama lain. Operasi yang tampaknya sederhana ini berjanji untuk mengurangi ukuran sel logis standar dan sel SRAM sebesar 50%. Dikembangkan dengan baik dan diuji sebagian pada gagasan model, berakhir di sini.

Beralih ke teknologi proses 1-nm juga mungkin memerlukan struktur transistor baru. Pada saat yang sama, harus diingat bahwa para insinyur sering merasa mungkin untuk meluaskan kesenangan mereka - untuk menghasilkan sesuatu seperti itu untuk mengambil langkah maju dengan menggunakan kruk tua.