Sebuah artikel dari situs insinyur rumah gila Chris Fenton

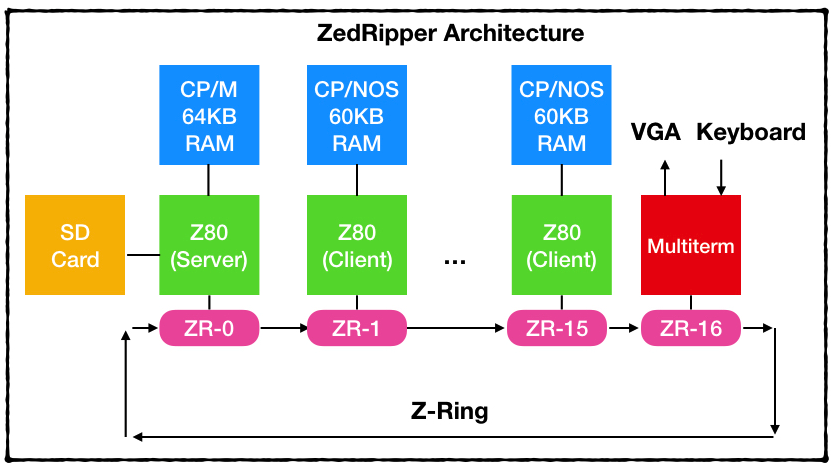

Temui ZedRipper, binatang 16-core yang berjalan pada 83 MHz yang ditenagai oleh prosesor Z80, sangat portabel dan tidak praktis. Ini adalah upaya saya yang terbaru untuk merakit komputer untuk bersenang-senang, dan telah memenuhi beberapa keinginan sekaligus:

- Akhirnya, gunakan FPGA raksasa, yang sedang berbaring bersamaku.

- Mainkan sejarah alternatif dalam menciptakan komputer, mendekati masalah multitasking dari perspektif besi.

- Siapkan komputer tempat saya bisa menulis program pendek yang lucu dalam perjalanan bekerja di kereta.

- Merakit platform tempat eksperimen yang relatif sederhana dengan arsitektur komputer dapat dilakukan.

Foto yang glamor

Jika Anda tidak punya waktu untuk membaca selembar teks tentang arsitektur komputer yang tidak praktis ...

Jadi, binatang apa ini?

ZedRipper adalah hasil dari upaya untuk membangun komputer paling keren dengan CP / M 2.2:

- 16 prosesor Z80 beroperasi pada frekuensi 83,33 MHz.

- Memori khusus 64 KB untuk masing-masing Z80.

- Akselerator terminal yang kompatibel dengan ANSI dengan 16 output.

- Semua prosesor dan perangkat terhubung oleh jaringan cincin searah yang sepenuhnya sinkron yang beroperasi pada 83 MHz.

- 128 MB drive pada kartu SD (16 x 8 MB drive dalam CP / M).

- Kernel “server” yang melakukan booting ke CP / M 2.2 dan menjalankan server file CP / NET (ditulis dalam Turbo Pascal 3 di komputer itu sendiri!), Yang menyediakan akses bersama ke kartu SD.

- 15 kernel "client" meluncurkan CP / NOS dari ROM. Setiap klien memiliki akses ke repositori umum, dan semua orang dapat menjalankan program CP / M 2.2 tanpa bersaing untuk sumber daya dengan kernel lain.

Jalan lain

Apakah catur dan Planetfall yang mengalihkan perhatian saya dari editor Turbo Pascal saya?

Apakah catur dan Planetfall yang mengalihkan perhatian saya dari editor Turbo Pascal saya?Setelah petualangan saya dengan

porting game ke Kaypro , saya memiliki kesan yang sangat hangat tentang sistem operasi primitif ini 40 tahun yang lalu, dan saya memiliki ide yang saya putuskan untuk dikembangkan: bagaimana jika cerita berubah ke arah yang berlawanan, dan PC akan melanjutkan jalur pengembangan dengan beberapa CPU segera? Bahkan pada 1980-an, prosesor itu sendiri (dan segera RAM) relatif murah, tetapi multitasking PC semata-mata didasarkan pada pemotongan waktu ketika satu sumber daya besar (RAM atau CPU) dibagi antara program yang bersaing. Iron tidak bisa mengatasi ini (dan sangat sulit untuk mendapatkan program untuk berperilaku baik pada OS seperti DOS) sampai kami pindah ke era 386 dan komputer dengan lebih dari 4 MB memori.

Selama hobi sejarah saya dengan komputer, saya menemukan sesuatu yang sangat menarik bagi saya: pada tahap awal pengembangan,

CP / M OS mendukung versi "jaringan" yang disebut CP / NET. Sebagian besar orang masih tahu idenya hari ini - untuk menempatkan di kantor satu atau dua mesin "nyata" dengan drive dan printer besar, yang sumber dayanya akan dibagi antara klien tipis, terminal dengan CPU dan RAM. Setiap pengguna akan bekerja seolah-olah dia memiliki mesin sendiri yang menjalankan CP / M dengan akses ke disk besar dan printer.

Seperti yang saya sebutkan, CPU dan RAM (biasanya Z80 memiliki 64 KB DRAM) tidak terlalu mahal, tetapi semua pribluds eksternal yang diperlukan untuk membuat komputer yang berguna (drive, printer, monitor, ..) ditambahkan hingga total biaya. Pada saat itu, menambahkan banyak CPU / RAM ke komputer tampaknya merupakan pendekatan yang agak dekaden untuk menyediakan satu pengguna dengan banyak CPU dan RAM. Bahkan CP / M telah membagi cara lamanya waktu untuk MP / M OS.

Saya menemukan bahwa Exidy datang paling dekat dengan ini - pada tahun 1981 mereka merilis mesin Multi-NET 80 mereka, yang memungkinkan menambahkan hingga 16 kartu, yang masing-masing memiliki Z80 dan RAM. Namun, itu dirancang untuk bekerja hingga 16 pengguna individu, dan bukan untuk pekerjaan satu pengguna yang secara bersamaan meluncurkan 16 program.

Sangat dekat ...

Sangat dekat ...Maju cepat 40 tahun - transistor benar-benar jatuh harga. Setelah penutupan laboratorium, saya mewarisi beberapa FPGA mengerikan (Stratix IV 530GX), dan saya pikir itu akan sangat menarik untuk dilakukan dengan salah satunya. Pada titik tertentu, saya menemukan proyek yang sangat menarik oleh Grant Searle

Multi-Comp , dan cukup mudah untuk merakit mesin yang bekerja dengan CP / M dan satu CPU. Tetapi saya membutuhkan lebih banyak. Saya memutuskan untuk melihat apakah saya dapat membuat mesin multi-core pada CP / M dengan multitasking nyata - tidak ada yang rumit, hanya kekuatan kasar.

Kami mengkonfigurasi dan meluncurkan perangkat lunak

Dalam proyek ini, saya terutama berkonsentrasi pada perangkat keras, dan tidak menulis satu baris kode pun di assembler. CPU 0 memuat langsung dari ROM, yang saya ambil dari Grant, dan simpul yang tersisa diambil dari ROM 4KB CP / NOS, yang saya ambil dari simulator Atari.

Kedua ROM menunggu koneksi ke terminal serial melalui antarmuka standar, sementara klien CP / NOS mengharapkan port serial lain yang terhubung ke server. Sangat mudah untuk merancang logika Anda sendiri pada FPGA besar. Saya mengembangkan logika penguraian alamat saya, berkat cincin Z untuk setiap CPU yang muncul dalam skema pemetaan alamat bila perlu.

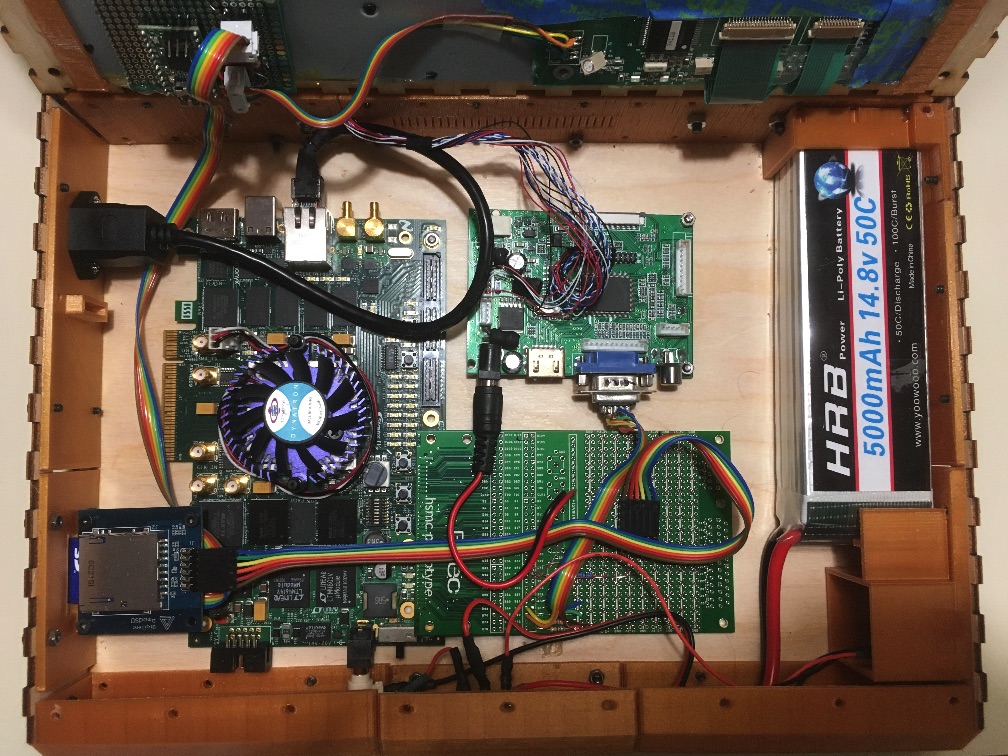

Bagian dalam

Jantung ZedRipper adalah salah satu dari FPGA Stratix IV 530GX yang sangat besar ini. Kartu HSMC digunakan untuk tampilan, menerima data dari pengontrol keyboard dan menghubungkan ke kartu SD. Ethernet digunakan untuk mengunduh firmware, jadi ada port seperti di samping case, bersama dengan adaptor kartu SD dan slot untuk port serial eksternal (belum digunakan).

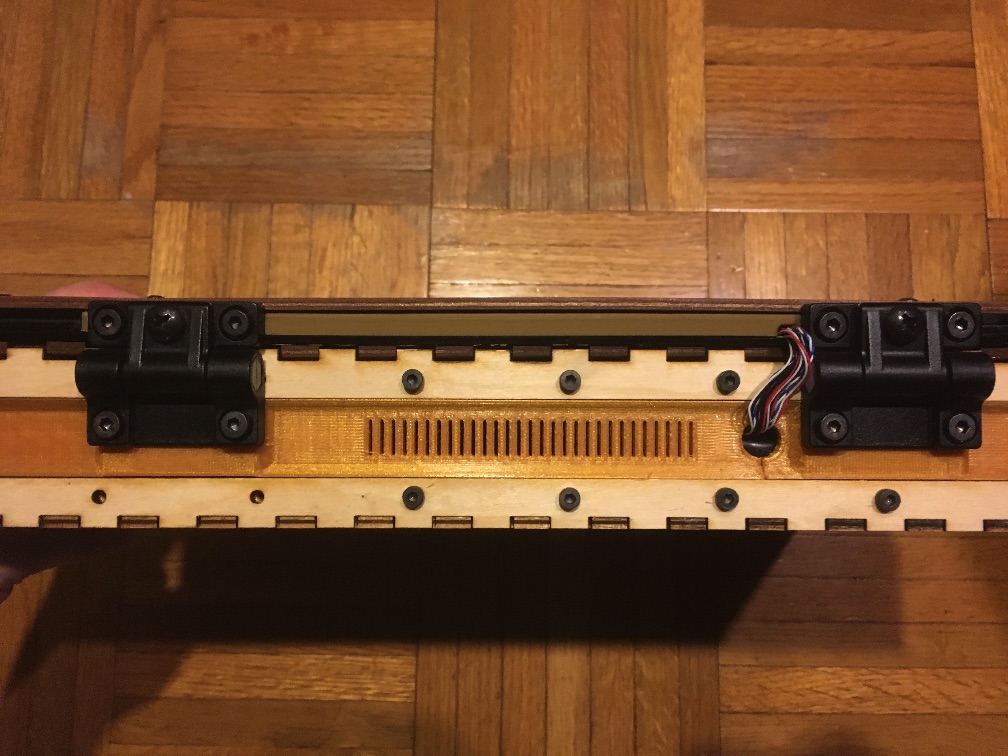

Keyboard dan pengontrol

Keyboard dan lubang di latar depan, di mana perangkat penentuan posisi akan dipasang nanti

Keyboard dan lubang di latar depan, di mana perangkat penentuan posisi akan dipasang nantiSaya memiliki keyboard PS / 2 yang ringkas tergeletak (dari salah satu proyek lama saya dengan laptop), dan saya ingin menghubungkannya ke I / O 2,5 V dari FPGA saya. Saya memutuskan untuk pergi dengan cara mudah, dan menambahkan mikrokontroler Teensy 2.0 ke bundel.

Kontroler lem panas di bagian bawah keyboard

Kontroler lem panas di bagian bawah keyboardIni memungkinkan untuk menerjemahkan PS / 2 ke ASCII, serta dengan mudah menandai beberapa kunci tambahan (F1-F12) menjadi urutan "ajaib" dari perintah terminal, untuk menambah kenyamanan. Pengontrol kemudian menyediakan Z80 byte untuk UART pada 9600 baud (menggunakan pembagi tegangan sederhana yang mengubah 5 V hingga 2,5 V untuk FPGA). Mengingat bahwa proyek ini dikumpulkan dari berbagai sampah di bengkel saya, itu adalah solusi yang nyaman yang menunjukkan dirinya dengan baik dalam pekerjaan.

Tampilan

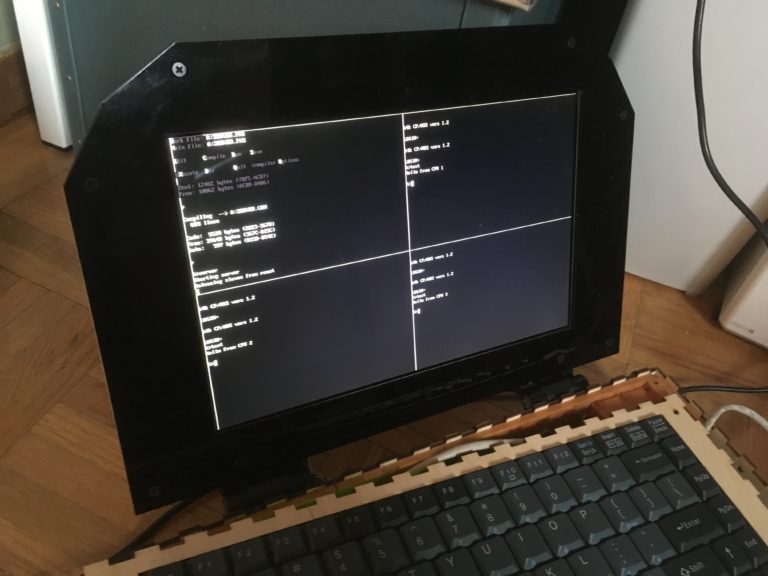

Layar memuat, server berjalan di sudut kiri atas, dan tiga program pengguna yang berbeda bekerja pada kernel yang terpisah

Layar memuat, server berjalan di sudut kiri atas, dan tiga program pengguna yang berbeda bekerja pada kernel yang terpisahFitur Tampilan: 1280 × 800 10.1 ″, dan ia mengerti VGA. FPGA menggunakan jaringan resistor sederhana untuk menghasilkan hingga 64 warna (R2G2B2). Layar memerlukan pengatur waktu 83,33 MHz (1280 × 800 @ 60Hz), sehingga untuk kesederhanaan seluruh rangkaian beroperasi pada frekuensi ini.

Proyek Grant, Multicomp, memiliki kode VHDL untuk terminal sederhana yang kompatibel dengan ANSI. Saya menulis ulang logikanya pada Verilog, dan kemudian mengembangkan pengontrol video dengan dukungan untuk 16 terminal independen yang terhubung melalui satu simpul Z-Ring. Layar 1280 × 800 dianggap sebagai tampilan 160x50 karakter (dengan font 8x16), dan setiap terminal berfungsi sebagai "sprite" 80x25 yang dapat dipindahkan di mana saja di layar (dengan daftar prioritas yang menyesuaikan urutan render terminal). Karena setiap terminal beroperasi secara independen dari yang lain, ia memiliki mesin negara sendiri, dengan 2 KB RAM untuk karakter dan 2 KB "atribut" (untuk menyimpan informasi warna). Setiap karakter mendukung latar belakang 4-bit dan warna karakter. Karena semua terminal harus memiliki karakter lekukan yang sama, dan sel 8x16 hanya dapat berisi satu karakter, semua terminal dapat menggunakan 2 KB ROM yang sama yang berisi font. Secara umum, logika tampilan menggunakan sekitar 66 KB RAM blok.

Secara umum, saya mendapatkan window manager yang sangat sederhana untuk terminal CP / M saya, yang bekerja hampir sepenuhnya karena perangkat keras. Ini adalah salah satu area terkaya untuk penelitian - sejauh ini, hanya CPU server yang dapat mengatur ulang terminal, tetapi saya memiliki rencana yang luas untuk menambahkan perangkat penentuan posisi seperti mouse, yang memungkinkan menggunakan perangkat keras windows hanya untuk menarik jendela dan mengubah prioritas tampilan.

Karena pengontrol terminal hanyalah salah satu dari simpul Z-Ring (dan mengarahkan ulang antarmuka ini ke salah satu Z80 sangat sederhana), di antara rencana masa depan adalah mungkin untuk menambahkan terminal "layar penuh" 160x50 (mungkin sebagai "latar belakang"), dan tampilan nyata 1280x800x64 warna dengan SRAM eksternal cepat di papan tulis.

Cincin-Z

Bagaimana cara mengumpulkan sekelompok Z80? Di pekerjaan saya, saya dengan tegas belajar satu hal: mengembangkan jaringan itu sulit. Tujuan keseluruhan dari jaringan ini adalah:

- Implementasi sederhana.

- Antarmuka yang sederhana

- Ekstensibilitas yang sewenang-wenang.

- Performa yang memadai.

Seperti yang sudah saya sebutkan, Z80s saya berharap untuk terhubung ke port serial, jadi antarmuka itu cukup sederhana untuk dilakukan - itu harus disamarkan sebagai port serial! Pada dasarnya, Z-Ring adalah jaringan cincin sinkron, searah yang menggunakan "kredit" untuk mengontrol aliran. Setiap node memiliki buffer masuk 1-byte untuk masing-masing node lain dalam jaringan. Setelah reset, setiap node memiliki 1 "kredit" untuk masing-masing node jaringan yang tersisa. Skema ini diparameterisasi, oleh karena itu mudah untuk diukur ke ratusan node dengan penambahan jumlah logika yang sangat kecil, namun hari ini Z-Ring mendukung hingga 32 node (oleh karena itu, setiap node membutuhkan buffer 32-byte).

"Bus" itu sendiri terdiri dari bit validitas, ID "sumber", ID "target", dan payload 1-byte (19 bit). Saya pikir itu akan sangat sederhana untuk diimplementasikan menggunakan logika TTL (jika seseorang gagal pada tahun 1981 dan tidak dapat menemukan FPGA). Setiap "simpul" memiliki 2 jalur pipa untuk pemicu bus - 0 dan 1 tahap - dan ketika Anda memasukkan pesan, ia menunggu sampai tahap 0 kosong, dan kemudian bergabung ke dalam 1. Pesan dimasukkan pada simpul sumber dan berjalan di sekitar cincin sampai mencapai target, setelah itu mereka menemukan diri mereka dalam buffer yang sesuai dan memperbarui bendera kesiapan data. Ketika node penerima membaca buffer, itu memasuki kembali pesan asli, yang terus melakukan perjalanan di sekitar cincin sampai mencapai sumber lagi, mengembalikan "kredit". Jika Anda mengirim paket ke alamat yang tidak ada, pinjaman akan dikembalikan secara otomatis setelah lingkaran penuh.

Karena setiap pemberhentian pada ring terdiri dari dua tahap konveyor, dan tidak ada tekanan balik, setiap pesan tidak lebih dari 2 * (jumlah node) siklus pengiriman. Implementasi saat ini memiliki 17 node (16 CPU + display / keyboard controller), dan bekerja pada timer 12 ns, sehingga dibutuhkan sekitar 400 ns untuk mengirimkan pesan dan mengembalikan pinjaman. Pengontrol layar dapat mengirimkan lalu lintas dengan tingkat kedatangan, sehingga setiap CPU memiliki bandwidth 2-2,5 Mb / s ke terminalnya (bus melewati cukup untuk menyediakan semua 16 CPU), yang cukup banyak untuk terminal.

Dalam konfigurasi saat ini, semuanya berfungsi dengan baik, tetapi Anda dapat membuat beberapa perbaikan yang jelas:

- Untuk memperdalam buffer penerima, yang akan meningkatkan throughput dari node - pada FPGA ada banyak blok gratis 1 KB RAM, yang akan mendukung 32 node dengan 32 kredit, sehingga setiap teori dalam teori dapat menjenuhkan bus.

- Tambahkan dukungan untuk mode alamat. Menambahkan alamat 16-bit (atau lebih) akan memungkinkan akses langsung ke memori (DMA) (dan menambahkan DMA ke setiap node akan mudah). FPGA memiliki sejumlah besar perangkat keras tambahan (beberapa megabyte RAM statis dan sekitar satu gigabyte DDR3).

- Tambahkan flow control (dan buffering) antar node.

Tetapi semua ini bisa menunggu sampai waktu yang lebih baik.

Nutrisi!

Papan debugging dengan FPGA membutuhkan daya input 12-20 V, layar membutuhkan 12 V, dan keyboard dan pengontrol membutuhkan 5 V. Lebih nyaman jika FPGA memiliki pengontrol 3,3, 5 dan 12 V, yang cukup mudah dihubungkan, jadi FPGA menerima daya langsung dari baterai lithium-polimer pada 5.000 mAh dengan tegangan 14,4 V, dan kemudian mendistribusikan daya ke semua perangkat lain. Salah satu kesulitannya adalah saya tidak ingin membongkar laptop setiap kali untuk mengisi daya, tetapi baterai memiliki konektor daya + / - normal, serta konektor "penyeimbang" yang terhubung ke setiap sel individu. Solusi saya yang tidak sempurna adalah tombol daya mengalihkan koneksi baterai antara daya FPGA dan konektor pengisian daya yang terletak di ceruk ditutup oleh penutup geser. Sangat tidak nyaman, tetapi Anda cukup menggeser tutupnya dan mengeluarkan konektor dari sana untuk menghubungkannya ke muatan tanpa menggunakan tombol hex.

Pengisian terlihat aneh

Pengisian terlihat anehSaya belum menguji baterai dengan saksama, tetapi baterai bertahan setidaknya 3 jam (yang lebih dari cukup untuk menutupi perjalanan kereta saya). Kemungkinan besar, ini akan bertahan sekitar 6 jam tanpa optimasi konsumsi. Ini tidak mendukung penggunaan pada saat yang sama dengan pengisian daya, namun, laptop berjalan dengan daya baterai yang cukup lama sehingga ini tidak menjadi masalah.

Perumahan

Kasing dari desain "hacker" standar adalah kombinasi dari kayu lapis laser cutting 3 mm dan plastik yang dicetak pada printer 3D. Saya pegas engsel layar, jadi sebenarnya rasanya seperti laptop biasa, meskipun agak lambat. Saya ingin memberikan tampilan tahun 1980-an, sehingga sudut atas layar agak mirip Cray, dan dudukan kulit palsu dibuat di bawah pergelangan tangan. Tepi kayu lapis potong laser sangat tidak menyenangkan untuk tangan, jadi dudukan ini ternyata sangat fungsional.

Kecepatan

Saya belum mencoba satu tolok ukur khusus untuk CP / M (saya berasumsi mereka melakukannya, tapi saya tidak mencarinya secara khusus). Karena mesin ini dibuat untuk menulis program dalam Turbo Pascal, saya mencoba beberapa tes mikro untuk kecepatan. Ternyata operasi floating point 15-35 K per detik (menggunakan tipe Real 48-bit di TP), dan sekitar 1 juta operasi integer per detik (dengan tipe Integer 16-bit). Tidak buruk untuk CPU 8-bit dan lingkungan pemrograman yang cukup nyaman.

Proyek yang menarik untuk masa depan mungkin pengembangan akselerator untuk operasi floating point.

Pembuangan FPGA

Semua logika, seperti sudah saya katakan, agak ringan, dan hanya mengkonsumsi sekitar 7% dari sumber daya chip (meskipun 40% dari total blok RAM dan 100% dari RAM M144k).

- ALUT gabungan 31.808 / 424.960 (7%)

- Memory ALUT 0 / 212,480 (0%)

- Register logika khusus 10.231 / 424.960 (2%)

- Pemanfaatan logika 10%

- Total register 10231

- Total bit memori blok 9.005.056 / 21.233.664 (42%)

- Blok DSP elemen 18-bit 0 / 1.024 (0%)

Rencana masa depan

Dalam rencana langsung saya (yaitu, setrika sudah ada di bengkel, Anda hanya perlu mencari waktu untuk menyolder):

- Warnai semuanya. Laptop ini terbuat dari kayu lapis, dan saya benar-benar ingin menutupinya dengan sesuatu.

- Perangkat Pemosisian Joystick Hubungkan ke pengontrol keyboard.

- Pelacakan Baterai. ADC pada pengontrol keyboard membuatnya cukup mudah untuk melacak baterai, sehingga saya bisa mengerti pada level berapa daya terisi.

- WiFi - Saya memiliki ESP32 untuk meluncurkan Zimodem! Bersama dengan ponsel dalam mode titik akses, ini seharusnya memungkinkan saya untuk online saat bepergian. Ada aplikasi terminal yang bagus untuk CP / M, tetapi alangkah baiknya menulis sesuatu seperti klien IRC atau browser web sederhana. Akan lebih mudah menggunakan protokol transfer file Kermit ke komputer Linux modern.

- Port serial, dapat diakses dari luar, untuk menghubungkan ke komputer lain (konektor sudah dicetak untuk itu, hanya perlu disolder).

- LED menunjukkan status saat ini. Baginya, sudah ada lubang di depan - sekarang saya berencana untuk menghubungkannya ke sinyal akses ke kartu SD.

Dalam jangka panjang, saya menantikan berbagai ide besi, yang akan menyenangkan untuk bereksperimen dengan:

- Berapa banyak yang bisa Anda overclock pada Z80? Langkah pertama adalah melepaskan kecepatan prosesor dari pengatur waktu piksel, namun juga menarik untuk mencoba menerapkan teknik komputer modern ke Z80 (saluran pipa, penggantian nama register, prediktor transisi, dll.).

- Mungkin menarik untuk menambahkan akselerator khusus untuk hal-hal seperti operasi floating point. Ada 1024 blok DSP yang tidak digunakan pada chip, dan saya pikir tidak ada yang mencoba membangun akselerator untuk format Real 48-bit di TP.

- Gunakan besi yang ada! Saya masih memiliki banyak memori yang tidak digunakan, yaitu:

- 512 MB DDR3 SDRAM dengan bus data 64 bit

- 128 MB DDR3 SDRAM dengan bus data 16 bit

- Dua 4 MB QDR II + SRAM dengan bus data 18 bit

- 64 MB flash

- 2 MB SSRAM

- Tingkatkan videonya! Langkah pertama adalah menambahkan dukungan untuk terminal "layar penuh" 160x50, dan kemampuan untuk menskalakan terminal reguler 80x25 2 kali. Menggunakan SSRAM eksternal hanya akan menambah mode 1280 × 800 @ 6-bit.

- Perluas kapabilitas terminal saat ini. Saya pikir saya dapat menambahkan kompatibilitas dengan terminal seperti ADM-3A (dan menambahkan dukungan grafis), yang digunakan dalam Kaypro / 84, maka saya akan memiliki akses ke berbagai perangkat lunak yang lebih luas (dan saya tidak akan perlu port DD9).

Ringkasan

Sejauh ini, mobil telah bekerja hanya beberapa hari, tetapi saya dapat mengatakan bahwa saya sangat menyukai semuanya. Layarnya bagus dan jelas, keyboard-nya besar dan nyaman, bodinya tebal, tapi beratnya kecil (dan pas ke ransel).

Laptop itu ternyata sangat ergonomis untuk bekerja di kereta.Saya pikir saya berada di jalur yang benar. Kemampuan untuk membuka editor teks di satu jendela untuk membuat catatan saat men-debug kode pada TP di jendela lain sangat mudah (atau kemampuan untuk membuat catatan saat bermain Zork!). Dirasakan bahwa pendekatan seperti itu untuk menciptakan komputer multitask berbiaya rendah berdasarkan CP / M bisa ada.Ingin membangun yang sama?

Sejauh ini, saya tidak memiliki cara mudah untuk mendapatkan file dari mesin, sehingga bagian yang paling berguna dari perangkat lunak (server file CP / Net yang ditulis dalam Turbo Pascal) terjebak. Tetap bersama kami dan tetap disini (atau kirimi saya email jika Anda tidak bisa menunggu sama sekali). Pada titik tertentu, saya mungkin akan bergabung dengan abad ke-21 dan membuka akun di github. Sayangnya, semuanya bersandar pada "waktu senggang" itu.