Fotos, materiais e reviravoltas do seminário MIPSfpga no MEPhI

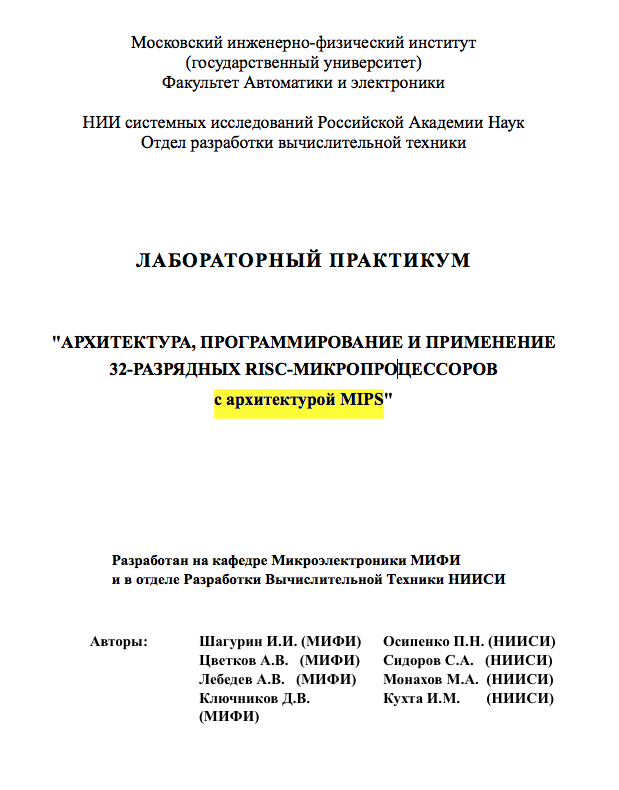

No final de outubro, foi realizado um seminário sobre o MIPSfpga no MEPhI - um de uma série de seminários organizados por universidades russas, juntamente com a Imagination Technologies, Microchip Technology em parceria com a Gamma St. Petersburg, representantes do Macro Group, Xilinx na Rússia, com a participação de palestrantes da MathWorks e NIISI. Abaixo está uma mistura de fotografias, links para materiais, notas sobre a preparação do seminário e cultura mítica. Abaixo está uma foto do MEPhI do lado de fora. A palavra "nuclear" lembra que existe um reator nuclear no Instituto de Física de Engenharia de Moscou, por isso é difícil chegar lá, especialmente com um passaporte americano - recebi um passe por duas semanas e o reitor assinou a ordem do seminário. Na entrada há um artilheiro com Kalashnikov (!) (Não me foi permitido fotografar o artilheiro ) Aqui estou (Yuri Panchul) com outros organizadores do seminário - Igor Ivanovich Shagurin e Maxim Gorbunov: Igor Ivanovich Shagurin, vice. Chefe do Departamento de Micro e Nanoeletrônica - autor de livros e artigos sobre microprocessadores Intel, Motorola e PowerPC, trabalho de laboratório no MIPS . UPD: Esclarecimentos de um camarada do NIIIS:

(Não me foi permitido fotografar o artilheiro ) Aqui estou (Yuri Panchul) com outros organizadores do seminário - Igor Ivanovich Shagurin e Maxim Gorbunov: Igor Ivanovich Shagurin, vice. Chefe do Departamento de Micro e Nanoeletrônica - autor de livros e artigos sobre microprocessadores Intel, Motorola e PowerPC, trabalho de laboratório no MIPS . UPD: Esclarecimentos de um camarada do NIIIS:

«, -32 -64 MIPS- — ( :) ). , — MIPS- . RISC , . MIPS-I. , , MIPS- , . , „ MIPS“ MIPS- . „

Curiosamente, Igor Ivanovich Shagurin foi representar a eletrônica soviética em uma conferência em San Francisco nos anos 70, quando a URSS era um país bastante isolado. Os participantes da conferência VLSI na década de 1970 foram levados para Muir Woods, a área com as sequóias mais altas do planeta. Sequoia sempervirens Maxim Gorbunov , pesquisador do NIISI / SRISA , um instituto envolvido no desenvolvimento de microprocessadores russos com arquitetura MIPS - COMDIV-32 e COMISSÃO 64. A Maxim é especialista no design da topologia de VLSI resistente à radiação e foi co-presidente de uma das seções da conferência internacional RADECS em Moscou:

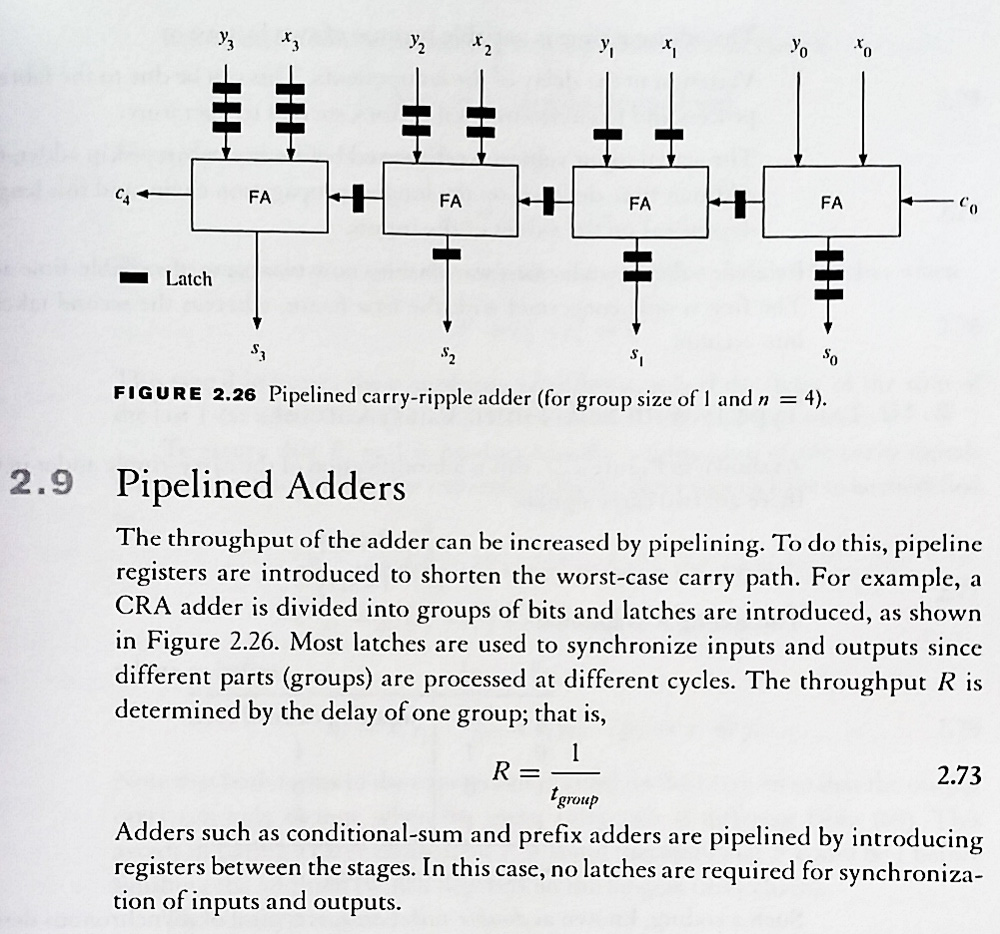

Antes do seminário do MIPSfpga na MEPhI, um dos instrutores, Yegor Kuzmin, começou a me perguntar sobre as condições da corrida em um determinado esquema de computação especializada que surgiu como um projeto do aluno. Não sei se entendi direito, mas expressei que, em um design síncrono devidamente organizado, esses problemas não surgem e prometem enviar como exemplo a fotografia de uma página do livro "Aritmética digital", que entende a organização do somador de pipeline, que contém uma pequena quantidade de lógica combinatória (a mesma que no somador com transporte sequencial), mas ao mesmo tempo coloca os registros (D-flip-flops) de forma que o somador possa iniciar uma nova operação de adição a cada ciclo do relógio, com uma frequência sinal de relógio, determinado pelo atraso de um somador combinatório completo de um bit:Digital Arithmetic 1st Edition por Milos D. Ercegovac e Tomás Lang Ao mesmo tempo, fotografei algumas páginas sobre circuitos assíncronos autotemporais, também relacionados ao problema .

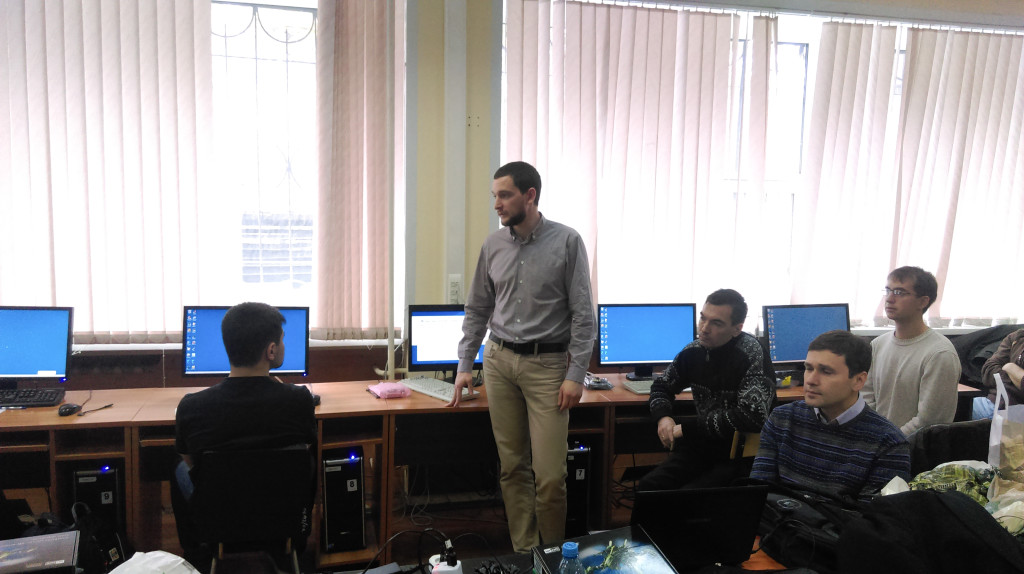

Antes do seminário do MIPSfpga na MEPhI, um dos instrutores, Yegor Kuzmin, começou a me perguntar sobre as condições da corrida em um determinado esquema de computação especializada que surgiu como um projeto do aluno. Não sei se entendi direito, mas expressei que, em um design síncrono devidamente organizado, esses problemas não surgem e prometem enviar como exemplo a fotografia de uma página do livro "Aritmética digital", que entende a organização do somador de pipeline, que contém uma pequena quantidade de lógica combinatória (a mesma que no somador com transporte sequencial), mas ao mesmo tempo coloca os registros (D-flip-flops) de forma que o somador possa iniciar uma nova operação de adição a cada ciclo do relógio, com uma frequência sinal de relógio, determinado pelo atraso de um somador combinatório completo de um bit:Digital Arithmetic 1st Edition por Milos D. Ercegovac e Tomás Lang Ao mesmo tempo, fotografei algumas páginas sobre circuitos assíncronos autotemporais, também relacionados ao problema . Fui apresentado a Vladimir Dementiev, que, juntamente com Andrei Andrianov, Dmitry Kozlovsky, ministra aulas de laboratório no MEPhI para programar microcontroladores Microchip PIC32MX. Eu disse a Vladimir que o professor Alex Dean da Universidade da Carolina do Norte colaborou com Imagination, Microchip e Digilent e agora está desenvolvendo um novo curso sobre programação de microcontroladores Microchip PIC32MZEste curso inclui RTOSs e a nova conexão de microcontroladores à nuvem. O microcontrolador PIC32MZ é baseado no núcleo do microprocessador MIPS microAptiv UP, o mesmo que o usado no MIPSfpga. Portanto, comecei a agitar os camaradas do MEPhI para participarem da revisão e (se quiserem) do teste beta deste curso: Mas voltando ao nosso seminário. O tópico do seminário foi MIPSfpga. O que é isso:

Fui apresentado a Vladimir Dementiev, que, juntamente com Andrei Andrianov, Dmitry Kozlovsky, ministra aulas de laboratório no MEPhI para programar microcontroladores Microchip PIC32MX. Eu disse a Vladimir que o professor Alex Dean da Universidade da Carolina do Norte colaborou com Imagination, Microchip e Digilent e agora está desenvolvendo um novo curso sobre programação de microcontroladores Microchip PIC32MZEste curso inclui RTOSs e a nova conexão de microcontroladores à nuvem. O microcontrolador PIC32MZ é baseado no núcleo do microprocessador MIPS microAptiv UP, o mesmo que o usado no MIPSfpga. Portanto, comecei a agitar os camaradas do MEPhI para participarem da revisão e (se quiserem) do teste beta deste curso: Mas voltando ao nosso seminário. O tópico do seminário foi MIPSfpga. O que é isso:

MIPSfpga — MIPS microAptiv UP. Microchip PIC32MZ, « » — Samsung Artik 1.

MIPS microAptiv UP 25 , Verilog, , .

MIPS microAptiv UP — MIPSfpga — : (), () Field Programmable Gate Array (FPGA).

Então, primeiro eu falei e falei sobre:1. Imagination Technologies e sua unidade de negócios MIPS2. Programas educacionais de Imagination Technologies3. Atualizar o conceito de fluxo RTL para GDSII para aqueles na platéia que não tinham Verilog / VHDL à especialização: como os blocos e sistemas IP em um chip (SoC) são projetados.4. Falei um pouco sobre as três linhas de núcleos de microprocessadores MIPS e em mais detalhes sobre a linha de núcleos de classe de microcontroladores, com base em um dos quais (MIPS microAptiv UP) o pacote MIPSfpga5. Foi criado um pacote para demonstrar ainda mais o cache do MIPSfpga 5. palavras e caches no MIPS microAptiv UP

Após meu primeiro discurso, Mikhail Peselnik, um orador do MathWorks fez um discurso: Mikhail Peselnik implementou um subconjunto de MIPS no Simulink , que recebeu uma espécie de prêmio editorial Escolha central da semana do MATLAB: O exemplo de Michael mostrou que para um aluno a arquitetura e a microarquitetura dos núcleos de processador podem ser estudadas de diferentes maneiras - pelo menos no Verilog e VHDL, pelo menos com a ajuda dos modelos C, pelo menos com a ajuda do Simulink. Porém, depois que os conceitos básicos de arquitetura e microarquitetura são estudados, o aluno deve experimentar um processador industrial, e aqui o MIPSfpga entra em cena, com o qual:

Após meu primeiro discurso, Mikhail Peselnik, um orador do MathWorks fez um discurso: Mikhail Peselnik implementou um subconjunto de MIPS no Simulink , que recebeu uma espécie de prêmio editorial Escolha central da semana do MATLAB: O exemplo de Michael mostrou que para um aluno a arquitetura e a microarquitetura dos núcleos de processador podem ser estudadas de diferentes maneiras - pelo menos no Verilog e VHDL, pelo menos com a ajuda dos modelos C, pelo menos com a ajuda do Simulink. Porém, depois que os conceitos básicos de arquitetura e microarquitetura são estudados, o aluno deve experimentar um processador industrial, e aqui o MIPSfpga entra em cena, com o qual:

- Os alunos podem criar seus próprios protótipos de sistemas em um chip, combinando um núcleo de microprocessador, memória e dispositivos de E / S projetados por eles

- , . « ».

- , , .

Mas, para experimentar os desenvolvimentos de SoC e com o kernel, eles precisam ter um bom comando da ferramenta / ferramenta de implementação. Portanto, depois que Mikhail Mikhail Filippov, engenheiro de aplicação do Macro Group, um representante oficial da Xilinx na Rússia, falou. A Xilinx é a empresa que inventou os FPGAs e, até hoje, continua sendo o número 1 nos FPGAs de alta velocidade.Alexander Filippov fez dois relatos:- Novos FPGAs da série 7 e MPSoC UltraScale - produtos XILINX para poderosos sistemas de chip programáveis

- XILINX VIVADO Design Environment para criação de sistemas em um chip

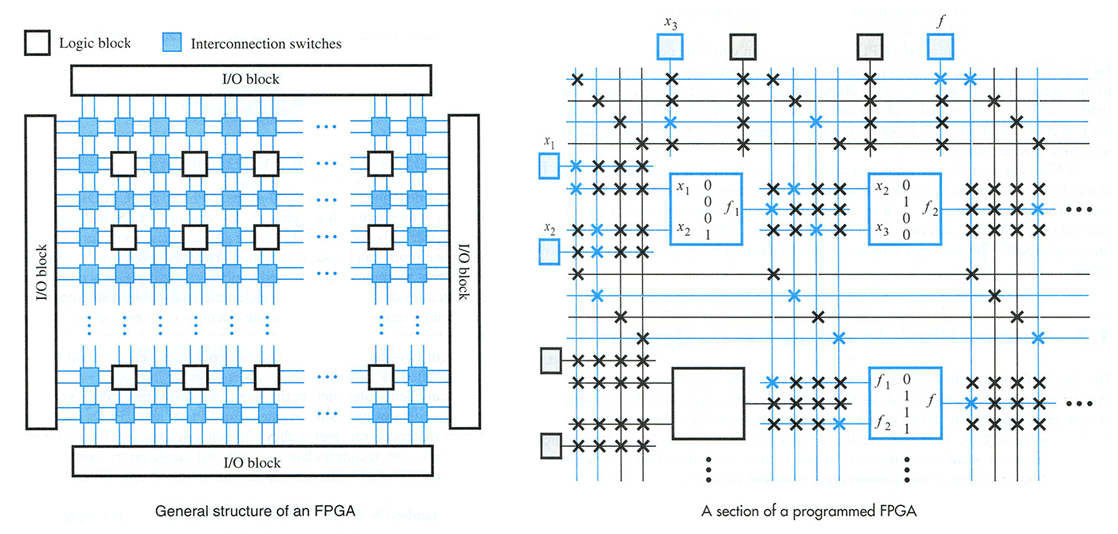

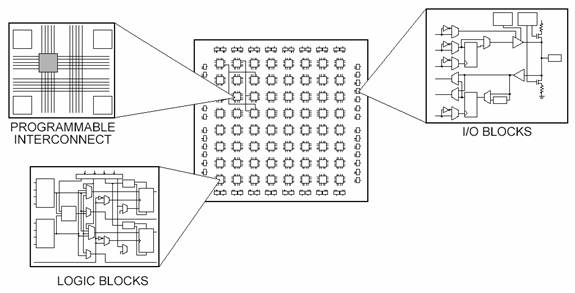

O que FPGA / FPGA expliquei nos dedos em outro post no Habr - Como começar a desenvolver ferro usando FPGAs - instruções passo a passo . Mas vamos repetir esta informação novamente:Na versão mais simples, o FPGA consiste em uma matriz de células homogêneas, cada uma das quais pode ser transformada em função usando multiplexadores conectados aos bits da memória de configuração. Uma célula pode se tornar uma porta AND com quatro entradas e uma saída, outra - um registro de bit único etc. Carregamos uma sequência de bits da memória na memória de configuração - e o circuito eletrônico fornecido é formado no FPGA, que pode ser um processador, controlador de exibição etc.FPGAs / FPGAs não são processadores; ao “programar” os FPGAs (preenchendo a memória de configuração dos FPGAs), você cria um circuito eletrônico (hardware), enquanto que ao programar um processador (hardware fixo), você insere uma cadeia de instruções seqüenciais de programa escritas nele (Programas).Abaixo está um diagrama da unidade FPGA mais simples, que inclui uma tabela de consulta (LUT) e flip-flop. É verdade que, nesse esquema, multiplexadores que alteram a função da célula e conexões com a memória de configuração não são mostrados.

O que FPGA / FPGA expliquei nos dedos em outro post no Habr - Como começar a desenvolver ferro usando FPGAs - instruções passo a passo . Mas vamos repetir esta informação novamente:Na versão mais simples, o FPGA consiste em uma matriz de células homogêneas, cada uma das quais pode ser transformada em função usando multiplexadores conectados aos bits da memória de configuração. Uma célula pode se tornar uma porta AND com quatro entradas e uma saída, outra - um registro de bit único etc. Carregamos uma sequência de bits da memória na memória de configuração - e o circuito eletrônico fornecido é formado no FPGA, que pode ser um processador, controlador de exibição etc.FPGAs / FPGAs não são processadores; ao “programar” os FPGAs (preenchendo a memória de configuração dos FPGAs), você cria um circuito eletrônico (hardware), enquanto que ao programar um processador (hardware fixo), você insere uma cadeia de instruções seqüenciais de programa escritas nele (Programas).Abaixo está um diagrama da unidade FPGA mais simples, que inclui uma tabela de consulta (LUT) e flip-flop. É verdade que, nesse esquema, multiplexadores que alteram a função da célula e conexões com a memória de configuração não são mostrados. Diagramas ilustrando a estrutura do FPGA:

Diagramas ilustrando a estrutura do FPGA: E mais um:

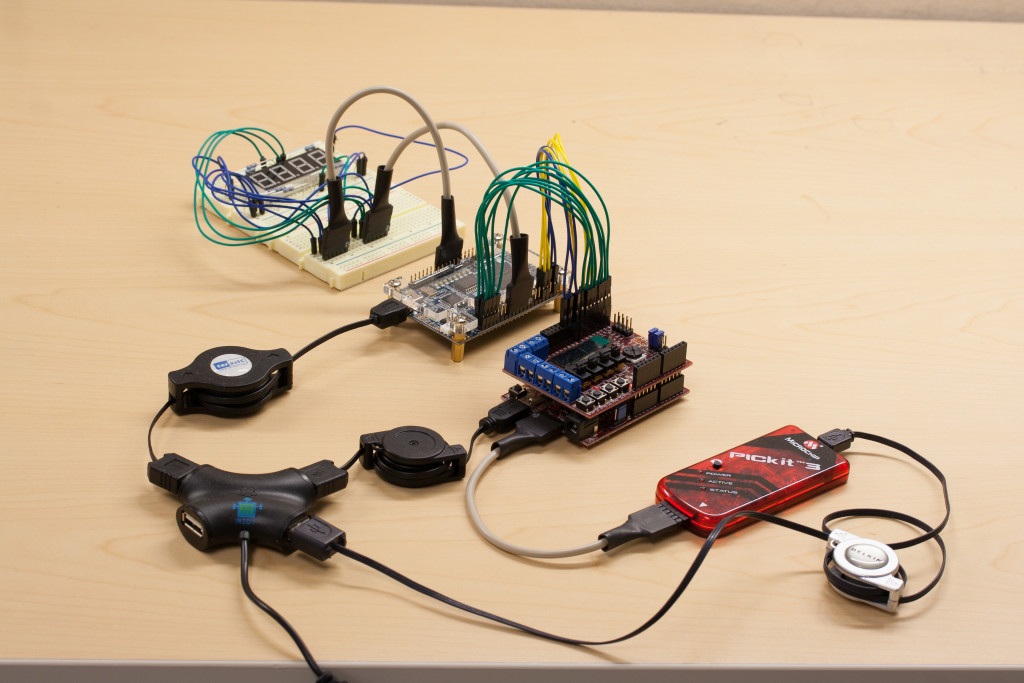

E mais um: Depois do almoço na sala de jantar do Instituto de Física de Engenharia de Moscou, começamos a parte prática. Inicialmente, quando a Imagination Technologies e a Xilinx realizaram esse seminário em Los Angeles, eles usaramslides preparados pelos professores David e Sarah Harris, do sul da Califórnia . Como parecia originalmente, você pode ver no vídeo:Todos os 8 vídeos doworkshop de Los Angeles Para seminários na Rússia, as ligações do núcleo e do laboratório de Harris tiveram que ser substancialmente modificadas. As modificações podem ser encontradas em https://github.com/MIPSfpga/mipsfpga-plus . As diferenças incluem:1. Tudo está classificado para placas-mãe baratas da Altera, disponíveis na Rússia sem mecanismo de importação e exportação2. Carregamento implementado do programa em um sistema sintetizado sem o uso do BusBlaster, simplesmente via UART3. Sensor de luz como periférico em vez de um monitor LCD4. Comutável sinal de freqüência ultra baixa, permitindo que os laboratórios visualizem a operação de qualquer processador interno5. Adicionado um laboratório simples para visualizar erros de cache+ todas as pequenas coisas e cosméticos - um carregador de inicialização / carregador de inicialização mais compacto, a possibilidade de transações estreitas e não armazenáveis em cache na memória, etc.Mais detalhes:1. Portando sob AlteraAntes de tudo, os slides da Harris mostraram tudo para o Xilinx e, recentemente, as placas de remessa dos FPGAs do Xilinx para a Rússia se tornaram um procedimento burocrático bastante complicado que leva de 3 a 4 meses. O mesmo aconteceu com o licenciamento do software para síntese e com o Xilinx Vivado, de localização e rota, mesmo com licenças gratuitas. Algumas universidades russas não tinham placas Xilinx ou licenças Vivado; outros tinham apenas a licença antiga do antecessor do Vivado - o software ISE de 2013, que não suportava FPGAs em placas que eu transportava na Rússia.Em resumo, para seminários na Rússia, camaradas e eu, na Califórnia, transportamos o MIPSfpga para duas placas baratas disponíveis na Rússia, da rival Xilinx Altera (esta empresa está se fundindo à Intel). Os painéis Alter foram doados para as necessidades do workshop pela empresa Zelenograd SPC Elvis . A placa principal da MEPhI, MIPT e SSAU era o Terasic DE0-CV baseado no Altera Cyclone V: outra placa era o Terasic DE0-Nano - um xaile muito compacto adequado para projetos como robôs voadores, mas com uma pequena quantidade de periféricos a bordo: Terasic DE0 - desvantagem O Nano é um pequeno número de dispositivos periféricos na própria placa, mas também é uma vantagem, já que o DE0-Nano pode ser conectado como designer a outras placas e incorporado a diferentes dispositivos:

Depois do almoço na sala de jantar do Instituto de Física de Engenharia de Moscou, começamos a parte prática. Inicialmente, quando a Imagination Technologies e a Xilinx realizaram esse seminário em Los Angeles, eles usaramslides preparados pelos professores David e Sarah Harris, do sul da Califórnia . Como parecia originalmente, você pode ver no vídeo:Todos os 8 vídeos doworkshop de Los Angeles Para seminários na Rússia, as ligações do núcleo e do laboratório de Harris tiveram que ser substancialmente modificadas. As modificações podem ser encontradas em https://github.com/MIPSfpga/mipsfpga-plus . As diferenças incluem:1. Tudo está classificado para placas-mãe baratas da Altera, disponíveis na Rússia sem mecanismo de importação e exportação2. Carregamento implementado do programa em um sistema sintetizado sem o uso do BusBlaster, simplesmente via UART3. Sensor de luz como periférico em vez de um monitor LCD4. Comutável sinal de freqüência ultra baixa, permitindo que os laboratórios visualizem a operação de qualquer processador interno5. Adicionado um laboratório simples para visualizar erros de cache+ todas as pequenas coisas e cosméticos - um carregador de inicialização / carregador de inicialização mais compacto, a possibilidade de transações estreitas e não armazenáveis em cache na memória, etc.Mais detalhes:1. Portando sob AlteraAntes de tudo, os slides da Harris mostraram tudo para o Xilinx e, recentemente, as placas de remessa dos FPGAs do Xilinx para a Rússia se tornaram um procedimento burocrático bastante complicado que leva de 3 a 4 meses. O mesmo aconteceu com o licenciamento do software para síntese e com o Xilinx Vivado, de localização e rota, mesmo com licenças gratuitas. Algumas universidades russas não tinham placas Xilinx ou licenças Vivado; outros tinham apenas a licença antiga do antecessor do Vivado - o software ISE de 2013, que não suportava FPGAs em placas que eu transportava na Rússia.Em resumo, para seminários na Rússia, camaradas e eu, na Califórnia, transportamos o MIPSfpga para duas placas baratas disponíveis na Rússia, da rival Xilinx Altera (esta empresa está se fundindo à Intel). Os painéis Alter foram doados para as necessidades do workshop pela empresa Zelenograd SPC Elvis . A placa principal da MEPhI, MIPT e SSAU era o Terasic DE0-CV baseado no Altera Cyclone V: outra placa era o Terasic DE0-Nano - um xaile muito compacto adequado para projetos como robôs voadores, mas com uma pequena quantidade de periféricos a bordo: Terasic DE0 - desvantagem O Nano é um pequeno número de dispositivos periféricos na própria placa, mas também é uma vantagem, já que o DE0-Nano pode ser conectado como designer a outras placas e incorporado a diferentes dispositivos:

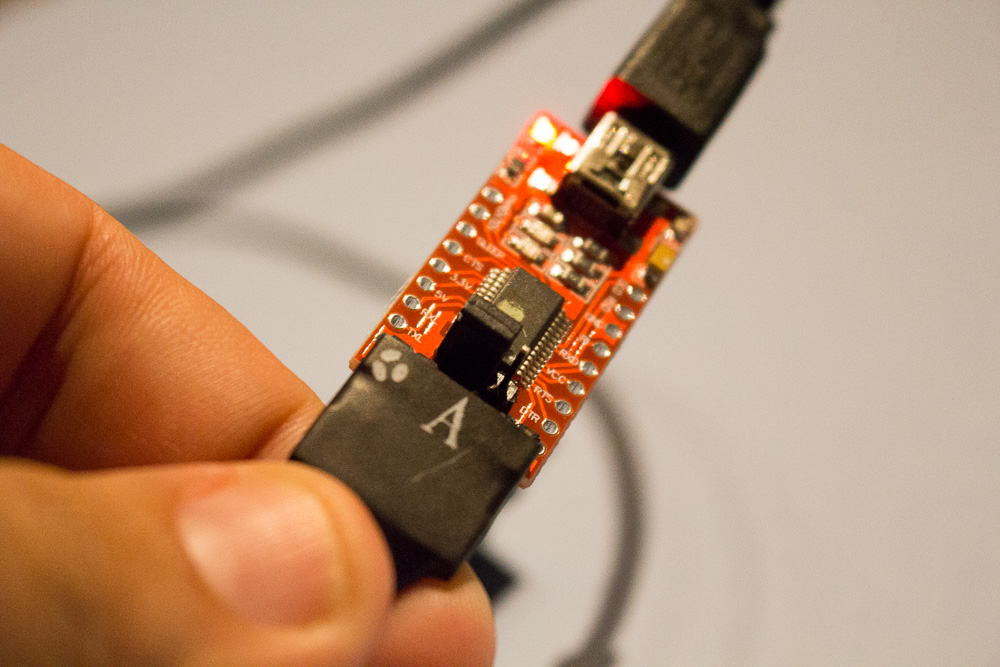

2. Download via UART Osegundo problema de slide da Harris foi usar o adaptador e o software de depuração do Bus Blaster para ele chamado OpenOCD . Basicamente, o BusBlaster / OpenOCD é uma solução muito boa desse tipo. Ele permite não apenas carregar programas no sistema sintetizado dentro do FPGA, mas também depurá-los remotamente via interface EJTAG, um complemento de nível superior à interface JTAG. Ao mesmo tempo, o BusBlaster custa apenas US $ 43, o que é muito mais barato que os adaptadores EJTAG de depuração industrial.Infelizmente, a combinação BusBlaster / OpenOCD é bastante grosseira, e eu tinha medo de que não funcionasse em algumas configurações inesperadas de computadores na Rússia (eu estava certo - não funcionou no MIPT e SSAU). Além disso,Em um site que vende uma combinação BusBlaster / OpenOCD para MIPS , às vezes as placas acabam .Por esse e outros motivos, comecei a procurar outras maneiras de carregar software no sistema (no FPGA, você precisa carregar separadamente a configuração / hardware e software do processador (em um sistema sintetizado com um processador)). O troll anônimo na Internet Alexey tentou me deixar fraco por um longo tempo, para que eu implementasse o gerenciador de inicialização EJTAG através do Altera USB Blaster, mas, como não era especialista em EJTAG, escolhi uma solução simples que funcionava desde a era soviética - para carregar o programa pela porta serial / UART. É verdade que durante a era soviética havia uma porta RS-232C e, na década de 1990, apareceram os chips da FTDI, que tornaram possível fazer tudo através de um cabo USB conectado a um PC. Diferentes variações desse adaptador podem ser compradas por US $ 5 em Moscou e por menos de US $ 2 via Internet da China:

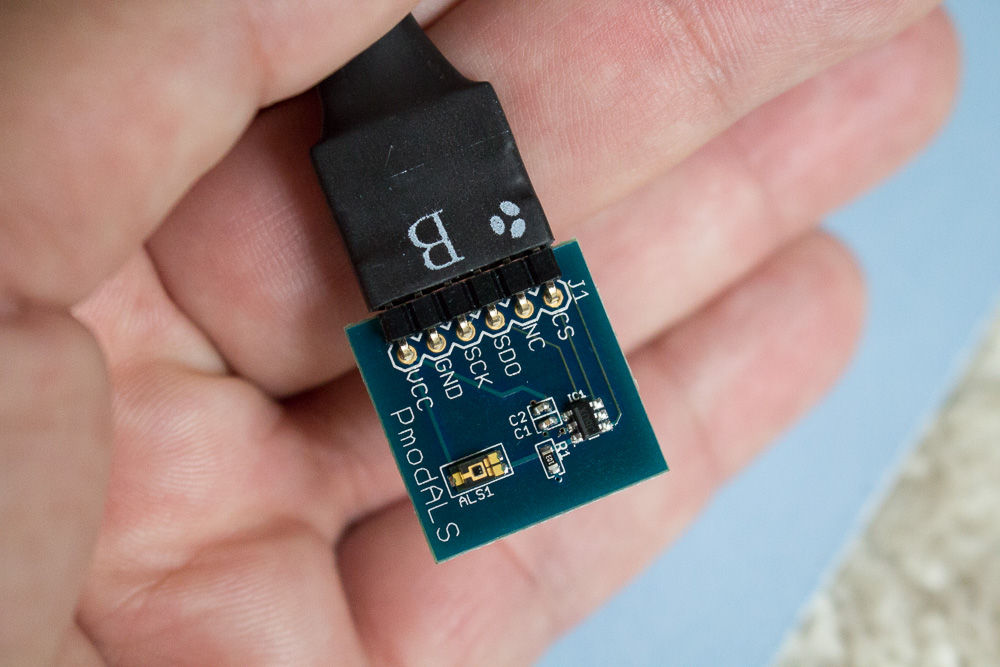

2. Download via UART Osegundo problema de slide da Harris foi usar o adaptador e o software de depuração do Bus Blaster para ele chamado OpenOCD . Basicamente, o BusBlaster / OpenOCD é uma solução muito boa desse tipo. Ele permite não apenas carregar programas no sistema sintetizado dentro do FPGA, mas também depurá-los remotamente via interface EJTAG, um complemento de nível superior à interface JTAG. Ao mesmo tempo, o BusBlaster custa apenas US $ 43, o que é muito mais barato que os adaptadores EJTAG de depuração industrial.Infelizmente, a combinação BusBlaster / OpenOCD é bastante grosseira, e eu tinha medo de que não funcionasse em algumas configurações inesperadas de computadores na Rússia (eu estava certo - não funcionou no MIPT e SSAU). Além disso,Em um site que vende uma combinação BusBlaster / OpenOCD para MIPS , às vezes as placas acabam .Por esse e outros motivos, comecei a procurar outras maneiras de carregar software no sistema (no FPGA, você precisa carregar separadamente a configuração / hardware e software do processador (em um sistema sintetizado com um processador)). O troll anônimo na Internet Alexey tentou me deixar fraco por um longo tempo, para que eu implementasse o gerenciador de inicialização EJTAG através do Altera USB Blaster, mas, como não era especialista em EJTAG, escolhi uma solução simples que funcionava desde a era soviética - para carregar o programa pela porta serial / UART. É verdade que durante a era soviética havia uma porta RS-232C e, na década de 1990, apareceram os chips da FTDI, que tornaram possível fazer tudo através de um cabo USB conectado a um PC. Diferentes variações desse adaptador podem ser compradas por US $ 5 em Moscou e por menos de US $ 2 via Internet da China: Observarei imediatamente que você pode carregar programas no SoC sintetizado de maneiras diferentes. Em um deles, mais tradicional, o sistema possui um pequeno programa fixo na memória (carregador de inicialização), que inicia após a redefinição do sistema e carrega um programa maior pela porta serial / UART. Esse método foi usado por Anton Pavlov, da NIIIS, que o demonstrou em seminários na Universidade Estadual de Moscou e no Instituto de Física de Engenharia de Moscou, e também escreveu sobre ele nos tempos de nerd "MIPSfpga: outside the canon" .Fiz o carregamento de uma maneira alternativa, na qual a memória é preenchida com uma máquina de estado, totalmente implementada no hardware. A máquina aceita um arquivo de texto no formato Motorola S-Record de um PC via UART, analisa-o (tudo no hardware) e enche a memória com dados, enquanto o processador está em um estado de redefinição. Em seguida, o processador acorda e começa a ler o programa na memória do sistema. Tudo o que precisa ser feito no lado do PC é converter o arquivo ELF executável no formato Motorola S-Record e enviá-lo para a porta COM virtual com o comando “tipo” windows-shell.3. Sensor de luz como periférico, em vez de monitor LCDNos laboratórios originais da Harris, eles usaram um indicador de sete segmentos e um display LCD da SPI como exemplos de periféricos. Um exemplo com um indicador de sete segmentos é chato - qualquer aluno entende que se você sabe piscar com uma luz, então sabe piscar com sete luzes. O exemplo do SPI é um pouco melhor, especialmente quando se trata de estudantes iniciantes, mas por que precisamos de uma segunda exibição se já existe um indicador de sete segmentos? Em resumo, antes de viajar para a Rússia, comprei 20 sensores de luz, também com uma interface SPI, e os usei em vez de monitores: Ao mesmo tempo, a interface é muito simples - aqui está o módulo de interface que escrevi (nota: esse código não inclui todas as modificações do sistema para emparelhá-lo) Barramento AHB-Lite, para que o software veja o valor):

Observarei imediatamente que você pode carregar programas no SoC sintetizado de maneiras diferentes. Em um deles, mais tradicional, o sistema possui um pequeno programa fixo na memória (carregador de inicialização), que inicia após a redefinição do sistema e carrega um programa maior pela porta serial / UART. Esse método foi usado por Anton Pavlov, da NIIIS, que o demonstrou em seminários na Universidade Estadual de Moscou e no Instituto de Física de Engenharia de Moscou, e também escreveu sobre ele nos tempos de nerd "MIPSfpga: outside the canon" .Fiz o carregamento de uma maneira alternativa, na qual a memória é preenchida com uma máquina de estado, totalmente implementada no hardware. A máquina aceita um arquivo de texto no formato Motorola S-Record de um PC via UART, analisa-o (tudo no hardware) e enche a memória com dados, enquanto o processador está em um estado de redefinição. Em seguida, o processador acorda e começa a ler o programa na memória do sistema. Tudo o que precisa ser feito no lado do PC é converter o arquivo ELF executável no formato Motorola S-Record e enviá-lo para a porta COM virtual com o comando “tipo” windows-shell.3. Sensor de luz como periférico, em vez de monitor LCDNos laboratórios originais da Harris, eles usaram um indicador de sete segmentos e um display LCD da SPI como exemplos de periféricos. Um exemplo com um indicador de sete segmentos é chato - qualquer aluno entende que se você sabe piscar com uma luz, então sabe piscar com sete luzes. O exemplo do SPI é um pouco melhor, especialmente quando se trata de estudantes iniciantes, mas por que precisamos de uma segunda exibição se já existe um indicador de sete segmentos? Em resumo, antes de viajar para a Rússia, comprei 20 sensores de luz, também com uma interface SPI, e os usei em vez de monitores: Ao mesmo tempo, a interface é muito simples - aqui está o módulo de interface que escrevi (nota: esse código não inclui todas as modificações do sistema para emparelhá-lo) Barramento AHB-Lite, para que o software veja o valor):

4. Orelógio mudou para uma frequência ultrabaixa Quando o MIPSfpga apareceu e os professores das universidades russas começaram a estudá-lo, alguns deles começaram a reclamar que o pacote em sua forma original não é muito interessante para estudantes avançados, uma vez que os laboratórios preparados por David e Sarah Harris usam um processador como uma "caixa preta", apenas conectando dispositivos a ela. Em outras palavras, Harris ignorou completamente que o processador é fornecido no código-fonte e, portanto, é possível implementar laboratórios com ele que permitam que as conexões sejam produzidas a partir de registros arbitrários do processador (não apenas registros visíveis ao programador, mas geralmente a partir de qualquer D-trigger), para conectar por exemplo, para LEDs e observe o que acontece com o processador ao executar determinados programas.Como você entende, para tornar essas observações “vivas”, é necessário fazer o processador funcionar com uma freqüência de clock muito baixa, por exemplo, um clock por segundo. Como fazer isso? O núcleo MIPS microAptiv UP implementado no ASIC na tecnologia de 28 nm pode operar em frequências acima de 500 MHz e na tecnologia de 65 nm acima de 300 MHz. Quando implementadas em FPGAs, as frequências são muito mais baixas, mas ainda altas - 50-60 MHz. As frequências dos geradores de sinal de relógio nas placas são de 50 a 100 MHz, com a possibilidade de aumentar ou diminuir a frequência usando um loop de fase bloqueada (PLL) / loop de fase bloqueada (PLL) .Infelizmente, usando PLL, você pode reduzir a frequência para ~ 100 KHz, mas precisa reduzir a frequência para 1 Hz de outra maneira. No começo, tentei fazer isso usando um bloco da Altera chamadoALTCLKCTRL , mas por algum motivo não funcionou. Tentei dividir o sinal do relógio usando um contador, mas (eu já sabia disso) essa solução por si só não funciona, porque o sintetizador não entende que o sinal de saída é um sinal do relógio e começa a dividi-lo incorretamente, como resultado do qual o processador não funciona. Consultei vários camaradas e começamos a usar a macro Alter “global” (e seu equivalente no Xilinx BUFG). 5. Adicionado um laboratório simples de visualização de falta de cache

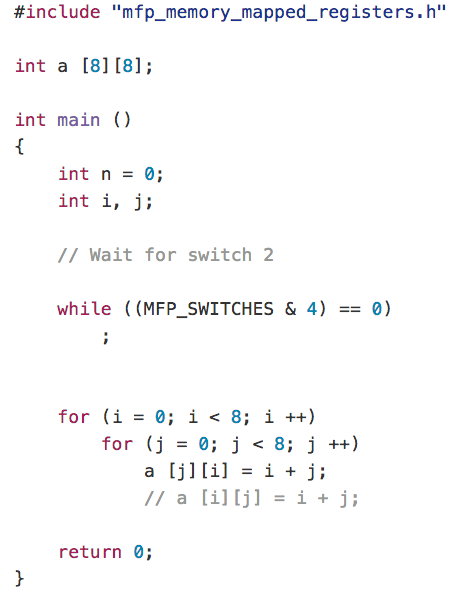

4. Orelógio mudou para uma frequência ultrabaixa Quando o MIPSfpga apareceu e os professores das universidades russas começaram a estudá-lo, alguns deles começaram a reclamar que o pacote em sua forma original não é muito interessante para estudantes avançados, uma vez que os laboratórios preparados por David e Sarah Harris usam um processador como uma "caixa preta", apenas conectando dispositivos a ela. Em outras palavras, Harris ignorou completamente que o processador é fornecido no código-fonte e, portanto, é possível implementar laboratórios com ele que permitam que as conexões sejam produzidas a partir de registros arbitrários do processador (não apenas registros visíveis ao programador, mas geralmente a partir de qualquer D-trigger), para conectar por exemplo, para LEDs e observe o que acontece com o processador ao executar determinados programas.Como você entende, para tornar essas observações “vivas”, é necessário fazer o processador funcionar com uma freqüência de clock muito baixa, por exemplo, um clock por segundo. Como fazer isso? O núcleo MIPS microAptiv UP implementado no ASIC na tecnologia de 28 nm pode operar em frequências acima de 500 MHz e na tecnologia de 65 nm acima de 300 MHz. Quando implementadas em FPGAs, as frequências são muito mais baixas, mas ainda altas - 50-60 MHz. As frequências dos geradores de sinal de relógio nas placas são de 50 a 100 MHz, com a possibilidade de aumentar ou diminuir a frequência usando um loop de fase bloqueada (PLL) / loop de fase bloqueada (PLL) .Infelizmente, usando PLL, você pode reduzir a frequência para ~ 100 KHz, mas precisa reduzir a frequência para 1 Hz de outra maneira. No começo, tentei fazer isso usando um bloco da Altera chamadoALTCLKCTRL , mas por algum motivo não funcionou. Tentei dividir o sinal do relógio usando um contador, mas (eu já sabia disso) essa solução por si só não funciona, porque o sintetizador não entende que o sinal de saída é um sinal do relógio e começa a dividi-lo incorretamente, como resultado do qual o processador não funciona. Consultei vários camaradas e começamos a usar a macro Alter “global” (e seu equivalente no Xilinx BUFG). 5. Adicionado um laboratório simples de visualização de falta de cache Agora você pode fazer experiências divertidas - por exemplo, para fazer o LED piscar durante uma falha de cache e, em seguida, observar em tempo real que o cache bate e falha ao preencher uma matriz bidimensional. Se você preencher a matriz linha por linha, as piscadas serão diferentes das preenchidas nas colunas: Observe que nem tudo correu bem:

Agora você pode fazer experiências divertidas - por exemplo, para fazer o LED piscar durante uma falha de cache e, em seguida, observar em tempo real que o cache bate e falha ao preencher uma matriz bidimensional. Se você preencher a matriz linha por linha, as piscadas serão diferentes das preenchidas nas colunas: Observe que nem tudo correu bem: 1. O GPIO no DE0-Nano é diferente do GPIO nas placas DE0-CV e Xilinx. Em particular, por algum motivo, não consegui declarar toda a porta GPIO como uma entrada e depois usar seus bits individuais como entrada ou saída. Embora no DE0-CV isso funcione bem. Não tive tempo de dividir as diferentes saídas GPIO entre diferentes sinais lógicos (no Verilog), então não classifiquei o laboratório com o sensor de luz no DE0-Nano. Pelo mesmo motivo, não exportei a interface com o Bus Blaster para o DE0-CV.2. Pior ainda, o download via UART para DE0-Nano não funcionou na MEPhI, embora antes tenha funcionado na Universidade Estadual de Moscou e no meu laptop. O motivo ainda não é 100% claro:2.1 Talvez houvesse um problema de incompatibilidade da versão do Windows (7 com o patch) e do cabo USB-UART usado para o DE0-Nano. O cabo era um clone chinês barato, baseado no chipset PL2303TA, embora eu não tenha experimentado antes do seminário. Sabe-se que a versão anterior desses cabos, baseada em chipsets com PL2303HX, apresentava um problema de compatibilidade com o Windows 8 ( consulte ). O mais hediondo que eu tinha comigo um laptop com uma versão do Windows 7 e um laptop com uma versão do Windows 8 e várias alternativas para esse cabo. Mas não verifiquei todas as combinações antes do seminário, apesar de poder ter feito na noite anterior - infelizmente.2.2 Dois dias antes do workshop, fiz alterações no divisor de relógio. Também não valia a pena.2.3 Bem, pelo menos tudo funcionou bem no DE0-CV.3. No MEPhI, mostrei uma versão mais complexa do exemplo de cache do que antes na Universidade Estadual de Moscou. Foi um erro - em um exemplo complexo, o compilador otimizou alguma coisa, e o padrão das luzes não era tão óbvio quanto no exemplo simples original. A situação foi um pouco salva pelo orador adicional convidado do NIIMI Anton Pavlov, que, embora não tivesse tempo no MEPhI, mostrou alguns presentes sua própria versão da ligação do MIPSfpga chamada myMIPSfpga, que ele também descreveu na nota "MIPSfpga: fora do cânone" . Entre outras coisas, Anton transportou o MIPSfpga para o conselho russo Mars rover 3

1. O GPIO no DE0-Nano é diferente do GPIO nas placas DE0-CV e Xilinx. Em particular, por algum motivo, não consegui declarar toda a porta GPIO como uma entrada e depois usar seus bits individuais como entrada ou saída. Embora no DE0-CV isso funcione bem. Não tive tempo de dividir as diferentes saídas GPIO entre diferentes sinais lógicos (no Verilog), então não classifiquei o laboratório com o sensor de luz no DE0-Nano. Pelo mesmo motivo, não exportei a interface com o Bus Blaster para o DE0-CV.2. Pior ainda, o download via UART para DE0-Nano não funcionou na MEPhI, embora antes tenha funcionado na Universidade Estadual de Moscou e no meu laptop. O motivo ainda não é 100% claro:2.1 Talvez houvesse um problema de incompatibilidade da versão do Windows (7 com o patch) e do cabo USB-UART usado para o DE0-Nano. O cabo era um clone chinês barato, baseado no chipset PL2303TA, embora eu não tenha experimentado antes do seminário. Sabe-se que a versão anterior desses cabos, baseada em chipsets com PL2303HX, apresentava um problema de compatibilidade com o Windows 8 ( consulte ). O mais hediondo que eu tinha comigo um laptop com uma versão do Windows 7 e um laptop com uma versão do Windows 8 e várias alternativas para esse cabo. Mas não verifiquei todas as combinações antes do seminário, apesar de poder ter feito na noite anterior - infelizmente.2.2 Dois dias antes do workshop, fiz alterações no divisor de relógio. Também não valia a pena.2.3 Bem, pelo menos tudo funcionou bem no DE0-CV.3. No MEPhI, mostrei uma versão mais complexa do exemplo de cache do que antes na Universidade Estadual de Moscou. Foi um erro - em um exemplo complexo, o compilador otimizou alguma coisa, e o padrão das luzes não era tão óbvio quanto no exemplo simples original. A situação foi um pouco salva pelo orador adicional convidado do NIIMI Anton Pavlov, que, embora não tivesse tempo no MEPhI, mostrou alguns presentes sua própria versão da ligação do MIPSfpga chamada myMIPSfpga, que ele também descreveu na nota "MIPSfpga: fora do cânone" . Entre outras coisas, Anton transportou o MIPSfpga para o conselho russo Mars rover 3 que eu, como homem torturado por importação e exportação (Scylla: controle de exportação americano + Charybdis: costumes russos), tentarei usar nos seguintes eventos educacionais na Rússia: Durante o intervalo e após o seminário, Maxim Gorbunov me mostrou vários pontos míticos, que incluem três painéis no espírito da época da galáxia de Andrômeda e do café molecular de vários volumes vermelho e branco vem de 1960: UPD: Como nos comentários, começaram a discutir a igreja mifishnuyu, e eu farei isso (não estou inserido l Este fragmento era originalmente, pois ele não tinha certeza de que era apropriado para os geeks):

que eu, como homem torturado por importação e exportação (Scylla: controle de exportação americano + Charybdis: costumes russos), tentarei usar nos seguintes eventos educacionais na Rússia: Durante o intervalo e após o seminário, Maxim Gorbunov me mostrou vários pontos míticos, que incluem três painéis no espírito da época da galáxia de Andrômeda e do café molecular de vários volumes vermelho e branco vem de 1960: UPD: Como nos comentários, começaram a discutir a igreja mifishnuyu, e eu farei isso (não estou inserido l Este fragmento era originalmente, pois ele não tinha certeza de que era apropriado para os geeks):

Eu fui à igreja mítica, em torno da qual havia tantos gritos na Internet há cerca de três anos, por causa dos quais os funcionários deixaram o Instituto de Física de Engenharia de Moscou em protesto. Como uma pessoa neutra, ou seja, um incrédulo e não militante de um ou outro lado do conflito, devo dizer que 1) a igreja mítica é bastante modesta e não vulgar, semelhante em espírito à Catedral Ortodoxa em São Francisco; 2) MEPhI não é a primeira universidade russa com religião, o curso de Ortodoxia já apareceu no Instituto de Física e Tecnologia de Moscou em 1988 (então toda a faculdade de física e tecnologia o procurou, os alunos ouviram a primeira palestra em pé, mas depois de três meses não havia mais do que uma dúzia de estudantes); 3) existem igrejas em muitas universidades americanas. Continua.

Eu fui à igreja mítica, em torno da qual havia tantos gritos na Internet há cerca de três anos, por causa dos quais os funcionários deixaram o Instituto de Física de Engenharia de Moscou em protesto. Como uma pessoa neutra, ou seja, um incrédulo e não militante de um ou outro lado do conflito, devo dizer que 1) a igreja mítica é bastante modesta e não vulgar, semelhante em espírito à Catedral Ortodoxa em São Francisco; 2) MEPhI não é a primeira universidade russa com religião, o curso de Ortodoxia já apareceu no Instituto de Física e Tecnologia de Moscou em 1988 (então toda a faculdade de física e tecnologia o procurou, os alunos ouviram a primeira palestra em pé, mas depois de três meses não havia mais do que uma dúzia de estudantes); 3) existem igrejas em muitas universidades americanas. Continua.

Source: https://habr.com/ru/post/pt387157/

All Articles