Prototipagem ASIC em FPGA

O desenvolvimento de chips é complexo, caro e demorado. E o preço de qualquer erro é extremamente alto. Depois de fazer o cristal com patches e atualizações, nada pode ser corrigido. Portanto, a verificação dos esquemas projetados no estágio de desenvolvimento é especialmente meticulosa. Para cada bloco funcional, os testes de bloco são gravados em todos os modos de operação e fora de operação. Após a integração do bloco no circuito geral, são realizados testes do sistema sobre como esse bloco funciona como parte do sistema. Todos os testes estão girando constantemente nos testes de regressão. Existe até um sinal informal de um nível de teste menos ou menos aceitável - quando a quantidade de código de teste é 10 vezes a quantidade de código da unidade que está sendo testada. Mas todos esses testes não dão a sensação de que o circuito é viável, pois qualquer simulação é o comportamento do circuito por centenas de milissegundos no máximo.Mas na vida, o circuito deve funcionar centenas de milhares de horas. Uma vez, procurei uma falha quando foram perdidos 1 ou 2 bytes por 1 GB de informações transmitidas e nenhum teste funcional encontrou esse problema. E esse erro foi manifestado apenas no protótipo FPGA do futuro chip. Sobre quais protótipos fizemos e o que está acontecendo no mundo, este artigo mostrará.Prototipar futuros chips em um FPGA é a única maneira de testar como o circuito funciona em tarefas do mundo real em menos tempo real. O protótipo permite depurar software, obter características iniciais de desempenho e muito mais. Os FPGAs modernos têm uma quantidade suficientemente grande de recursos para essas tarefas. Por exemplo, você mesmo pode implementar um computador completo com um processador Intel 8086 em uma placa-mãe com FPGA por US $ 300 .Ano 2004

Infelizmente, não conseguimos encontrar o primeiro protótipo nos depósitos de nosso gabinete com esqueletos, mas era um pequeno cachecol baseado no Xilinx Spartan3-400 (XC3S400). 400 significa o número de milhares de equivalentes de válvulas que estão disponíveis para o desenvolvedor para criar seu circuito. O preço do lenço era de aproximadamente US $ 50 e permitia implementar nele um simples microcontrolador de 8 bits com toda a memória e a uma frequência de 40 MHz. A prototipagem consistiu no fato de o microcontrolador desenvolvido nele piscar um LED.2005 ano

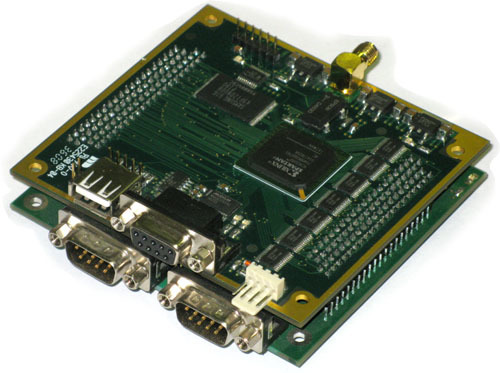

O quadro especial para o protótipo já foi desenvolvido não como um experimento, mas como uma etapa significativa do projeto. Já aplicado FPGA Xilinx Spartan3-1000. Essa. 1 milhão de válvulas já estavam disponíveis para nós, e o microcontrolador projetado trabalhava em sua frequência máxima de 48 MHz. E foi nessa placa que peguei os 2 bytes perdidos por gigabyte. O preço do conselho era de aproximadamente US $ 200.

2007 ano

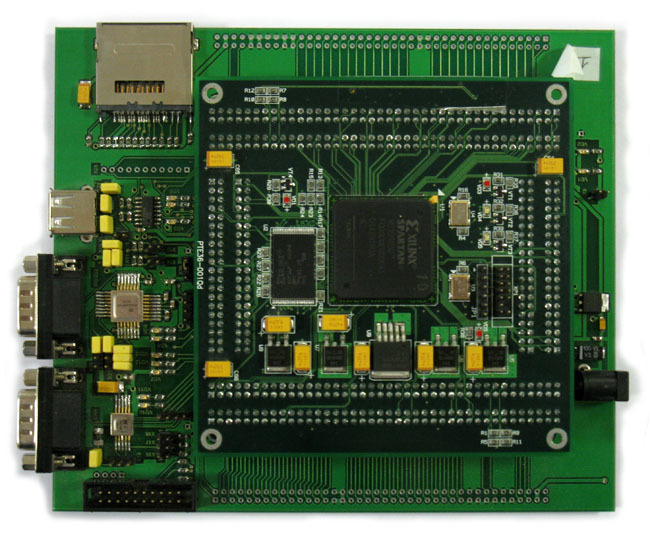

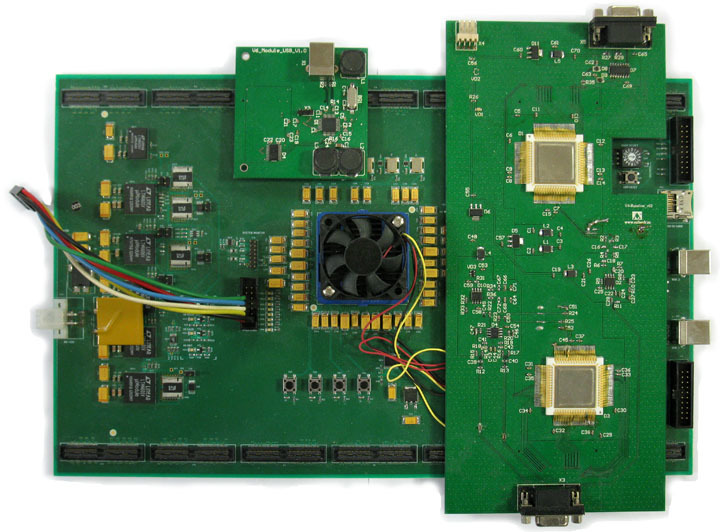

Para o novo microcontrolador de 32 bits, era óbvio que 1 milhão de válvulas pode não ser suficiente. Portanto, uma nova placa-mãe baseada no Xilinx Spartan3-5000 foi desenvolvida, graças à qual 5 milhões de portas ficaram disponíveis. O preço do conselho era de aproximadamente US $ 500 e, por muito tempo, esse conselho se tornou o principal para a criação de protótipos de novos desenvolvimentos. Em sua base, não apenas os microcontroladores foram testados, mas também vários microcircuitos especializados. O microcontrolador projetado em FPGA já estava operando a uma frequência reduzida de 20 MHz, embora em silício funcionasse em frequências de 100 MHz e até 150 MHz.O protótipo do microcontrolador de 32 bits: O protótipo da placa de vídeo (infelizmente o projeto não foi lançado, mas o RTL final está aguardando):

O protótipo da placa de vídeo (infelizmente o projeto não foi lançado, mas o RTL final está aguardando): O protótipo do switch Ethernet de 4 vias com transceptores integrados:

O protótipo do switch Ethernet de 4 vias com transceptores integrados:

Ano 2010

Ao desenvolver um microcontrolador de núcleo duplo (núcleo RISC de 32 bits + núcleo de DSP de 16 bits), finalmente alcançamos o nível em que 5 milhões já não eram suficientes. Mas a implementação no FPGA de várias configurações truncadas do futuro microcircuito tornou possível testar sua operação. Por exemplo, eles venderam dois núcleos (RISC + DSP) com um conjunto truncado de periféricos ou um núcleo (RISC), mas toda a periferia.ano de 2012

O novo projeto exigia uma nova placa, pois a quantidade necessária de memória interna para o novo núcleo DSP de 32 bits já excedia a capacidade disponível no maior Spartan FPGA. Eu tive que mudar para FPGAs mais caros e complexos. O tempo do projeto foi limitado e decidiu encontrar uma solução pronta. A escolha recaiu sobre o INREVIUM c, o maior da época FPGA Xilinx Virtex-6 XC6VLX760. E, embora o número de portas equivalentes tenha aumentado para apenas 8 milhões, a quantidade de memória de bloco incorporada aumentou de 2 Mbit para 25 Mbit.A escolha também provavelmente determinou que o custo da taxa foi preservado no site do escritório de representação alemão no cache do Google, e sabíamos que custaria US $ 18 mil antes da assinatura de qualquer NDA. E com o custo de apenas um chip FPGA de US $ 15 mil, isso removeu qualquer dúvida sobre o desenvolvimento de sua própria placa. Placas seriais para FPGAs tão grandes geralmente custam tanto quanto os próprios FPGAs ou são um pouco mais caras.A compra do conselho também trouxe muitos conhecimentos interessantes, por exemplo, nosso distribuidor local estava convencido de que esse conselho custa US $ 40 mil, incluindo frete, e, em geral, arrisca muito com pré-pagamento de 100% da nossa parte. Por fim, três dessas placas foram compradas sem intermediários e agora são usadas para prototipar nossos processadores DSP.

E, embora o número de portas equivalentes tenha aumentado para apenas 8 milhões, a quantidade de memória de bloco incorporada aumentou de 2 Mbit para 25 Mbit.A escolha também provavelmente determinou que o custo da taxa foi preservado no site do escritório de representação alemão no cache do Google, e sabíamos que custaria US $ 18 mil antes da assinatura de qualquer NDA. E com o custo de apenas um chip FPGA de US $ 15 mil, isso removeu qualquer dúvida sobre o desenvolvimento de sua própria placa. Placas seriais para FPGAs tão grandes geralmente custam tanto quanto os próprios FPGAs ou são um pouco mais caras.A compra do conselho também trouxe muitos conhecimentos interessantes, por exemplo, nosso distribuidor local estava convencido de que esse conselho custa US $ 40 mil, incluindo frete, e, em geral, arrisca muito com pré-pagamento de 100% da nossa parte. Por fim, três dessas placas foram compradas sem intermediários e agora são usadas para prototipar nossos processadores DSP.ano 2013

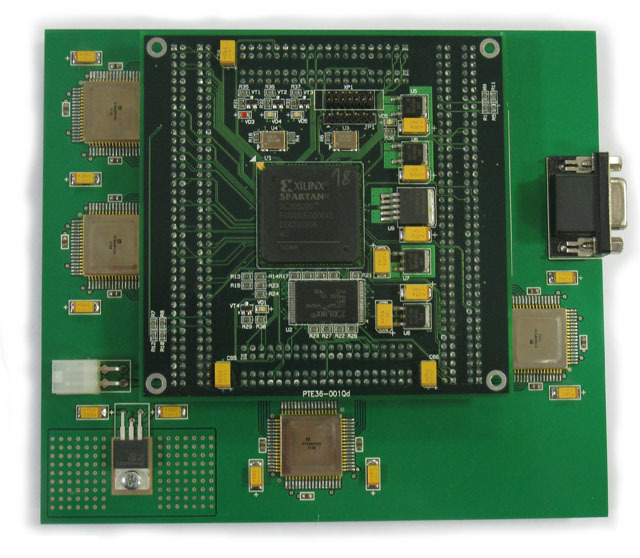

Para o novo microcontrolador especializado de 32 bits, foi decidido tentar criar sua própria placa. Primeiro, os desenvolvedores de módulos em FPGAs devem desenvolver e não ter medo de usar microcircuitos que são mais caros que seus carros pessoais e, segundo, um dos distribuidores tinha vários Virtex-6 XC6VLX550T em estoque e ele os ofereceu com um grande desconto. O FPGA LX550T é um passo menor que o LX760 (cerca de 30% menos válvulas), mas o preço final das placas, levando em consideração o desenvolvimento, foi de apenas US $ 8K. 6 placas foram montadas. Não planejamos distribuí-los aos clientes, mas organizamos para os desenvolvedores o acesso a eles via Internet. O conselho implementou muitas soluções interessantes. Por exemplo, os arquivos de firmware foram carregados na placa, como em um dispositivo MassStorage, em um cartão SD especial e, em seguida, carregados a partir dele no FPGA.No total, o cartão pode ter até 10 firmwares diferentes e, por meio de um programa de gerenciamento especial, você pode escolher qual usar no momento. Também implementou várias proteções "do tolo", para não queimar acidentalmente um chip caro. Tudo isso permite que você trabalhe com esses painéis remotamente, com segurança e confie neles mesmo aos alunos. O MK projetado em FPGA funcionava a uma frequência de 40 MHz.A própria placa (protótipo de um microcontrolador de 32 bits de núcleo duplo especializado): Protótipo de um chip especializado para sensores de conversão de ângulo para código:

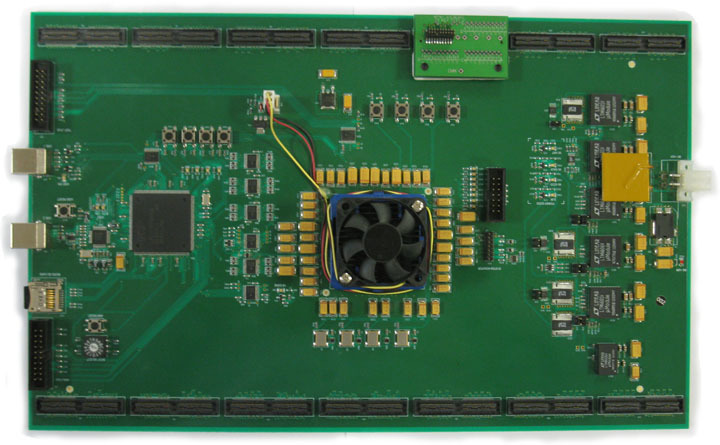

Protótipo de um chip especializado para sensores de conversão de ângulo para código: Infelizmente, esta placa tem várias desvantagens: conectores ruins são selecionados para conectar módulos adicionais, mas é metade do problema, esquecemos de corrigir orifícios próximos aos conectores, e os módulos são realmente mantidos apenas nos conectores. Para obter acesso a alguns controles na placa principal, você precisa descobrir os módulos de expansão.

Infelizmente, esta placa tem várias desvantagens: conectores ruins são selecionados para conectar módulos adicionais, mas é metade do problema, esquecemos de corrigir orifícios próximos aos conectores, e os módulos são realmente mantidos apenas nos conectores. Para obter acesso a alguns controles na placa principal, você precisa descobrir os módulos de expansão.Experiência doméstica

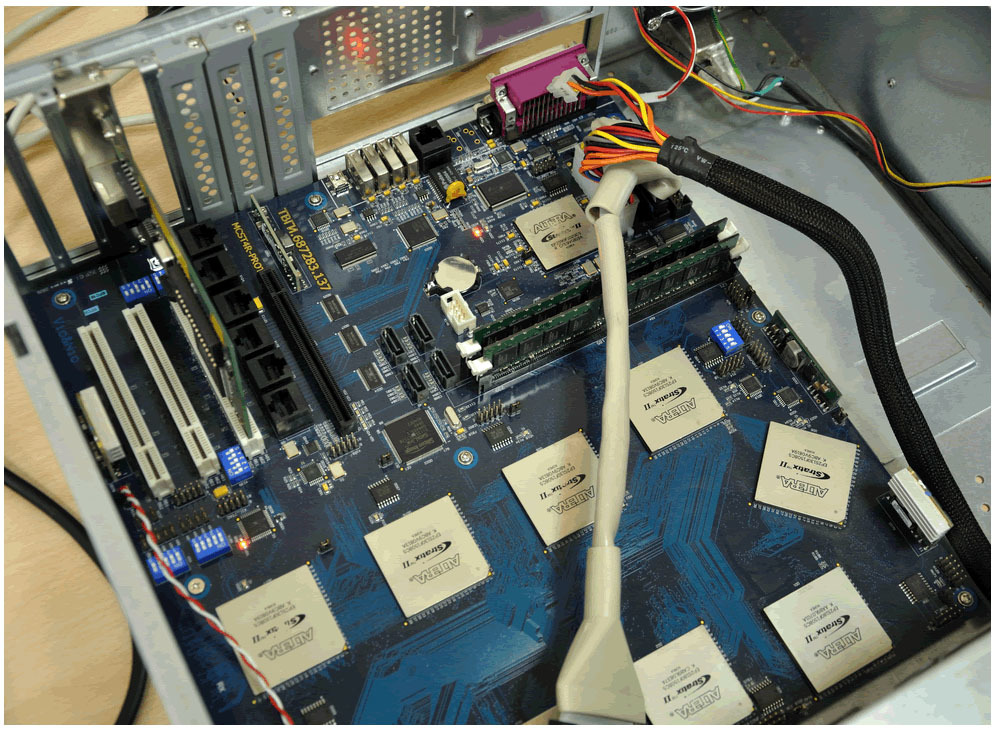

Mas e os outros desenvolvedores de chips personalizados? Por exemplo, o MCST ao prototipar o VLSI 1891VM6Ya (R-1000, um processador de quatro núcleos com arquitetura SPARC v.9 de 64 bits) usou uma placa especializada com 10 FPGAs Altera Stratix II (4 x EP2S180 + 5 x EP2S130 + 1 x EP2S90). O volume total de portas lógicas do sistema pode ser estimado em 20 milhões.Agora, um chip EP2S180 custa cerca de US $ 8 mil. Portanto, o custo de apenas chips FPGA no protótipo excede US $ 50 mil.Para a prototipagem do processador Elbrus-4C +, já eram necessários 21 microcircuitos Altera Stratix IV EP4SE820 e com um volume total de 100 milhões de válvulas (embora o próprio MCST cite uma cifra de 750 milhões) e custa cerca de US $ 200 mil. Ao mesmo tempo, a frequência de trabalho do protótipo é de 9 MHz.

um chip EP2S180 custa cerca de US $ 8 mil. Portanto, o custo de apenas chips FPGA no protótipo excede US $ 50 mil.Para a prototipagem do processador Elbrus-4C +, já eram necessários 21 microcircuitos Altera Stratix IV EP4SE820 e com um volume total de 100 milhões de válvulas (embora o próprio MCST cite uma cifra de 750 milhões) e custa cerca de US $ 200 mil. Ao mesmo tempo, a frequência de trabalho do protótipo é de 9 MHz.Experiência estrangeira

Agora, soluções especializadas para prototipagem FPGA são oferecidas por empresas especializadas no desenvolvimento de ferramentas CAD para microeletrônica, embora módulos adequados para prototipagem também possam ser encontrados em outras empresas. Intel e IBM possuem protótipos FPGA, mas suas características não são anunciadas e só são conhecidas por um amplo círculo quando o protótipo já está desatualizado.A Cadence oferece uma plataforma especial de prototipagem rápida, construída no FPGA da Altera Stratix-4 EP4SE820. Na configuração mínima, a plataforma consiste em duas (com um volume total de 10 milhões de válvulas) e no máximo em seis FPGAs (com um volume de até 30 milhões de válvulas). O preço de um chip EP4SE820 hoje é de ~ $ 10K. O novo sistema da Cadence é chamado Protium e é baseado no Xilinx Virtex-7 XC7V2000T e permite implementar de 25 milhões em dois FPGAs a 100 milhões de válvulas em oito. O custo de um chip XC7V2000T agora é de cerca de US $ 20 mil. Essa. Protium totalmente equipado custará pelo menos US $ 160 mil.Além das ferramentas de desenvolvimento, a Aldec também oferece uma plataforma para prototipagem FPGA do HES-7.

O novo sistema da Cadence é chamado Protium e é baseado no Xilinx Virtex-7 XC7V2000T e permite implementar de 25 milhões em dois FPGAs a 100 milhões de válvulas em oito. O custo de um chip XC7V2000T agora é de cerca de US $ 20 mil. Essa. Protium totalmente equipado custará pelo menos US $ 160 mil.Além das ferramentas de desenvolvimento, a Aldec também oferece uma plataforma para prototipagem FPGA do HES-7. Até seis Xilinx Virtex-7 XC7V2000T ou UltraSacle XCVU440 estão localizados em uma placa. No caso da implementação do módulo baseado no FPGA UltraSacle XCVU440, o número total de portas atinge 158 milhões.Com uma placa adicional, você pode montar 24 chips FPGA em um único módulo e obter 633 milhões de portas. O custo de um chip XCVU440 agora é de US $ 49 mil. E o custo total máximo de todos os FPGAs excede 1 milhão de dólares.A Synopsys tem provavelmente a maior experiência no desenvolvimento de plataformas para prototipagem FPGA. Seus primeiros modelos foram baseados no FPGA Virtex-6 (HAPS-60), depois Virtex-7 (HAPS-70). Seu mais recente desenvolvimento, o HAPS-80, em um único módulo contém de um a quatro FPGAs Xilinx UltraScale XCVU440.

Até seis Xilinx Virtex-7 XC7V2000T ou UltraSacle XCVU440 estão localizados em uma placa. No caso da implementação do módulo baseado no FPGA UltraSacle XCVU440, o número total de portas atinge 158 milhões.Com uma placa adicional, você pode montar 24 chips FPGA em um único módulo e obter 633 milhões de portas. O custo de um chip XCVU440 agora é de US $ 49 mil. E o custo total máximo de todos os FPGAs excede 1 milhão de dólares.A Synopsys tem provavelmente a maior experiência no desenvolvimento de plataformas para prototipagem FPGA. Seus primeiros modelos foram baseados no FPGA Virtex-6 (HAPS-60), depois Virtex-7 (HAPS-70). Seu mais recente desenvolvimento, o HAPS-80, em um único módulo contém de um a quatro FPGAs Xilinx UltraScale XCVU440. Os módulos prontos podem ser combinados em um único rack. E, neste caso, o volume total é um recorde de 1,6 bilhão de válvulas.Ao usar um FPGA, a frequência máxima é de 300 MHz, ao usar os vizinhos em um módulo para 100 MHz, ao usar vários módulos, a frequência é reduzida para 30 MHz.

Os módulos prontos podem ser combinados em um único rack. E, neste caso, o volume total é um recorde de 1,6 bilhão de válvulas.Ao usar um FPGA, a frequência máxima é de 300 MHz, ao usar os vizinhos em um módulo para 100 MHz, ao usar vários módulos, a frequência é reduzida para 30 MHz. Assim, tendo aproximadamente US $ 3,5 milhões para a compra de FPGAs, você pode montar uma plataforma adequada para a prototipagem do Intel Xeon E7. Bem, ou espere 20 anos, quando FPGAs desse volume cairão de preço para algumas centenas de dólares.

Assim, tendo aproximadamente US $ 3,5 milhões para a compra de FPGAs, você pode montar uma plataforma adequada para a prototipagem do Intel Xeon E7. Bem, ou espere 20 anos, quando FPGAs desse volume cairão de preço para algumas centenas de dólares. Source: https://habr.com/ru/post/pt387653/

All Articles