Distribuição de elefantes: placas FPGA para projetos educacionais com MIPSfpga

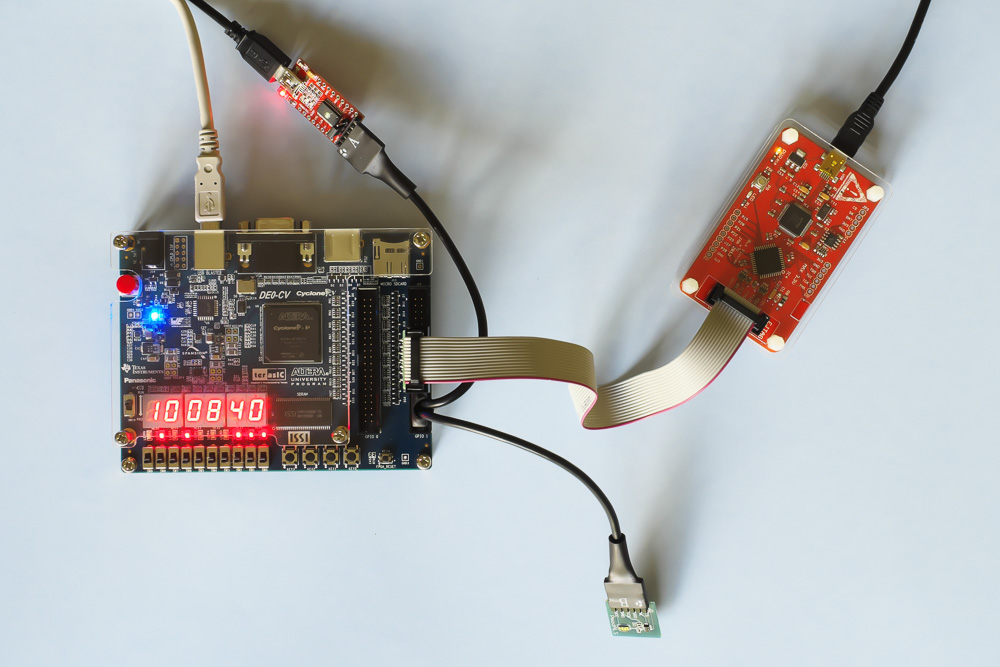

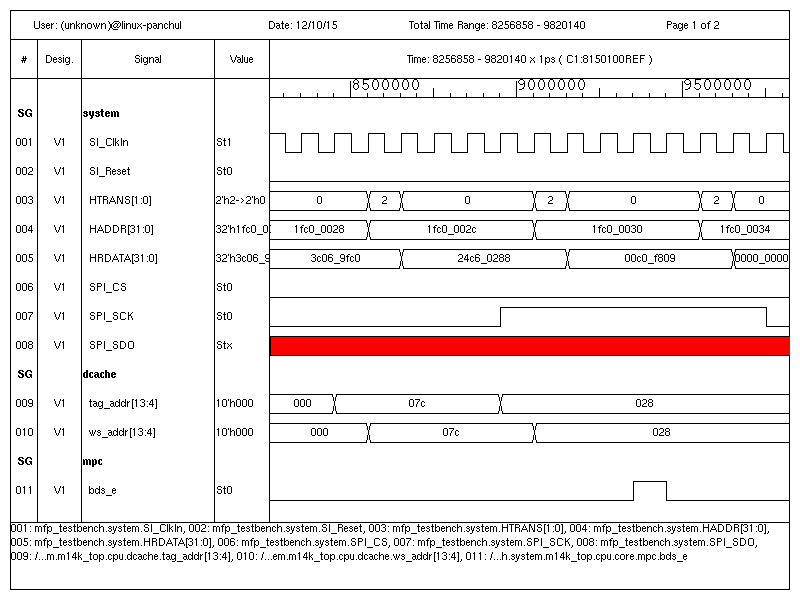

Há um mês, seminários sobre o MIPSfpga ( 1 , 2 , 3 , 4 ) foram realizados nas universidades russas , e um senhor do NIIIS chamado Anton Pavlov escreveu uma nota sobre suas próprias melhorias no MIPSfpga "MIPSfpga: fora do cânone" . Desde que os professores conheceram o novo produto para ensinar positivamente os estudantes de eletrônica como um todo, surgiu a idéia de ajudar a começar com os conselhos e, ao mesmo tempo, com várias pessoas e organizações.Em particular, em homenagem ao Ano Novo, estou em cooperação com Vitaliy Kravchenko de univeda.ruEstamos planejando uma pequena distribuição de elefantes, ou seja, placas Terasic DE0-CV gratuitas com o FPGA Altera Cyclone V. Para que você possa repetir a ação de Anton Pavlov. Como essa distribuição específica é feita - não com o dinheiro da Imagination Technologies, não com o dinheiro da Altera e não com o dinheiro do Elvis Scientific and Production Center, mas com o dinheiro de benfeitores privados, inclusive eu pessoalmente, os elefantes serão distribuídos com condições bastante específicas descritas abaixo. Os objetivos do evento: 1. Aumentar o nível de envolvimento das universidades russas em pesquisas mundiais no campo da microarquitetura de processadores, design de SoCs e sistemas heterogêneos de múltiplos núcleos 2. Aumentar o número de textos em russo no MIPS Insider para que visitantes da indústria eletrônica e da academia internacional comecem a entender que os russos estão chegando 3. Criar, em nome da comunidade, um monte de materiais de treinamento em torno do MIPSfpga, que poderiam ser usados por professores de universidades russas e professores de universidades de outros países - EUA, Japão, China, etc.Termos:1. É desejável que o beneficiário seja professor, estudante de graduação ou estudante de uma universidade russa.2. É desejável que esta universidade não seja a Universidade Estadual de Moscou, o Instituto de Física e Tecnologia de Moscou, MEPhI, MIET e ITMO, que podem receber essas taxas de outras fontes.3. É muito desejável que, antes de receber o quadro, um amigo criativo me envie não apenas uma descrição do projeto, mas também um código em Verilog ou VHDL, C e / ou assembler, com o qual ele simulou um protótipo de um futuro sistema sintetizado no ambiente ModelSim ou Icarus. Diagramas de tempo também são bem-vindos.4. O código do projeto após a conclusão é carregado em http://github.com/MIPSfpga - veja http://github.com/MIPSfpga/mipsfpga-plus5. Como exemplo, também é descrito na seção Wiki:5.1. O que há em cada arquivo5.2 Hierarquia de módulos de hardware5.3. Como simular - instruções com screenshots5.4. Diagramas de tempo da simulação5.5. Como sintetizar - instruções com screenshots5.6. Resultados da síntese - tamanho e frequência máxima5.7. Descrição da parte do software5.8. Fotos do FPGA de trabalho6. Isso é descrito em http://geektimes.ru na forma do artigo7. O mesmo é descrito em http://silicon-russia.com8. O mesmo é descrito em http://community.imgtec.com / forums / cat / mips-insider / mipsfpga9. O idioma (6), (7), (8) pode ser russo ou inglês10. Se você não fizer nada com o conselho por um mês, ele será retirado de você e transferido para outra pessoa11. Se nós (eu e o UnivEDA) fizermos eventos na Rússia, como competições ou treinamentos, também cobraremos uma taxa Retome o tempoExemplos de projetos com placas:1. Interface entre o MIPSfpga e sensores com interfaces SPI, I2C, UART e outros. Sensores de umidade, temperatura, som, bússolas, telêmetro, etc.2. A interface entre o MIPSfpga e o externo em relação à memória FPGA - SDRAM, DDR, etc. (nos exemplos atuais, a memória do sistema é construída a partir da memória em bloco dentro do FPGA)3. A interface entre o MIPSfpga e dispositivos maiores é um monitor VGA, mouse, teclado, joystick.4. Visualização do cache executando o processador a uma frequência de 1 relógio por segundo e emitindo sinais relacionados à transação (solicitação, falha, etc.).5. Visualização da operação do transportador e dos dispositivos aritméticos, iniciando o processador com uma frequência de 1 relógio por segundo e emitindo sinais de controle do transportador, etc.6. Adicionando comandos ao processador usando a interface CorExtend / Instruções Definidas pelo Usuário (UDI). Um exemplo são comandos especiais de criptografia.7. Trabalho de laboratório com uma demonstração da operação de interrupção em diferentes modos e um manipulador de interrupção.8. Pontes entre o ônibus AHB-Lite e outros ônibus - AXI, APB, OCP, Wishbone, PLB, etc.9. Sistemas multiprocessadores sem a coerência de caches de primeiro nível e (para os mais avançados) com caches coerentes e implementação de protocolos como o MESI.10. Portando para o MIPSfpga vários programas e sistemas operacionais - do RTOS simples a várias variantes do Linux (o MIPSfpga suporta TLB MMU).Envie sugestões para yuri.panchul@imgtec.com com uma cópia de yuri@panchul.com

3. Criar, em nome da comunidade, um monte de materiais de treinamento em torno do MIPSfpga, que poderiam ser usados por professores de universidades russas e professores de universidades de outros países - EUA, Japão, China, etc.Termos:1. É desejável que o beneficiário seja professor, estudante de graduação ou estudante de uma universidade russa.2. É desejável que esta universidade não seja a Universidade Estadual de Moscou, o Instituto de Física e Tecnologia de Moscou, MEPhI, MIET e ITMO, que podem receber essas taxas de outras fontes.3. É muito desejável que, antes de receber o quadro, um amigo criativo me envie não apenas uma descrição do projeto, mas também um código em Verilog ou VHDL, C e / ou assembler, com o qual ele simulou um protótipo de um futuro sistema sintetizado no ambiente ModelSim ou Icarus. Diagramas de tempo também são bem-vindos.4. O código do projeto após a conclusão é carregado em http://github.com/MIPSfpga - veja http://github.com/MIPSfpga/mipsfpga-plus5. Como exemplo, também é descrito na seção Wiki:5.1. O que há em cada arquivo5.2 Hierarquia de módulos de hardware5.3. Como simular - instruções com screenshots5.4. Diagramas de tempo da simulação5.5. Como sintetizar - instruções com screenshots5.6. Resultados da síntese - tamanho e frequência máxima5.7. Descrição da parte do software5.8. Fotos do FPGA de trabalho6. Isso é descrito em http://geektimes.ru na forma do artigo7. O mesmo é descrito em http://silicon-russia.com8. O mesmo é descrito em http://community.imgtec.com / forums / cat / mips-insider / mipsfpga9. O idioma (6), (7), (8) pode ser russo ou inglês10. Se você não fizer nada com o conselho por um mês, ele será retirado de você e transferido para outra pessoa11. Se nós (eu e o UnivEDA) fizermos eventos na Rússia, como competições ou treinamentos, também cobraremos uma taxa Retome o tempoExemplos de projetos com placas:1. Interface entre o MIPSfpga e sensores com interfaces SPI, I2C, UART e outros. Sensores de umidade, temperatura, som, bússolas, telêmetro, etc.2. A interface entre o MIPSfpga e o externo em relação à memória FPGA - SDRAM, DDR, etc. (nos exemplos atuais, a memória do sistema é construída a partir da memória em bloco dentro do FPGA)3. A interface entre o MIPSfpga e dispositivos maiores é um monitor VGA, mouse, teclado, joystick.4. Visualização do cache executando o processador a uma frequência de 1 relógio por segundo e emitindo sinais relacionados à transação (solicitação, falha, etc.).5. Visualização da operação do transportador e dos dispositivos aritméticos, iniciando o processador com uma frequência de 1 relógio por segundo e emitindo sinais de controle do transportador, etc.6. Adicionando comandos ao processador usando a interface CorExtend / Instruções Definidas pelo Usuário (UDI). Um exemplo são comandos especiais de criptografia.7. Trabalho de laboratório com uma demonstração da operação de interrupção em diferentes modos e um manipulador de interrupção.8. Pontes entre o ônibus AHB-Lite e outros ônibus - AXI, APB, OCP, Wishbone, PLB, etc.9. Sistemas multiprocessadores sem a coerência de caches de primeiro nível e (para os mais avançados) com caches coerentes e implementação de protocolos como o MESI.10. Portando para o MIPSfpga vários programas e sistemas operacionais - do RTOS simples a várias variantes do Linux (o MIPSfpga suporta TLB MMU).Envie sugestões para yuri.panchul@imgtec.com com uma cópia de yuri@panchul.com

Source: https://habr.com/ru/post/pt387803/

All Articles