Tecnologia de Flash NAND 3D

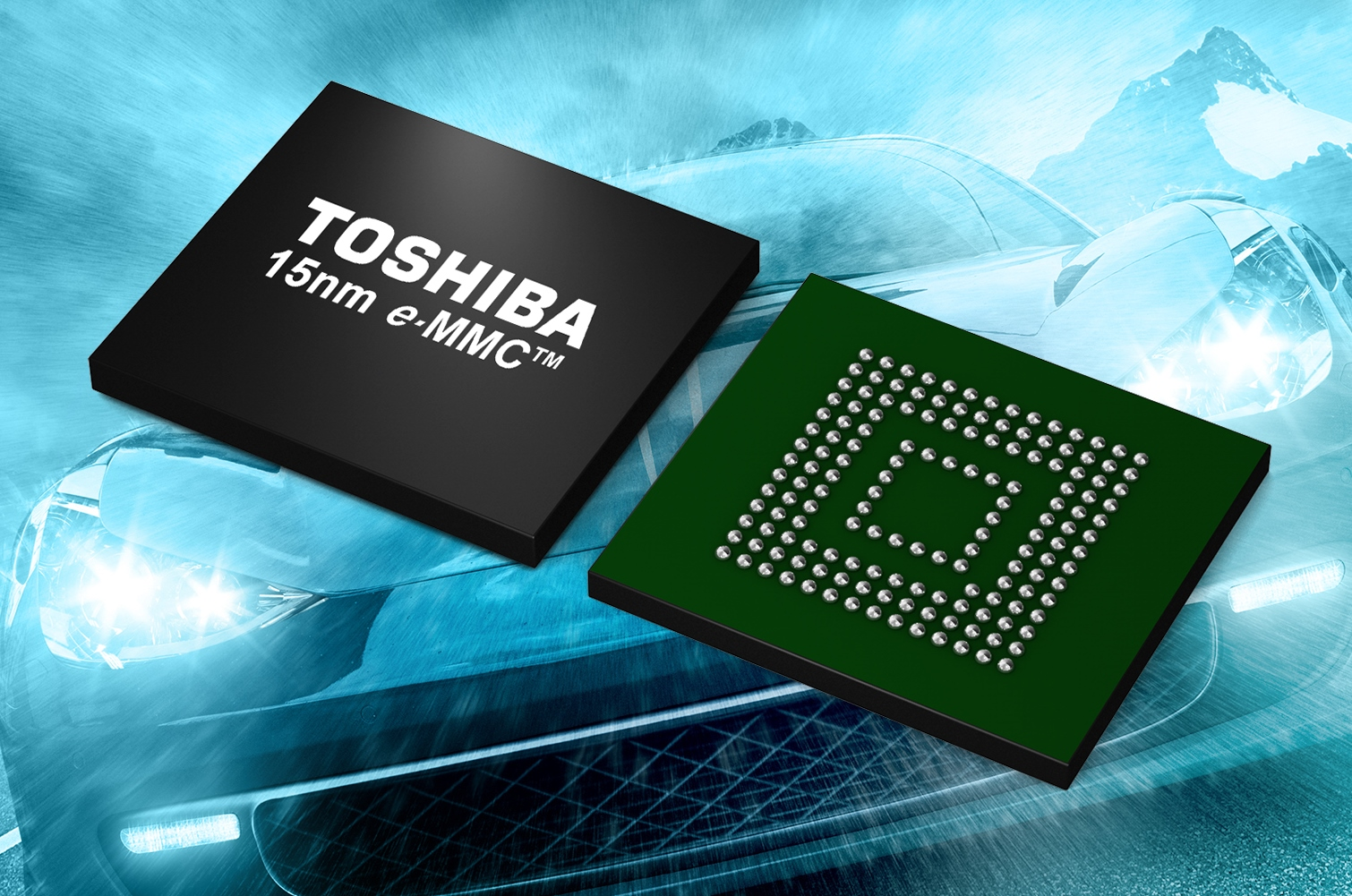

Olá pessoal! Como você sabe, a moderna memória flash planar da NAND quase esgotou seu potencial. Seu principal problema é que fica cada vez mais difícil reduzir o tamanho do cristal. Segundo especialistas, os padrões tecnológicos de 14 a 15 nm se tornarão o limite da memória flash plana, pelo menos em um futuro próximo. E será substituído pela tecnologia da memória flash "vertical" - 3D NAND.É muito importante entender o que impede a redução adicional do tamanho do cristal. Antes de tudo, o desenvolvimento de processos de fabricação mais refinados requer equipamentos caros, cuja compra pode não ser justificada no futuro do ponto de vista econômico. E se a aquisição de novas máquinas litográficas é um problema solucionável, então o problema do fluxo de carga de uma célula para outra, devido a quais erros ocorrem, não é tão fácil de resolver.

Source: https://habr.com/ru/post/pt391899/

All Articles