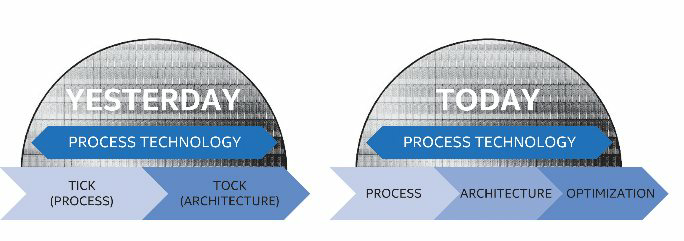

Intel abandona estratégia de tick-to-tack

Agora os processadores farão o ciclo "processo-arquitetura-otimização"

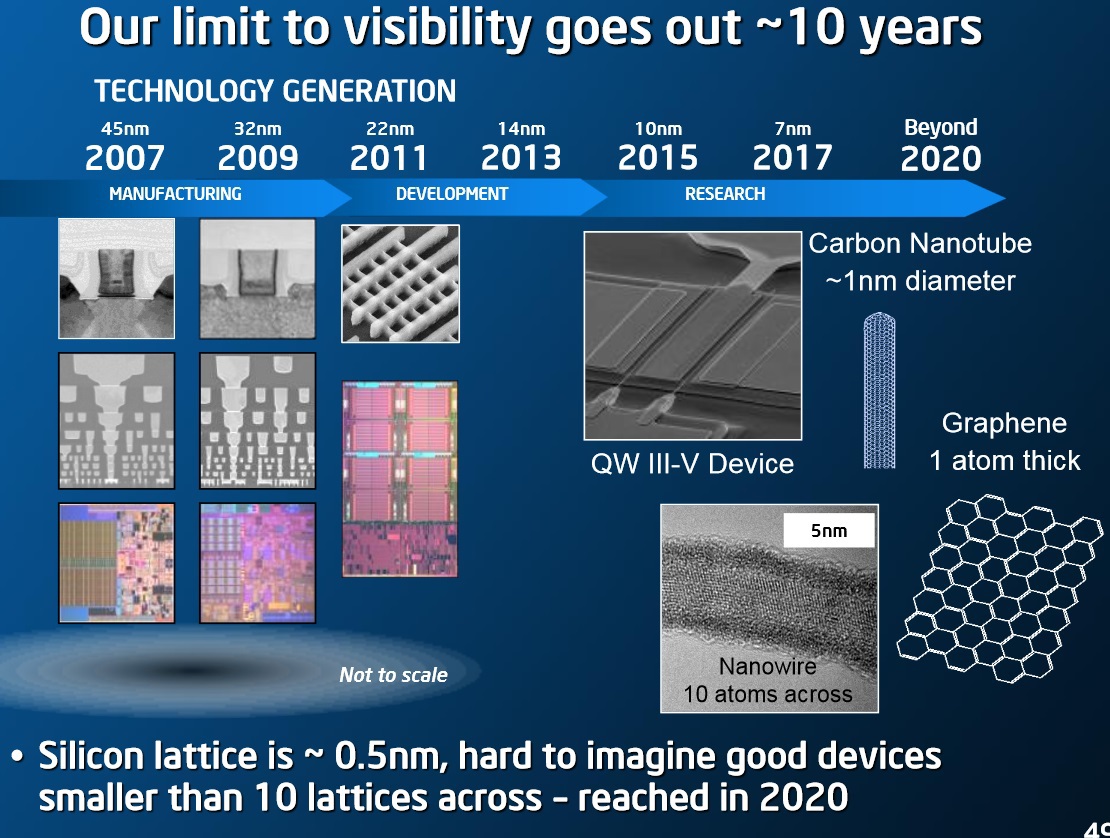

Como uma empresa pública com mais de US $ 10 milhões em ativos, ações detidas por mais de 500 acionistas, a Intel forneceu à Comissão com a Securities and Exchange Commission relatório anual no Formulário 10 da K- . De particular interesse no documento de 150 páginas é a página 14, na qual a Intel reconhece que está abandonando a estratégia de marcação a tachinha em favor do novo conceito de otimização da arquitetura de processo.O Tick-Tock é um modelo de desenvolvimento de microprocessador que a Intel usa desde 2007. Em certos intervalos, a tecnologia permite reduzir o tamanho dos elementos na placa, o que reduz o consumo de energia e encaixa um número maior de transistores em um chip do mesmo tamanho. Se for possível ajustar mais elementos, é possível uma nova microarquitetura: novos comandos são adicionados, a lógica do trabalho melhora, o número de diferentes elementos aumenta.A estratégia de tick-to-tack divide os dois processos. Sobre o "tick" transistores tornam-se menores. Há mudanças na microarquitetura, mas são insignificantes. “Então” significa a criação de uma nova microarquitetura, ou seja, grandes mudanças, às vezes fundamentais, para obter grandes ganhos de produtividade.A Intel vem adotando essas medidas há quase 10 anos. Cada um deles leva de um ano a um ano e meio. Mas, recentemente, tornou-se cada vez mais difícil reduzir o processo de fabricação. Ao mudar de 22 para 14 nanômetros , atrasos de 6 a 9 meses apareceram. Nesse momento, era necessário aumentar a porcentagem de produção de chips viáveis das bolachas para um nível aceitável ao custo. A lei de Moore, que descreve a duplicação do número de transistores em um chip a cada 24 meses, deve ser ajustada.No futuro, está planejado fazer a transição para 10 e depois para 7 e 5 nanômetros. Atingir novas fronteiras significa o possível uso da litografia em ultravioleta profundo, SAQP, rejeição de silício em favor de semicondutores III-V, nanotubos de carbono e grafeno.

Como uma empresa pública com mais de US $ 10 milhões em ativos, ações detidas por mais de 500 acionistas, a Intel forneceu à Comissão com a Securities and Exchange Commission relatório anual no Formulário 10 da K- . De particular interesse no documento de 150 páginas é a página 14, na qual a Intel reconhece que está abandonando a estratégia de marcação a tachinha em favor do novo conceito de otimização da arquitetura de processo.O Tick-Tock é um modelo de desenvolvimento de microprocessador que a Intel usa desde 2007. Em certos intervalos, a tecnologia permite reduzir o tamanho dos elementos na placa, o que reduz o consumo de energia e encaixa um número maior de transistores em um chip do mesmo tamanho. Se for possível ajustar mais elementos, é possível uma nova microarquitetura: novos comandos são adicionados, a lógica do trabalho melhora, o número de diferentes elementos aumenta.A estratégia de tick-to-tack divide os dois processos. Sobre o "tick" transistores tornam-se menores. Há mudanças na microarquitetura, mas são insignificantes. “Então” significa a criação de uma nova microarquitetura, ou seja, grandes mudanças, às vezes fundamentais, para obter grandes ganhos de produtividade.A Intel vem adotando essas medidas há quase 10 anos. Cada um deles leva de um ano a um ano e meio. Mas, recentemente, tornou-se cada vez mais difícil reduzir o processo de fabricação. Ao mudar de 22 para 14 nanômetros , atrasos de 6 a 9 meses apareceram. Nesse momento, era necessário aumentar a porcentagem de produção de chips viáveis das bolachas para um nível aceitável ao custo. A lei de Moore, que descreve a duplicação do número de transistores em um chip a cada 24 meses, deve ser ajustada.No futuro, está planejado fazer a transição para 10 e depois para 7 e 5 nanômetros. Atingir novas fronteiras significa o possível uso da litografia em ultravioleta profundo, SAQP, rejeição de silício em favor de semicondutores III-V, nanotubos de carbono e grafeno. Slide da apresentação de um ano atrás .Um documento da Comissão de Valores Mobiliários aborda o curso geral de desenvolvimento da Intel. A empresa explica que o tempo total de uso do produto para a tecnologia de processo atual será aumentado para 14 nanômetros e o futuro para 10 nm. Mas o ritmo do mercado de lançamentos de novos produtos continuará. Como isso será alcançado? A Intel fornece a imagem, que nesta postagem é publicada antes do kat. Nele, o “tick-tock” é chamado de tecnologia de ontem, e o ciclo de três etapas, “processo-arquitetura-otimização” (PAO), é declarada a realidade atual.Broadwell, o seguidor do Haswell de 22 nm, ajudou a calcular 14 nanômetros. A microarquitetura atual da Intel é a Skylake, a sexta geração do Core, a tecnologia de processo "so" de 14nm. Seu seguidor, Kaby Lake, também terá 14 nm, mas fornecerá "melhorias significativas de desempenho em relação à família de processadores Core de sexta geração".Atingir 10 nanômetros pode ser ajudado pela colaboração mencionada no documento com a ASML no estudo da fotolitografia em ultravioleta profundo, incluindo o aplicável a chapas com diâmetros de 300 e 450 milímetros. A Intel ainda mantém a liderança: 14 nm foram introduzidos em agosto de 2014, Samsung e TSMC se recuperaram mais tarde.Espera-se que o lago Kaby de 14 nm seja lançado este ano. De acordo com os planos atuais, os produtos da microarquitetura Cannonlake de 10 nanômetros devem aparecer em 2017. No ciclo de três etapas, é fácil ver vantagens óbvias para o usuário final: a mesma placa-mãe pode ser adequada para produtos de duas ou mais gerações.

Slide da apresentação de um ano atrás .Um documento da Comissão de Valores Mobiliários aborda o curso geral de desenvolvimento da Intel. A empresa explica que o tempo total de uso do produto para a tecnologia de processo atual será aumentado para 14 nanômetros e o futuro para 10 nm. Mas o ritmo do mercado de lançamentos de novos produtos continuará. Como isso será alcançado? A Intel fornece a imagem, que nesta postagem é publicada antes do kat. Nele, o “tick-tock” é chamado de tecnologia de ontem, e o ciclo de três etapas, “processo-arquitetura-otimização” (PAO), é declarada a realidade atual.Broadwell, o seguidor do Haswell de 22 nm, ajudou a calcular 14 nanômetros. A microarquitetura atual da Intel é a Skylake, a sexta geração do Core, a tecnologia de processo "so" de 14nm. Seu seguidor, Kaby Lake, também terá 14 nm, mas fornecerá "melhorias significativas de desempenho em relação à família de processadores Core de sexta geração".Atingir 10 nanômetros pode ser ajudado pela colaboração mencionada no documento com a ASML no estudo da fotolitografia em ultravioleta profundo, incluindo o aplicável a chapas com diâmetros de 300 e 450 milímetros. A Intel ainda mantém a liderança: 14 nm foram introduzidos em agosto de 2014, Samsung e TSMC se recuperaram mais tarde.Espera-se que o lago Kaby de 14 nm seja lançado este ano. De acordo com os planos atuais, os produtos da microarquitetura Cannonlake de 10 nanômetros devem aparecer em 2017. No ciclo de três etapas, é fácil ver vantagens óbvias para o usuário final: a mesma placa-mãe pode ser adequada para produtos de duas ou mais gerações.Source: https://habr.com/ru/post/pt392041/

All Articles