Pesquisadores da Intel e da Universidade da Carolina do Norte aceleram a troca de dados entre os núcleos da CPU em 2 a 12 vezes

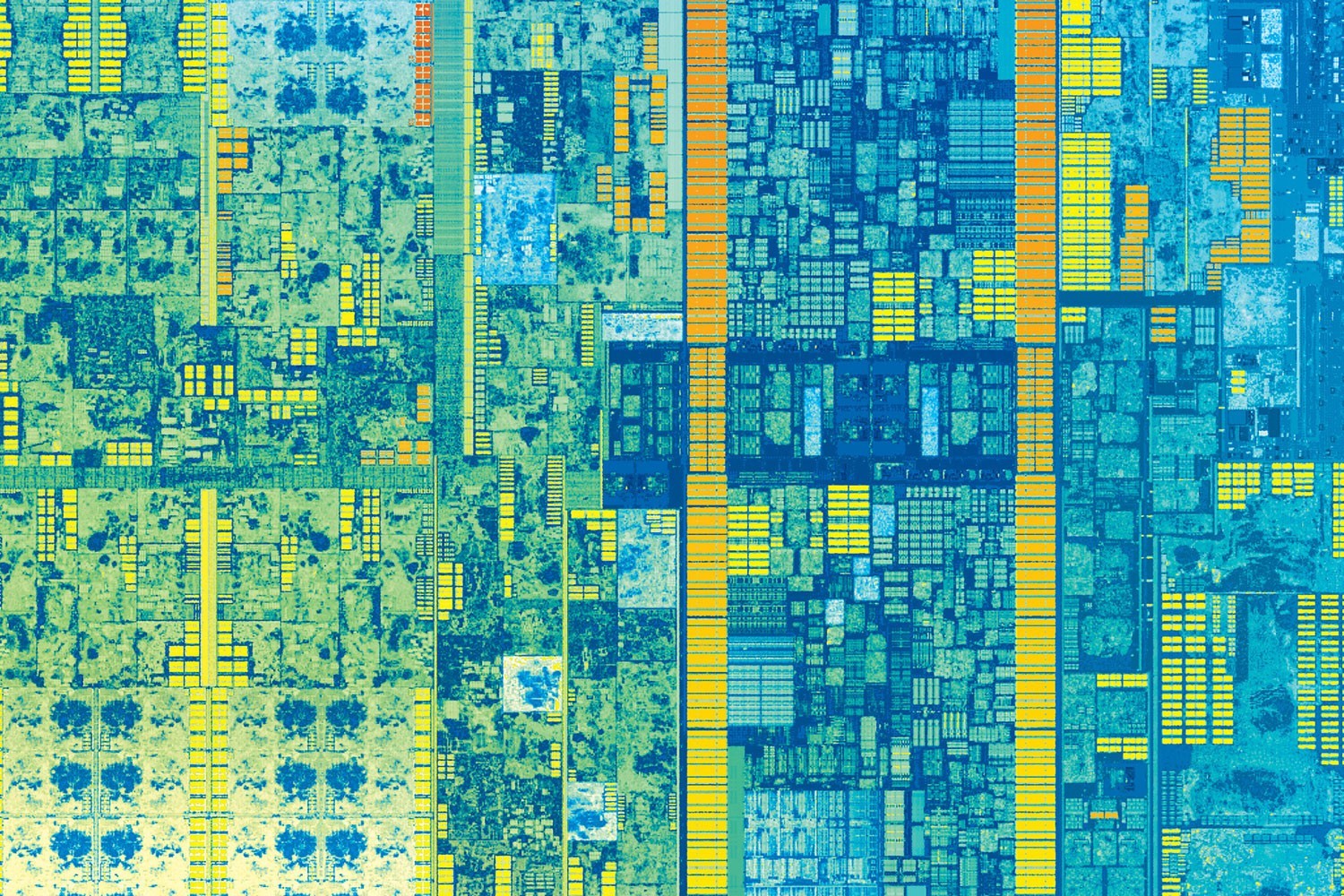

A topologia da sétima geração de processadores Intel Core (anteriormente denominada codinome Kaby Lake), que estará disponível no final de 2016. Foto: IntelUm grupo de pesquisadores da Universidade da Carolina do Norte e da Intel desenvolveu a tecnologia CAF (Core to Core Communication Acceleration Framework) , que pode acelerar significativamente a troca de dados entre os núcleos dos processadores. Ao eliminar esse gargalo, os fabricantes finalmente poderão aumentar o número de núcleos na CPU sem um aumento exponencial no tráfego de serviço entre eles.Na implementação de programas paralelos, o mais difícil é garantir a coordenação correta dos recursos compartilhados entre os processos. Nos processadores modernos, a sincronização da interação paralela entre os núcleos é realizada por dois métodos: usando a passagem de mensagens e a memória compartilhada.No primeiro caso, um processo de thread único é iniciado em cada núcleo, que troca dados com outros processos em execução em outros kernels.Ao interagir através da memória compartilhada em cada processador de um sistema multiprocessador, o encadeamento de execução que pertence a um processo é iniciado. Os fluxos trocam dados através de uma parte da memória comum a esse processo. O número de threads corresponde ao número de processadores.Pesquisadores propõem implementar essa coordenação de recursosno nível do hardware . No resumo do trabalho científico preparado, eles observam que “a interação através da memória compartilhada, por sua natureza, inclui deficiências para manter falhas de coerência e cache, o que aumenta muito a sobrecarga e cria uma grande quantidade de tráfego de rede [excessivo]”.Muitas tarefas importantes exigem uma grande troca de tráfego entre os núcleos; portanto, um aumento significativo na sobrecarga custa um enorme impacto no desempenho. Isso também se aplica ao desempenho do pipeline de computação, amplamente utilizado em soluções de software para a operação de paralelismo no nível de comando.A aceleração de hardware coordena o trabalho dos núcleos na computação paralela. A coordenação principal do hardware proposta é muito mais eficiente do que qualquer método de sincronização de software atualmente em uso."Essa abordagem, que chamamos de estrutura CAF para acelerar a comunicação entre os núcleos , melhora a transferência de dados de 2 a 12 vezes", disse Yan Solihin, professor de engenharia elétrica e de computadores da Universidade da Carolina do Norte e co-autor de pesquisas. "Em outras palavras, a velocidade de execução - do início ao fim - é pelo menos duas vezes mais rápida."No trabalho científico preparado, os autores realizaram uma análise da sobrecarga (tráfego excessivo de rede entre os núcleos), que ocorre ao sincronizar cálculos paralelos com os métodos de software existentes. E eles propuseram uma solução alternativa.Um elemento chave da nova estrutura é o módulo de hardware de gerenciamento de fila do Dispositivo de Gerenciamento de Fila (QMD). Ele é capaz de executar funções simples de computação e está conectado por hardware ao subsistema de comunicação, ou seja, ao NoC (rede em um chip - uma mini-Internet dentro do processador ).

A topologia da sétima geração de processadores Intel Core (anteriormente denominada codinome Kaby Lake), que estará disponível no final de 2016. Foto: IntelUm grupo de pesquisadores da Universidade da Carolina do Norte e da Intel desenvolveu a tecnologia CAF (Core to Core Communication Acceleration Framework) , que pode acelerar significativamente a troca de dados entre os núcleos dos processadores. Ao eliminar esse gargalo, os fabricantes finalmente poderão aumentar o número de núcleos na CPU sem um aumento exponencial no tráfego de serviço entre eles.Na implementação de programas paralelos, o mais difícil é garantir a coordenação correta dos recursos compartilhados entre os processos. Nos processadores modernos, a sincronização da interação paralela entre os núcleos é realizada por dois métodos: usando a passagem de mensagens e a memória compartilhada.No primeiro caso, um processo de thread único é iniciado em cada núcleo, que troca dados com outros processos em execução em outros kernels.Ao interagir através da memória compartilhada em cada processador de um sistema multiprocessador, o encadeamento de execução que pertence a um processo é iniciado. Os fluxos trocam dados através de uma parte da memória comum a esse processo. O número de threads corresponde ao número de processadores.Pesquisadores propõem implementar essa coordenação de recursosno nível do hardware . No resumo do trabalho científico preparado, eles observam que “a interação através da memória compartilhada, por sua natureza, inclui deficiências para manter falhas de coerência e cache, o que aumenta muito a sobrecarga e cria uma grande quantidade de tráfego de rede [excessivo]”.Muitas tarefas importantes exigem uma grande troca de tráfego entre os núcleos; portanto, um aumento significativo na sobrecarga custa um enorme impacto no desempenho. Isso também se aplica ao desempenho do pipeline de computação, amplamente utilizado em soluções de software para a operação de paralelismo no nível de comando.A aceleração de hardware coordena o trabalho dos núcleos na computação paralela. A coordenação principal do hardware proposta é muito mais eficiente do que qualquer método de sincronização de software atualmente em uso."Essa abordagem, que chamamos de estrutura CAF para acelerar a comunicação entre os núcleos , melhora a transferência de dados de 2 a 12 vezes", disse Yan Solihin, professor de engenharia elétrica e de computadores da Universidade da Carolina do Norte e co-autor de pesquisas. "Em outras palavras, a velocidade de execução - do início ao fim - é pelo menos duas vezes mais rápida."No trabalho científico preparado, os autores realizaram uma análise da sobrecarga (tráfego excessivo de rede entre os núcleos), que ocorre ao sincronizar cálculos paralelos com os métodos de software existentes. E eles propuseram uma solução alternativa.Um elemento chave da nova estrutura é o módulo de hardware de gerenciamento de fila do Dispositivo de Gerenciamento de Fila (QMD). Ele é capaz de executar funções simples de computação e está conectado por hardware ao subsistema de comunicação, ou seja, ao NoC (rede em um chip - uma mini-Internet dentro do processador ). Ilustração do artigo " Rede em um chip - mini-Internet dentro do processador "O módulo QMD assume a tarefa de gerenciar a fila e sincronizar a interação paralela dos núcleos, sem nenhuma instrução de software adicional nos núcleos da CPU. É como um roteador de hardware em uma rede.O desenvolvimento futuro é importante à luz do aumento constante de núcleos nos processadores modernos. Este é um processo completamente natural, pois a velocidade do relógio quase parou devido a limitações físicas naturais. Os fabricantes não têm escolha senão paralelizar os cálculos.Sob tais condições, a sincronização da interação paralela entre os núcleos se torna o gargalo que limita o desempenho do sistema. Com o roteamento de tráfego eficiente entre os núcleos do processador, você pode continuar a escalar a arquitetura da CPU e criar processadores com dezenas ou centenas de núcleos com escala de desempenho quase linear. O roteamento de tráfego eficiente entre os núcleos é uma tecnologia essencial necessária para ampliar ainda mais a arquitetura da CPU multinúcleo.Além de acelerar repetidamente a troca de dados entre núcleos enquanto sincroniza a computação paralela, o módulo QMD pode ser útil na agregação de dados de vários núcleos. Os pesquisadores acreditam que isso acelerará o processamento de algumas operações básicas de computação em até 15%.O trabalho científico " CAF: estrutura de aceleração de comunicação de núcleo para núcleo " será apresentado na 25ª conferência sobre arquiteturas paralelas e métodos de compilação PACT '16 , que será realizada de 11 a 15 de setembro de 2016 em Haifa (Israel).Os inventores são Yipeng Wang (Universidade da Carolina do Norte), Ren Wang, Andrew Herdrich e James Tsai (todos Intel Corp.), e o principal autor do artigo é o mencionado. Yan Solihin, da Universidade da Carolina do Norte e da Fundação Nacional de Ciência dos EUA.O artigo foi incluído nos Anais da Conferência Internacional de Arquitetura e Compilação Paralela de 2016, p. 351-362, doi: 10.1145 / 2967938.2967954. É provável que a coleção de relatórios seja distribuída aos participantes da conferência e publicada na Internet.

Ilustração do artigo " Rede em um chip - mini-Internet dentro do processador "O módulo QMD assume a tarefa de gerenciar a fila e sincronizar a interação paralela dos núcleos, sem nenhuma instrução de software adicional nos núcleos da CPU. É como um roteador de hardware em uma rede.O desenvolvimento futuro é importante à luz do aumento constante de núcleos nos processadores modernos. Este é um processo completamente natural, pois a velocidade do relógio quase parou devido a limitações físicas naturais. Os fabricantes não têm escolha senão paralelizar os cálculos.Sob tais condições, a sincronização da interação paralela entre os núcleos se torna o gargalo que limita o desempenho do sistema. Com o roteamento de tráfego eficiente entre os núcleos do processador, você pode continuar a escalar a arquitetura da CPU e criar processadores com dezenas ou centenas de núcleos com escala de desempenho quase linear. O roteamento de tráfego eficiente entre os núcleos é uma tecnologia essencial necessária para ampliar ainda mais a arquitetura da CPU multinúcleo.Além de acelerar repetidamente a troca de dados entre núcleos enquanto sincroniza a computação paralela, o módulo QMD pode ser útil na agregação de dados de vários núcleos. Os pesquisadores acreditam que isso acelerará o processamento de algumas operações básicas de computação em até 15%.O trabalho científico " CAF: estrutura de aceleração de comunicação de núcleo para núcleo " será apresentado na 25ª conferência sobre arquiteturas paralelas e métodos de compilação PACT '16 , que será realizada de 11 a 15 de setembro de 2016 em Haifa (Israel).Os inventores são Yipeng Wang (Universidade da Carolina do Norte), Ren Wang, Andrew Herdrich e James Tsai (todos Intel Corp.), e o principal autor do artigo é o mencionado. Yan Solihin, da Universidade da Carolina do Norte e da Fundação Nacional de Ciência dos EUA.O artigo foi incluído nos Anais da Conferência Internacional de Arquitetura e Compilação Paralela de 2016, p. 351-362, doi: 10.1145 / 2967938.2967954. É provável que a coleção de relatórios seja distribuída aos participantes da conferência e publicada na Internet.Source: https://habr.com/ru/post/pt397275/

All Articles