Continuamos a revisar o rastreamento de PCB. Publico este artigo da minha cidade natal, Severodvinsk, com agradecimentos aos meus professores. O tópico ao qual é dedicado é básico e, portanto, é importante lidar com ele. Aqui, as reflexões nas linhas de sinal serão consideradas e, como sempre, serão fornecidas recomendações para reduzir a distorção do sinal, incluindo o uso de várias técnicas de correspondência de linha.

Em um artigo

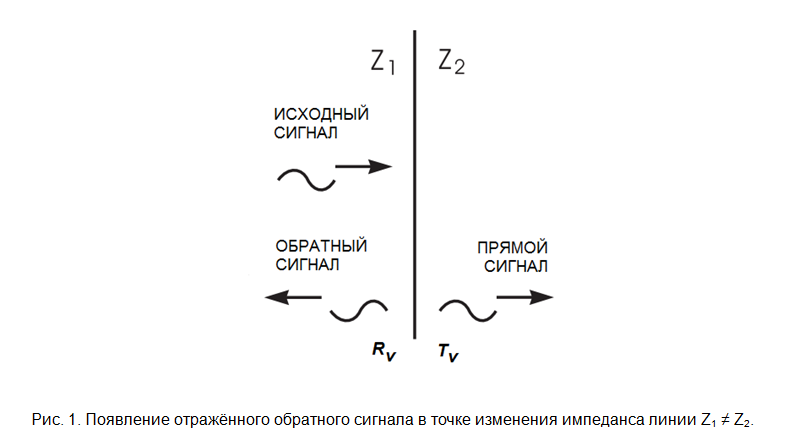

anterior do ciclo, foi demonstrado que a presença de cortes no caminho da corrente de retorno aumenta a indutância do circuito de sinal, o que afeta negativamente o nível de EMR da placa de circuito impresso. No entanto, seu impacto negativo não termina aí (vale ressaltar que há situações em que o uso de recortes na camada de referência reduz o nível de EMR da placa de circuito impresso, no entanto, eles exigem grande precisão do ponto de vista do controle de correntes de retorno e não podem ser recomendados no caso geral). Um recorte, como outras não homogeneidades (furo de transição, ramificação da faixa, alteração na largura ou distância da faixa da camada de referência, etc.) altera o valor local da impedância (impedância instantânea em inglês) da linha de sinal. Qualquer alteração na impedância no curso da propagação do sinal leva a uma alteração na sua amplitude e ao aparecimento de um sinal refletido que se propaga de volta à fonte (Fig. 1).

As amplitudes dos sinais de avanço e reverso em relação à fonte são determinadas apenas pelos valores das impedâncias Z

1 e Z

2 em uma determinada frequência:

Um sinal de menos na frente dos coeficientes indicará uma mudança na fase do sinal em 180

° . Mesmo que a linha de sinal seja homogênea (a seguir, a uniformidade da linha significa a constância dos parâmetros geométricos de sua seção transversal) ao longo de todo o seu comprimento, e sua impedância é constante e é denominada impedância característica, os reflexos podem ocorrer não apenas na própria linha, mas e nas extremidades - no lado da fonte ou no lado da carga. Considere um circuito simples (Fig. 2), no qual as resistências da fonte de sinal e da carga não são consistentes com a impedância de onda de uma linha homogênea. Nesse caso, os reflexos na linha ocorrem repetidamente, gradualmente desaparecendo e levando a um padrão de interferência - a soma dos sinais. O padrão dos sinais refletidos e a simulação resultam em LTSpice para um sinal de pulso passo a passo com uma amplitude de 1,2 V e uma borda principal de 1 ns também são mostrados na figura.

Observe que a tensão na entrada da linha de sinal durante o tempo de propagação do sinal (até a primeira reflexão) não é igual à tensão da fonte de sinal V

S e está associada a ela pelo coeficiente do divisor resistivo

Após várias reflexões das extremidades das linhas, o valor da tensão na carga tende à soma da progressão geométrica decrescente igual à tensão no braço inferior do divisor resistivo

Como em condições reais é impossível garantir a constância da impedância ao longo do caminho de propagação do sinal, as reflexões sempre ocorrem. A questão é sob quais condições eles levam a uma distorção perceptível do sinal. Consideramos novamente um exemplo do circuito mostrado na Fig. 2, fixando os valores da resistência da fonte de sinal, carga e impedância de onda da linha. Portanto, as amplitudes dos sinais interferentes incluídos na soma também são preservadas. No entanto, além das amplitudes dos sinais A1

, o valor da soma depende de seus deslocamentos de tempo τ

i :

onde TD é o tempo de propagação do sinal na linha ou o atraso da linha (atraso da linha de transmissão em inglês). Este valor é determinado pelo comprimento L da linha do sinal e pela velocidade de propagação v do sinal na linha TD = L / v. Reduziremos o atraso de tempo da linha - enquanto a duração das "prateleiras", quando o valor do sinal for constante, também diminuirá. E quando o sinal refletido i + 1st chega à carga imediatamente após o sinal i atingir seu valor de amplitude, as prateleiras desaparecem. Como o sinal atinge seu valor de amplitude em um tempo igual à duração da frente tR, deve-se fazer o seguinte:

Uma diminuição adicional no atraso de tempo levará ao fato de que os valores de amplitude da ondulação (toque em inglês) não serão alcançados. No caso limitante da linha infinitamente curta TD → 0, o transiente oscilatório está ausente. Daí a conclusão sobre a necessidade de minimizar o comprimento da linha para sinais críticos, já mencionados em um artigo

anterior em conexão com uma diminuição na indutância. Obviamente, as linhas de sinal reais em uma placa de circuito impresso têm um comprimento finito; portanto, a condição TD << tR é um critério matemático para uma pequena ondulação.

R.1

Uma condição prática para pequenas distorções de um sinal de pulso com uma duração frontal tR em uma linha de sinal com um atraso de tempo TD é TD <1/5 R. t R. Para estimar o comprimento da linha de sinal, podemos tomar v ≈ 15 cm / ns (para FR4), então a condição pode ser reescrita como L [cm] <3 ∙ t R [ns].

É importante entender que o grau aceitável de distorção deve ser determinado pelo projetista da placa de circuito impresso ou esse parâmetro deve ser especificado como restritivo. Além disso, a amplitude da ondulação depende não apenas da relação entre tR e TD, mas também do grau de incompatibilidade de linha. Na recomendação dada, pequenas distorções são entendidas como pulsações, cuja amplitude não excede cerca de ± 10%. Se a condição tR> 5 ∙ TD não for satisfeita ou se o requisito de pulsação for mais rigoroso, existem três maneiras de reduzir o fenômeno de ressonância na linha:

- diminuição no TD (principalmente devido à diminuição no comprimento da linha),

- aumento de tR (diminuição da velocidade de comutação do sinal),

- coordenação de linha (terminação em inglês).

O objetivo de todos os métodos de correspondência de linhas (tabela 1) é garantir que não haja reflexos em uma ou nas duas extremidades. Nenhum dos métodos é ideal - cada um deles tem seus prós e contras, enquanto absolutamente todos os métodos levam a perdas de energia adicionais. Portanto, não é recomendável recorrer à correspondência de linha antes que o comprimento mínimo possível da linha e a velocidade de comutação do sinal sejam fornecidos.

Tabela 1. Métodos de correspondência de linha de sinal.

| Título e esquema | Taxa de perda | Comentários |

|---|

| baixo |  |

| alto |  |

| média |  |

| média |  |

Notas:

(1) Em um circuito paralelo, pode ser usada uma conexão a um fio comum e a uma fonte de alimentação.

(2) Por otimização entende-se um critério para minimizar as perdas de energia.

No caso em que a linha de sinal conecta a fonte de sinal a uma única carga (ponto a ponto), pode ser usada a correspondência de impedâncias no lado da fonte e no lado da carga. Se houver várias cargas na linha de sinal (inglês multiload), é recomendável aplicar a coordenação no lado da carga. Exemplos de esquemas em que a ausência de distorção de sinal é sempre crítica, muito - um circuito de relógio distribuído, um barramento de dados multiponto, a organização da memória externa com vários microcircuitos, etc. . A vantagem de ramificações curtas é que elas podem não ter componentes correspondentes no final; no entanto, há uma restrição no comprimento.

R.2

Ramos curtos da linha de sinal podem ser inconsistentes, mas seu comprimento deve ser mínimo e não deve exceder o valor em que TD STUB 1/5 ∙ t R.

Três padrões principais de ramificação da linha de sinal em seções N são mostrados na Fig. 3. Um circuito com uma seção curta (o mesmo critério de uma ramificação) antes da ramificação leva a um aumento de carga na fonte de sinal. Se a seção demorar muito antes da ramificação, é necessário aumentar a impedância dos galhos. Um aumento na resistência da onda da linha de sinal na mesma camada exigirá uma diminuição em sua largura, o que pode se tornar uma limitação. Se você usar um resistor em série com a resistência R = (N - 1) ∙ Z

0 , ele formará um divisor de tensão - e a amplitude do sinal na carga diminuirá V

LOAD = 1 / N ∙ V

IN . Obviamente, cada um dos esquemas não apresenta desvantagens (além de aumentar o número de componentes utilizados); portanto, recomenda-se que a topologia com ramificação (topologia em estrela) seja usada apenas ao usar uma topologia com uma linha de sinal principal e ramificações curtas (eng. topologia daizy-chain) não é possível.

Em conclusão, deve-se notar que a escolha do método de correspondência de linha de sinal está intimamente relacionada ao circuito da placa de circuito impresso; portanto, se o desenvolvedor for responsável apenas pela topologia da placa de circuito impresso, a decisão deverá ser tomada em conjunto com o engenheiro de circuito usando modelagem de linha de sinal (SPICE ou software especializado). No entanto, a questão da necessidade de coordenar a linha é sempre iniciada pelo projetista da placa de circuito impresso, se for impossível fornecer o nível de distorção necessário de outras maneiras.

O artigo foi publicado pela primeira vez na revista Components and Technologies 2018, No. 3. A publicação em Habr foi acordada com os editores da revista.