Em cada artigo sobre Habré dedicado aos microprocessadores domésticos, de uma forma ou de outra, é levantada a questão dos blocos IP licenciados e o quanto sua presença e ausência reduzem o valor, a domesticidade ou a segurança do desenvolvimento. Ao mesmo tempo, muitos comentaristas não entendem muito bem o assunto da discussão, então vamos tentar descobrir como o licenciamento funciona na indústria microeletrônica, o que são bons e maus blocos licenciados e qual é o processo de desenvolvimento de um microcircuito se a maioria dos blocos for comprada nele.

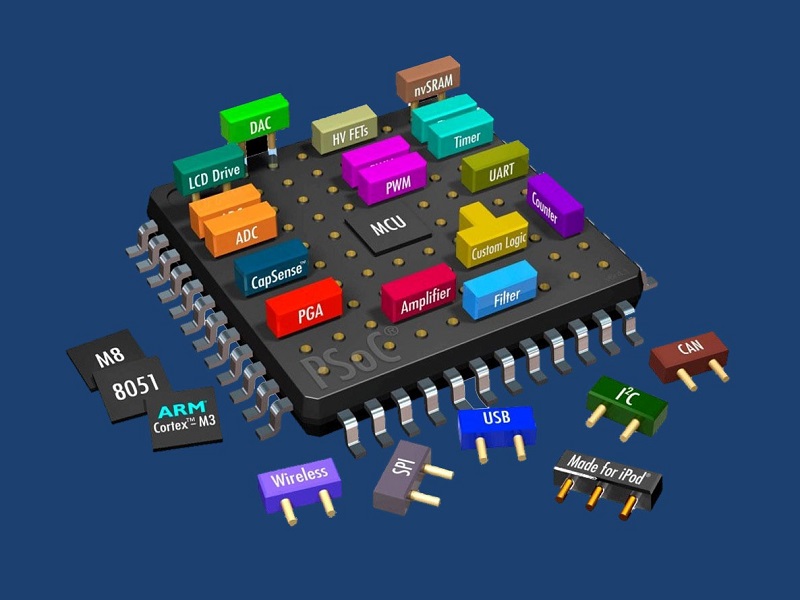

Qualquer microcircuito moderno é o que foi orgulhosamente chamado de "um sistema em um chip" há algum tempo: até mesmo reguladores lineares de três pernas e fontes de tensão têm um ajuste digital oculto ao usuário, o que podemos dizer sobre microprocessadores e microcontroladores contendo dezenas de blocos diferentes, o desenvolvimento de cada dos quais requer habilidades específicas e vasta experiência para contornar armadilhas que não são escritas em livros e artigos. Além disso, qualquer projeto, em regra, tem seu próprio recurso matador, devido ao qual os desenvolvedores esperam obter uma vantagem sobre os concorrentes, e é esse recurso matador que deve ser feito da melhor maneira possível, e todos os outros blocos simplesmente não devem ser piores que outros.

Atenção, a pergunta é: é necessário manter uma equipe de desenvolvimento dispendiosa que possa, de forma independente, criar todos os blocos necessários por conta própria?

Uma pergunta ainda mais interessante: se você mesmo desenvolveu um sistema de instruções de microprocessador, precisa conter uma equipe de programadores que

escreverá um compilador para ele , portar novos kernels de sistemas operacionais populares, realizar muitos outros trabalhos árduos e, provavelmente, não criará sua criação em um no nível das arquiteturas populares, nas quais muito mais pessoas trabalham?

E o mais importante: as respostas positivas para as duas perguntas anteriores darão vantagens competitivas ao seu produto?

Digressão líricaEm 5 de junho, Morris Chang se aposentou, um homem que você nunca ouvira falar, mas sem o qual não haveria eletrônicos modernos. Morris Chang nasceu na China, no auge da guerra civil que deixou para os Estados Unidos, se formou no MIT e trabalhou por muitos anos na Texas Instruments e na General Instruments. Naqueles anos, parte integrante de qualquer empresa de microeletrônica era sua própria produção, cujo equipamento era várias ordens de magnitude mais barato do que agora, mas, no entanto, era muito caro. Aqui está como o próprio Chang escreveu sobre isso:

Quando eu estava na TI e na General Instrument, vi muitos designers de IC querendo sair e montar seus próprios negócios, mas a única coisa ou a maior coisa que os impediu de deixar essas empresas foi que eles não podiam levantar dinheiro suficiente para formar sua própria empresa. Porque, naquela época, pensava-se que todas as empresas precisavam de fabricação, fabricação de wafer, e essa era a parte com maior capital de uma empresa de semicondutores, de uma empresa de IC. E vi todas aquelas pessoas querendo ir embora, mas sendo interrompidas pela falta de capacidade de levantar muito dinheiro para construir uma fábrica de wafer.

Em 1985, Morris Chang estava prestes a se aposentar, mas aceitou a oferta do governo de Taiwan para trabalhar no Industrial Technology Research Institute, um instituto de pesquisa que deveria ajudar a provocar uma revolução industrial em Taiwan e fechar a lacuna entre a economia desenvolvida e os países desenvolvidos. Em 1987, paralelamente ao seu trabalho na ITRI, Chang criou a TSMC, uma empresa que cresceu no maior fabricante de circuitos integrados do mundo. O modelo de negócios do TSMC foi originalmente baseado no fato de que a empresa não desenvolve nada, mas apenas produz desenvolvimentos de outras pessoas, e esse foi um dos primeiros passos na criação de um ecossistema moderno para o desenvolvimento e produção de microcircuitos, conhecido como modelo Fabless.

O fim da digressão líricaO que é Fabless?

O Fabless é um modelo para o desenvolvimento e produção de microcircuitos nos quais a empresa desenvolvedora não possui produção própria e utiliza os serviços de uma fábrica de terceiros que também colabora com outros desenvolvedores (e às vezes possui seus próprios produtos).

A presença de fábricas de terceiros pode reduzir radicalmente o limiar de entrada no mercado de microeletrônica (com o qual Morris Chang havia sonhado ao mesmo tempo), de centenas a milhões de dólares, devido à falta de compra e manutenção de equipamentos para produção. Também permite reduzir ainda mais esse limite, devido à formação de um mercado para fornecedores de blocos funcionais complexos (eles também são IP de silício). Se você produz chips em sua própria fábrica, pode confiar apenas em seus próprios pontos fortes e deve conter uma equipe que possa criar todos os blocos necessários. Se a fábrica é usada não apenas por você, mas também por outras empresas, alguém já resolveu a maioria das tarefas típicas antes de você, e você pode usar os resultados do trabalho de outra pessoa - ou revender sua própria solução para outra pessoa, tendo acordado previamente o preço e as condições para que ninguém ficou no perdedor. Obviamente, é improvável que você venda seu conhecimento para direcionar os concorrentes, mas há muitas situações em que você pode ganhar sem se envolver em um conflito de interesses. Estava fora da possibilidade e desejo de reutilizar os resultados da solução de problemas típicos que surgiram o mercado de blocos de IP, cujo tamanho em 2017 era próximo de quatro bilhões de dólares e continua a crescer rapidamente.

Como é rentável?

IP do comprador - principalmente economia. De acordo com várias estimativas, a compra de blocos IP geralmente é duas a cinco vezes mais barata que o autodesenvolvimento. Além disso, a compra geralmente permite reduzir significativamente o tempo de desenvolvimento, pois você não precisa produzir chips de teste e corrigir erros de forma independente.

Para o desenvolvedor de IP - a oportunidade de construir um negócio funcional em uma solução de nicho e reduzir significativamente o custo de fazer negócios. Uma parte significativa do custo do microcircuito é o custo de marketing, embalagem, teste, suporte técnico, software aplicativo e, finalmente, modelos de fotos para produção em massa, etc. etc. Se você não produz produtos acabados, mas apenas vende blocos, não possui todas essas despesas.

Fábrica - uma oportunidade para atrair mais clientes. Grandes fábricas estão se esforçando para criar um ecossistema de fornecedores de blocos IP ao seu redor, porque seu uso pode acelerar significativamente o design e, o mais importante, automatizá-lo o máximo possível. Um rico portfólio de componentes prontos é uma grande ajuda no design do produto final, pois permite que você faça apenas o que é seu conhecimento e não gaste recursos preciosos no desenvolvimento de tudo em geral - especialmente em uma situação em que já exista uma solução pronta desenvolvida por pessoas que investiram em seu desenvolvimento significativamente mais tempo e experiência do que você pode pagar. Assim, uma ampla seleção de IPs prontos pode ser um fator sério na escolha de uma fábrica específica para a produção do seu projeto.

Como isso funciona?

Vejamos o licenciamento de núcleos usando o exemplo de um sistema personalizado esférico em um chip. O sistema conterá um núcleo de processador, barramentos para combinar núcleo e periféricos, uma certa quantidade de memória cache, interfaces para comunicação com o mundo externo (por exemplo, CAN e I2C), PLL, DAC e ADC. Para a pureza do experimento, suponha que tudo será comprado, sem desenvolvimento independente. "Suposição estúpida", você diz, e não estará totalmente certo. Na realidade, é claro, essas situações são extremamente raras, mas ainda é bem possível imaginar que o recurso matador do produto não será um bloco em si, mas uma combinação específica de blocos existentes. Por exemplo, você é o primeiro comprador de um bloco (portanto, os concorrentes ainda não o possuem) ou criou um bloco existente para uso em um segmento não característico para ele (portanto, os concorrentes nesse segmento não têm nada semelhante).

Então, vamos começar com ...

... não, não do núcleo do processador, mas da ligação analógica. Por exemplo, considere o conversor analógico-digital (ADC) - uma unidade típica da maioria dos microcontroladores e de qualquer outro sistema que lide com dados do mundo exterior.

O ADC é um bloco analógico, o que significa que seus parâmetros dependem seriamente não apenas de seu circuito, mas também de como exatamente esse circuito é implementado em um chip. Se pegarmos o arquivo finalizado com a topologia de um processo técnico e o produzirmos em outra fábrica com os mesmos padrões de design, podemos obter parâmetros completamente diferentes (sem mencionar a transferência para outros padrões de design). No entanto, a cultura dos “segundos fornecedores”, conhecida em meados do século, ainda existe; por exemplo, a fábrica de Towerjazz oferece cópias de alguns processos de fabricação do TSMC.

O ADC é um ótimo exemplo de um bloco de IP rígido vinculado a um processo específico. Para comprar essa unidade, você deve saber exatamente em que tecnologia seu produto final será fabricado e, como mencionado acima, a disponibilidade do IP rígido necessário pode ser uma séria vantagem competitiva para a fábrica.

Como é entregue o IP rígido? Essa é uma pergunta interessante e, para respondê-la, é necessário discutir de que forma esse bloco está sendo desenvolvido. No caso da maioria dos blocos analógicos, o desenvolvimento de circuitos é realizado no nível de transistores individuais, ou seja, os arquivos de saída serão o arquivo de circuito elétrico e o arquivo com a topologia. Além disso, os recursos do esquema e da topologia podem ter um valor comercial sério, o que, é claro, eu não quero dar para o lado. E para que o cliente não seja capaz de fazer engenharia reversa do esquema por topologia, a topologia também geralmente não é transmitida; portanto, no caso usual, os arquivos entregues ficam assim:

- Em vez de um circuito elétrico, o cliente recebe um modelo comportamental de alto nível que não divulga os recursos de implementação. Esse modelo pode ser escrito em Verilog-A. Uma alternativa é que alguns sistemas CAD (por exemplo, Cadence Virtuoso) suportem criptografia de circuitos elétricos, ou seja, o cliente poderá usar seu circuito (ou o arquivo verilog-A), mas não poderá abrir e exibir o conteúdo.

- Layout dimensional da topologia, com conclusões externas marcadas e uma descrição de quantos níveis de metalização um bloco ocupa.

- Ambiente de teste para verificação dos principais parâmetros.

- Documentação

Nesse caso, é claro, é necessária a participação de terceiros, para a qual você pode transferir a topologia sem medo de concorrência e engenharia reversa. Esse terceiro é a fábrica, e seu papel intermediário entre clientes e contratados é uma parte importante do ecossistema de desenvolvimento de chips sem fábrica. A fábrica, é claro, deve ter uma reputação clara (trata-se de marcadores) e, idealmente, não deve produzir nada parecido por si só, porque trabalhar em uma fábrica de uma empresa concorrente é, de qualquer forma, um prazer duvidoso. A Samsung consegue produzir processadores ao mesmo tempo para si e para a Apple, mas outras grandes fábricas geralmente se concentram em sua própria produção (como a Intel) ou abandonam completamente o autodesenvolvimento (como a TSMC). O desejo de se livrar desse conflito de interesses, aliás, foi um dos fatores que motivaram a alocação da AMD à Globalfoundries (o segundo maior participante do mercado fabril).

Digressão líricaA propósito, na Rússia, não existem fábricas de peças de reposição na Rússia. Além disso, para absolutamente todos os participantes do mercado, a produção de seus próprios produtos é uma prioridade, e todos os chips domésticos produzidos por desenvolvedores de fábricas são fabricados nas instalações de seus concorrentes em potencial - ou em fábricas no exterior.

O fim da digressão líricaAlém disso, há outro detalhe importante da interação fornecedor-fábrica: a fábrica insere seu bloco IP em seu próprio banco de dados e verifica todos os projetos recebidos quanto à presença de sua topologia (que alguém poderia obter de você e também ilegalmente), e verifique com você se a pessoa que solicita a produção possui uma licença (uma vez que muitas licenças baratas implicam o uso da unidade em apenas um projeto). A presença de uma verificação pela fábrica permite que o desenvolvedor do Hard IP escolha qualquer opção conveniente de licenciamento - vinculada ao número de projetos, ao número de chips vendidos, ao momento de lançar os chips na produção, etc. etc. Mas mais sobre os tipos de licenças na próxima parte.

Como o IP rígido em um sistema típico de um chip, você precisará de ADCs, PLL, camadas físicas de interfaces de E / S.

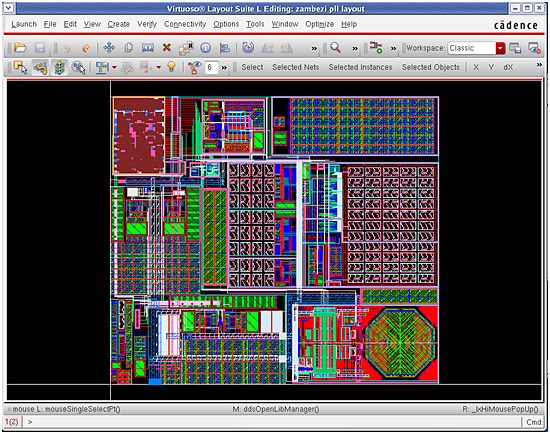

Janela CAD Cadence Virtuoso Layout Suite com a topologia do bloco de IP rígido analógico (este é PLL, se alguém estiver interessado). Os limites entre as subunidades individuais (que geralmente são feitas por pessoas diferentes) e, por exemplo, um elemento muito raro para circuitos integrados - o indutor no canto inferior direito, são claramente visíveis. E no canto superior esquerdo há um bloco digital (provavelmente controle) e sua interface multibits para o resto.

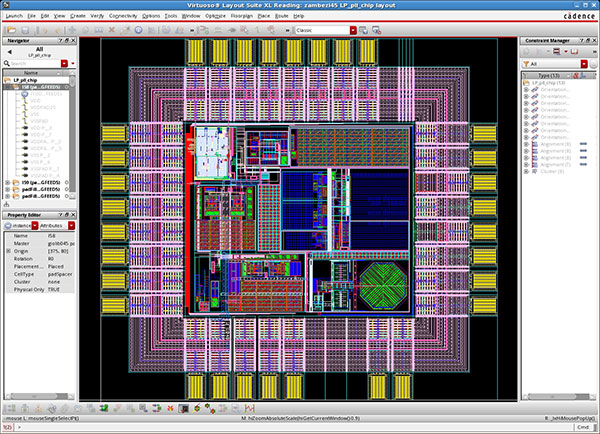

É o mesmo, mas já na forma de um chip pronto (por exemplo, para teste). As almofadas de E / S e os anéis que os conectam das terras e suprimentos são claramente visíveis.

O termo "IP rígido" também é usado em relação aos blocos de IP para FPGAs. Nesse caso, entende-se que o código de bloco foi otimizado para uso em um modelo FPGA específico e sintetizado para colocação nele.

IP suave

O próximo bloco que consideraremos é o núcleo do processador. Na verdade, quase qualquer circuito digital pode estar no seu lugar, por exemplo, uma unidade de codificação de sinal com um código Reed-Solomon, mas os núcleos dos processadores são mais amplamente ouvidos e representam uma boa metade de todo o mercado (inclusive devido à complexidade e ao alto custo).

A principal diferença entre o desenvolvimento de circuitos digitais e o desenvolvimento de circuitos analógicos é que os circuitos digitais geralmente são escritos em linguagens especiais de alto nível - Verilog ou VHDL e, em seguida, um sistema CAD especial sintetiza o circuito elétrico e a topologia desse código. Portanto, até o momento da síntese, o código não está vinculado a uma tecnologia específica e o mesmo bloco pode ser produzido em diferentes fábricas (ou costuradas no FPGA) ou em diferentes versões da mesma tecnologia (por exemplo, otimizadas para alta velocidade ou baixo consumo de energia) . De fato, isso é usado por empresas de desenvolvimento, como, por exemplo, ARM. Esses blocos digitais que não estão vinculados a uma tecnologia específica são chamados de Soft IP.

Aqui está o esquema de um bit de somador:

E aqui está a aparência de um somador de oito bits em um design de chip:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

, , , . , IP- .

Soft IP? :

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation – integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

, — , ( IP ). , . , - -, , .

, LEON3:

- , Cobham Gaisler, LEON3 GPL

- LEON3FT ( ): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

- ( ) , LEON2FT, .

, , Verilog-, . Verilog- , , , , . digital watermarks, , IP.

, “Clean, readable, synthesizable” , , IP . , , , ( , hardware trojans) , , , .

, : soft IP , , ? , Soft IP, , .. .… :

ARM, , , , , ( ), IP , - , , . . (, , , ). Apple Imagination Technology in-house , Apple , Imagination ( ).

, — ( IP ) ( ).

soft IP FPGA, , . , Xilinx IP, ( ) , , ( , ).

, , .

— IP- . , -, . , IP, , IP , , IP ( , ); , - .

— . , ( IP).

— . , , , . — . , , .

— , , (, ARM Cortex). — , .

— . (, , ) , — ( , , ). ? , ( - , , ) . , , , , , — .

? : , , , . , Apple, ARM - , , (, ARM ) — .

: , , , , , , ( — ). , , . , , Apple, , , ! ARM, , Apple . , ARM . , , Apple — PowerPC, , PowerPC x86, Apple Intel.

Soft IP , - , IP . :

- , “ — ”, .

- - IP ( ), IP, IP ( IP hardening) . ? , , , .

soft IP ( ), , , .. ..

Configurable IP

IP, hard soft — , . - , - . ? , IP-? ?

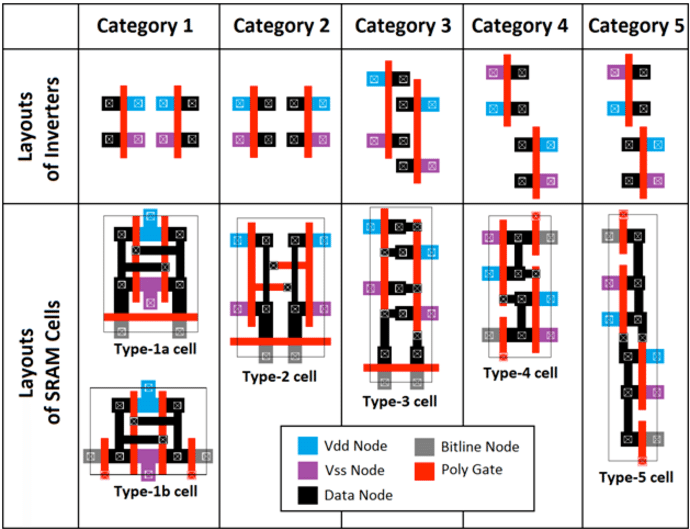

( , FPGA) , , , . , , IP- Hard IP, Soft IP ( , ).

— -.

Foundation IP

«-hard» IP- — foundation IP, . — , . , , , , , . , , ( ) , (, ) . «generic» , , , , , .

Foundation IP -, , , .

BarsMonster .

Verification IP

, , — , . , , , . , , . , - . “”. .

, — Verification IP. — , , ( ). Synopsys , , Synopsys — IP-. IP Design&Reuse Synopsys 828 Silicon IP ( ARC — ARM) 116 Verification IP .

verification IP CAN, ( APB AHB ARM) - . , , , .

?

, , , , ? .

:

- , ( verification IP ).

- — .

- ( , ).

- Soft IP , .

- , , .

- , , .

- , .

- , ( ).

, , ( ). , - , « - BGA 400-700 ». , Hard IP- 400-700 , , , 4-8 (, Soft IP). — ? , . , «-» .

— Synopsys IC Compiler , .

, — , , , , , , .

, , fabless- IP- , , , . , , ( “”) , , : , , , , , , - . , , — .

: Open Source?/ Open Source . , - ( ) , - . , , - . , , .

—

Opencores.org, — OpenRISC, ( FPGA), ASIC ( Samsung). Opencores, , - , ( ARM), FPGA. FPGA Proven, — ASIC Proven.

—

RISC-V. ( OpenPOWER OpenSPARC) , - , , ( ).

RISC-V — , MIPS, , , , ( , MIPS). RISC-V Foundation Google, Samsung, NXP, NVIDIA . , , , , OpenPOWER, , , ARM , ARM, , , ( Intel). - . RISC-V (

RISC-V), - , . , ,

RISC-V — Falcon NVIDIA.

: ?OpenCores, IP- ( ) . :

TSMC IP Alliance, IP .

Design&Reuse, IP-, ( ).

ChipEstimate, D&R, .

— ?, , , - .

— “” (), “” ( ), “” “” (211), “Neuromatrix” ( “”), RISC-V (Syntacore), ARM, MIPS, SPARC, MCS96, MCS51, C166, AVR, MSP430.

,

“ ” ( ):

IP-:

: ARM Cortex-M4F, ARM Cortex-M0, ARM946E-S c AMBA, ARM VFP9-S, SPARC v.8 c AMBA. 8- RISC .

IP- (PLL) TSMC, KeyASIC AnalogBits, Sidense Memory, - (eFuse) TSMC, IP- , ROM RAM ..

“ ” , IP- - (-, IP-).

IP? IP- (

“ ”,

“”,

211), . Design&Reuse ChipEstimate “ ” ( ) NTLab. , .