O tamanho dos transistores nos microcircuitos modernos está diminuindo inexoravelmente - apesar de falarem da morte da lei de Moore há vários anos e o limite físico da miniaturização já estar próximo (mais precisamente, já foi contornado com sucesso em alguns lugares). No entanto, essa redução não é em vão, e o apetite do usuário está crescendo mais rapidamente do que as capacidades dos desenvolvedores de chips. Portanto, além da miniaturização de transistores, outras tecnologias frequentemente não menos avançadas são usadas para criar produtos microeletrônicos modernos.

Na minha última frase, usei deliberadamente a frase "produto microeletrônico" em vez da palavra "microcircuito", porque este artigo se concentrará no fato de que dentro do gabinete da CPU ou GPU pode haver não apenas um cristal, mas todo um sistema de vários chips, então e chamado: um sistema em um pacote ou sistema em pacote.

O termo "sistema em um caso" é muito menos conhecido do que o termo relacionado "sistema em um chip", que os desenvolvedores gostam de superar. Além disso, agora quase todos os chips (exceto os mais simples) são de alguma forma um sistema em um chip, e os tempos dos conjuntos de microprocessadores e até dos chips individuais das pontes sul e norte são coisa do passado. As vantagens dos sistemas em um chip são bastante óbvias: menos casos na placa, menos área (e, portanto, mais barata), menos indutâncias e capacidades perdidas (o que significa que o produto funcionará melhor e mais rápido), mais fácil para o usuário (mais conveniente para implementar e menos espaço para erros), produção mais barata (em vez de vários microcircuitos especializados, um mais universal pode ser produzido).

Mas os sistemas em um chip também têm suas armadilhas.

Primeiro, quando você tenta colocar tudo em um cristal de uma só vez, corre o risco de obter um chip desse tamanho (e com tantas pernas) que ele não caiba em nenhum caso. Além disso (como sugere um tecnólogo profissional nos comentários), um chip muito grande corre o risco de não atingir o tamanho do campo do scanner fotolitográfico. Você pode contornar essa limitação, mas é muito difícil tecnicamente e, portanto, muito caro.

Em segundo lugar, quanto maior o tamanho do chip, menor a porcentagem de rendimento, especialmente se para a produção você precisar costurar várias janelas em uma máscara fotográfica. E isso, é claro, também afeta o custo.

Terceiro, se o seu sistema consiste em componentes heterogêneos, combiná-los em um único chip pode ser muito difícil, muito caro ou muito ruim para a qualidade do sistema. Por exemplo, a DRAM requer capacitores especiais, adicioná-los a um processo de fabricação "normal" pode ser excessivamente caro para a fábrica (que, por isso, será forçada a aumentar os preços para os clientes). A frequência de rádio ou os componentes de potência no silício podem ter parâmetros significativamente piores do que nos materiais A3B5 (arseneto de gálio e seus análogos), e a conexão das partes digital e analógica no mesmo cristal cria um problema de ruído.

A combinação de todos os fatores mencionados acima levou ao fato de que a tendência de “colocar tudo em um cristal” foi substituída por uma abordagem mais equilibrada, bem como o rápido desenvolvimento de tecnologias para embalar cristais em um caso.

Desempenho e rendimento

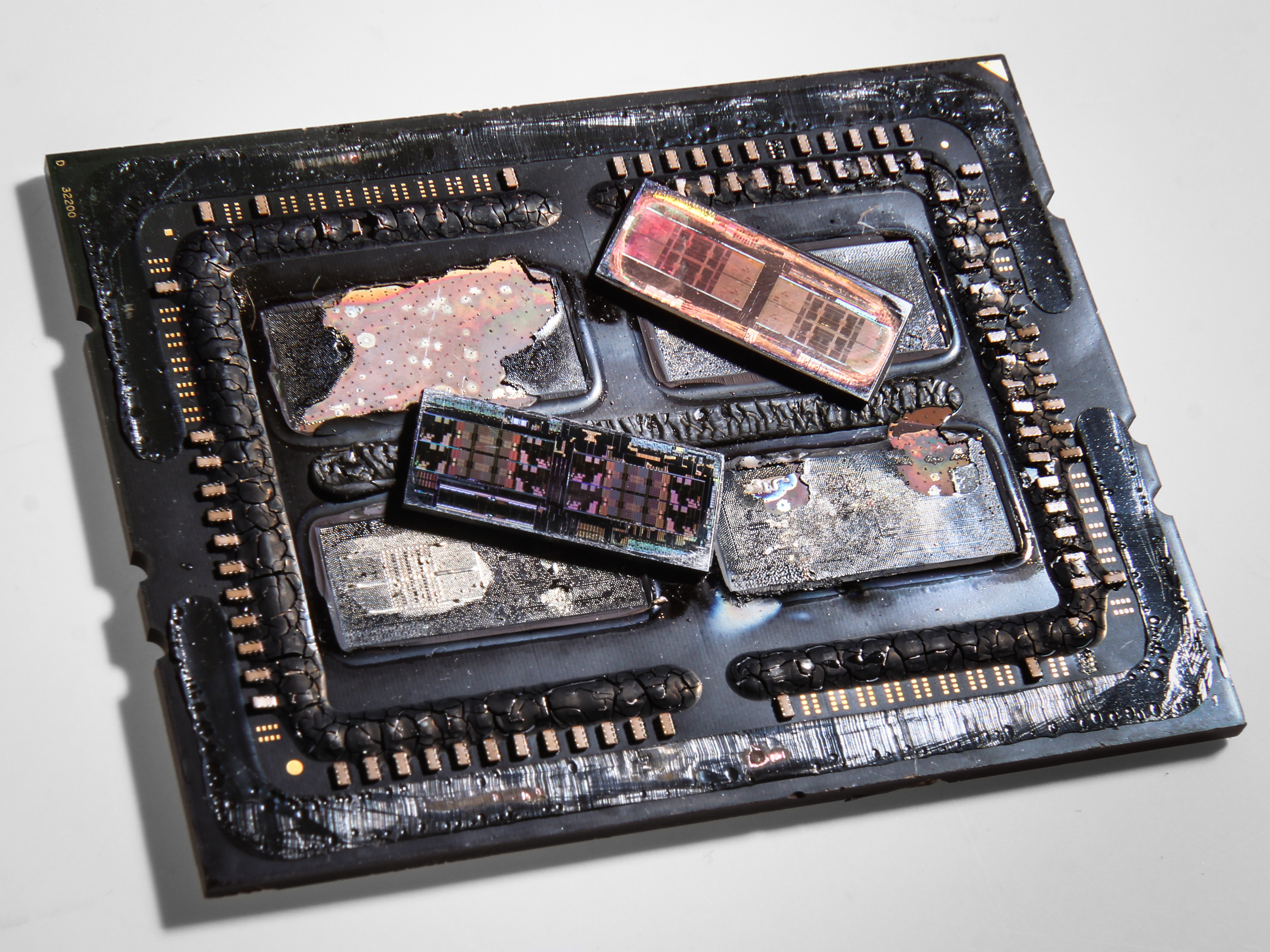

O primeiro exemplo que vem à mente é, é claro, os microprocessadores AMD (consulte KDPV). Os sistemas no caso de produtos com vários núcleos são considerados uma das razões importantes para a recente ascensão da empresa, ocorrendo no contexto dos problemas da Intel com o lançamento de um novo processo técnico devido ao baixo rendimento em chips enormes.

A figura mostra um chip Intel Xeon de 28 núcleos. O tamanho desses processadores atinge 456 milímetros quadrados, enquanto o tamanho máximo dos chips AMD é de cerca de 200 milímetros quadrados para um chip de oito núcleos, e produtos com mais núcleos são montados a partir de vários cristais idênticos em uma placa de circuito impresso de duas camadas localizada no gabinete do processador.

Nesta figura, você pode ver o design da placa dentro do gabinete dos processadores EPYC e Threadripper (também conhecido como KDPV). Quatro cristais de oito núcleos estão localizados em uma placa de duas camadas. No caso do Threadripper, com metade dos núcleos desativados. Por que os cristais são tão irracionalmente usados?

Primeiro, produzir um tipo de cristal pode ser mais barato do que vários diferentes.

Em segundo lugar, o mesmo se aplica ao restante do arnês - desativar desnecessariamente pode ser mais barato e mais tecnológico do que desenvolver e produzir vários modelos diferentes.

Em terceiro lugar, a porcentagem de rendimento adequada para um chip de 200 milímetros, provavelmente, também não é ideal, e esse design do produto final permite o uso de cristais nos quais nem todos os núcleos funcionam. A Intel faz exatamente a mesma coisa, mas seus problemas de saída são muito mais fortes devido a cristais maiores.

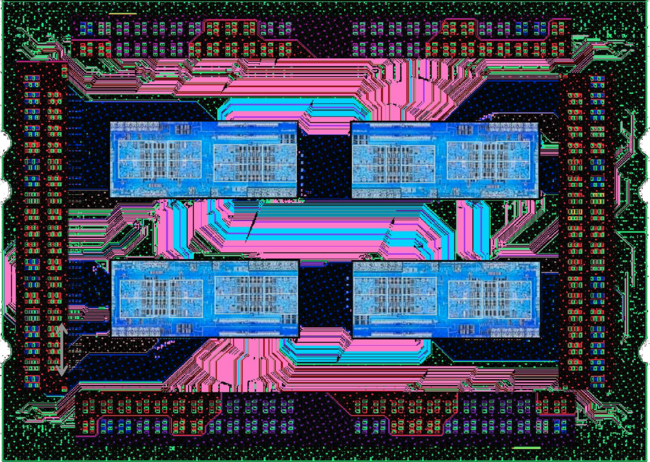

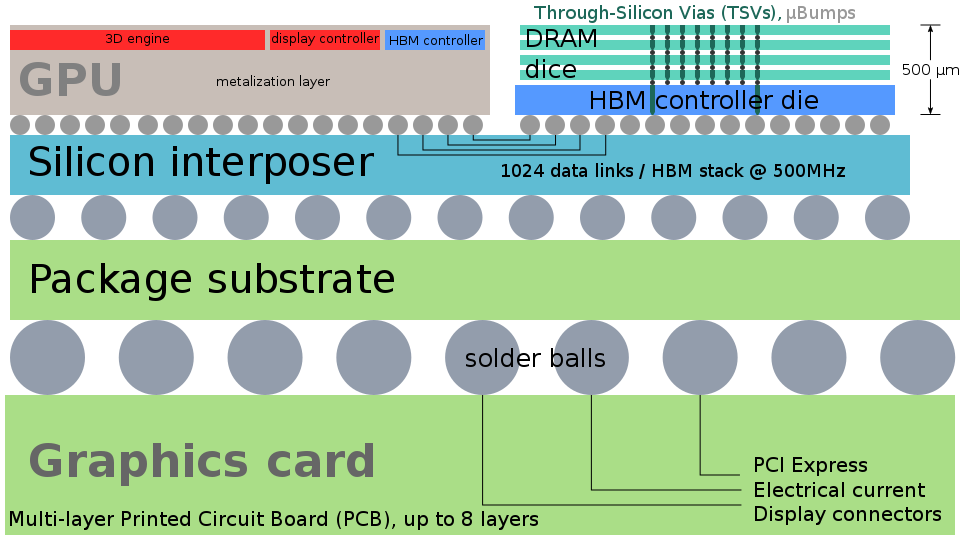

E aqui está um exemplo ainda mais interessante, também da AMD. O AMD Fiji é uma GPU com memória de alta velocidade incorporada, localizada diretamente no chassi. Por que isso é importante? Porque linhas muito mais curtas do processador para a memória possibilitam altas velocidades e, portanto, maior desempenho. Ao contrário do exemplo anterior, os cristais dentro do gabinete são diferentes. Além disso, não há cinco, como pode parecer à primeira vista, mas muito mais - vinte e dois. Aqui está uma seção da estrutura:

A camada superior é o próprio chip GPU e a “prateleira” de vários (neste caso, quatro) chips de memória conectados usando colunas condutoras TSV (through-silicon-via) - que atravessam o cristal em toda a espessura.

Os TSVs se parecem com isso, esquematicamente e em escala real.

A tecnologia TSV, que originalmente apareceu apenas para matrizes de memória (afinal, nunca há muita memória, certo?), Agora está se tornando cada vez mais difundida, inclusive graças ao próximo chip localizado na GPU e na memória.

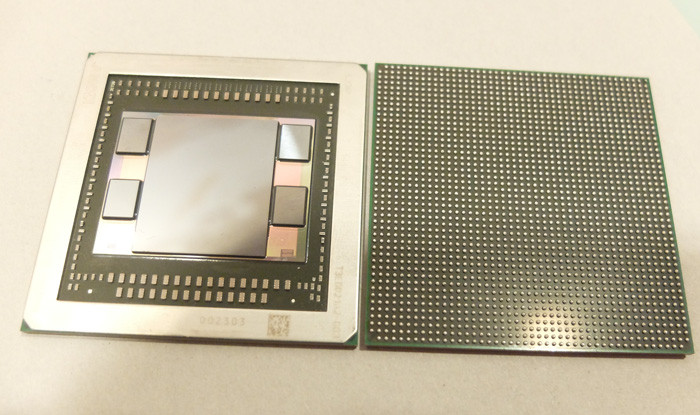

O Silicon Interposer é um substituto para uma placa de circuito impresso multicamada feita de cristal de silício e contém várias camadas de metalização e TSV para conectar os chips na parte superior e na caixa. O uso de silício permite obter tamanhos significativamente menores de elementos (unidades de mícrons) do que uma placa de circuito impresso, mas, ao mesmo tempo, os padrões de design podem ser suficientemente rigorosos para que esse chip de conexão tenha um alto rendimento e um preço acessível. As dimensões menores dos elementos significam menos influência dos parâmetros parasitários das conexões, e os TSVs mencionados são muito mais compactos do que as vias da placa de circuito impresso e permitem que centenas ou mesmo milhares de contatos sejam transportados através do interposer para o gabinete. Juntamente com os MEMS, esses chips de interconexão são um importante mercado novo para fábricas desatualizadas, com bolachas de 100 a 150 milímetros de diâmetro.

Outro pioneiro da integração 3D é o Xilinx. Tecnologicamente, seus FPGAs são próximos dos produtos AMD (especialmente aqueles com memória integrada), e os motivos também são semelhantes: os FPGAs são um nicho de mercado em que uma transição precoce para um novo processo de fabricação pode oferecer uma vantagem séria sobre os concorrentes. De acordo com várias estimativas, em um estágio inicial da vida de uma tecnologia, reduzir o tamanho do cristal em três a quatro vezes pode aumentar o rendimento em duas a três vezes, de algumas dezenas de por cento para mais da metade. Além disso, os FPGAs são uma estrutura regular na qual é conveniente rastrear defeitos tecnológicos. Portanto, os fabricantes de FPGA são “primeiros clientes” típicos de novos processos de fabricação, e a Xilinx, devido ao fato de seus produtos conterem vários cristais pequenos em vez de um tamanho grande, pode lançar novos modelos vários meses mais rapidamente que os concorrentes.

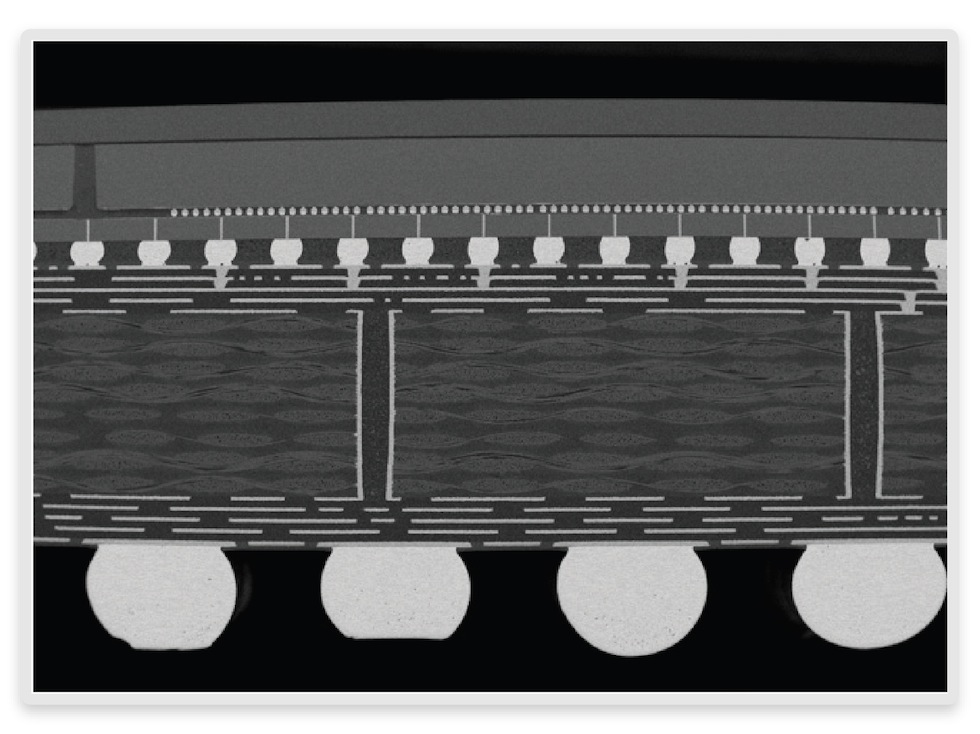

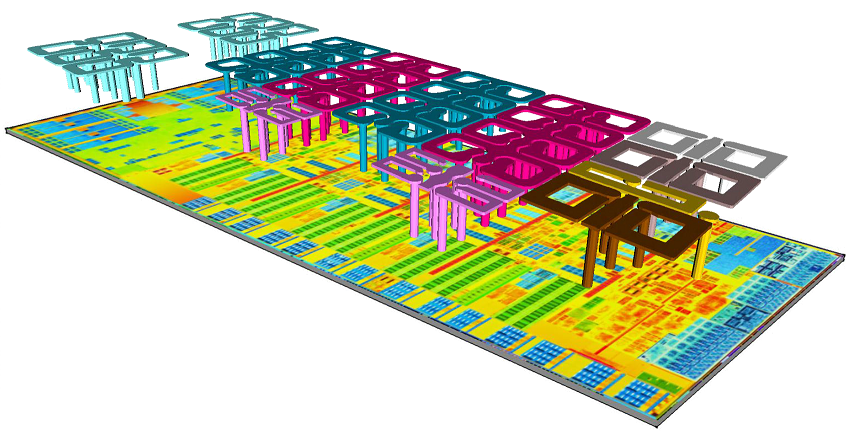

Aqui está uma seção transversal do interior do Xilinx FPGA. O chip superior é na verdade uma parte do FPGA com contatos muito pequenos (40-45 mícrons) ao interposer, conectando vários chips e, na parte inferior, a base do gabinete, que possui uma dúzia de camadas de suas próprias interconexões metálicas.

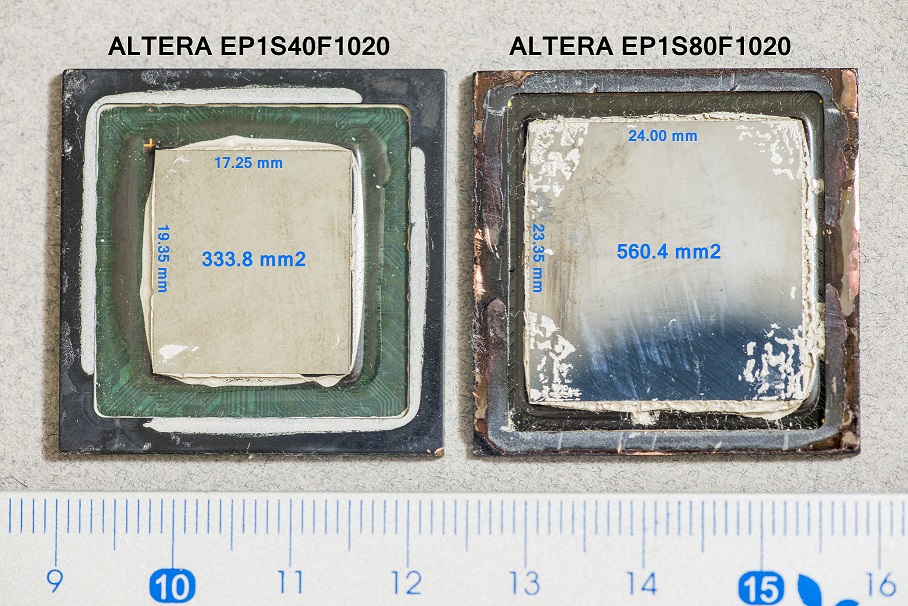

Para comparação - FPGA Altera em um cristal enorme. Quinhentos e sessenta milímetros quadrados, Carl! Se de repente este post for lido por tecnólogos de produção de microeletrônicos, verifique se eles não têm um ataque cardíaco.

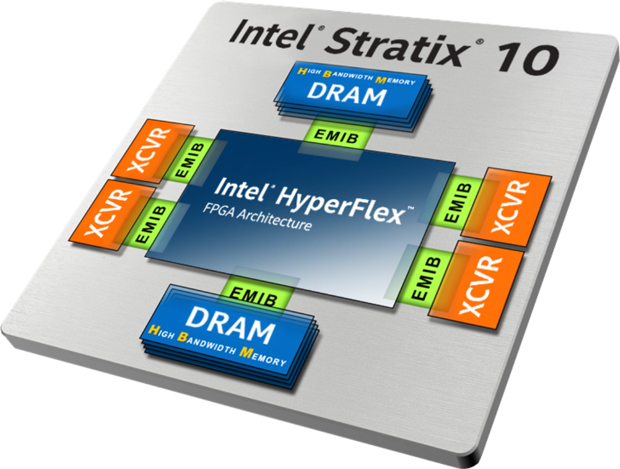

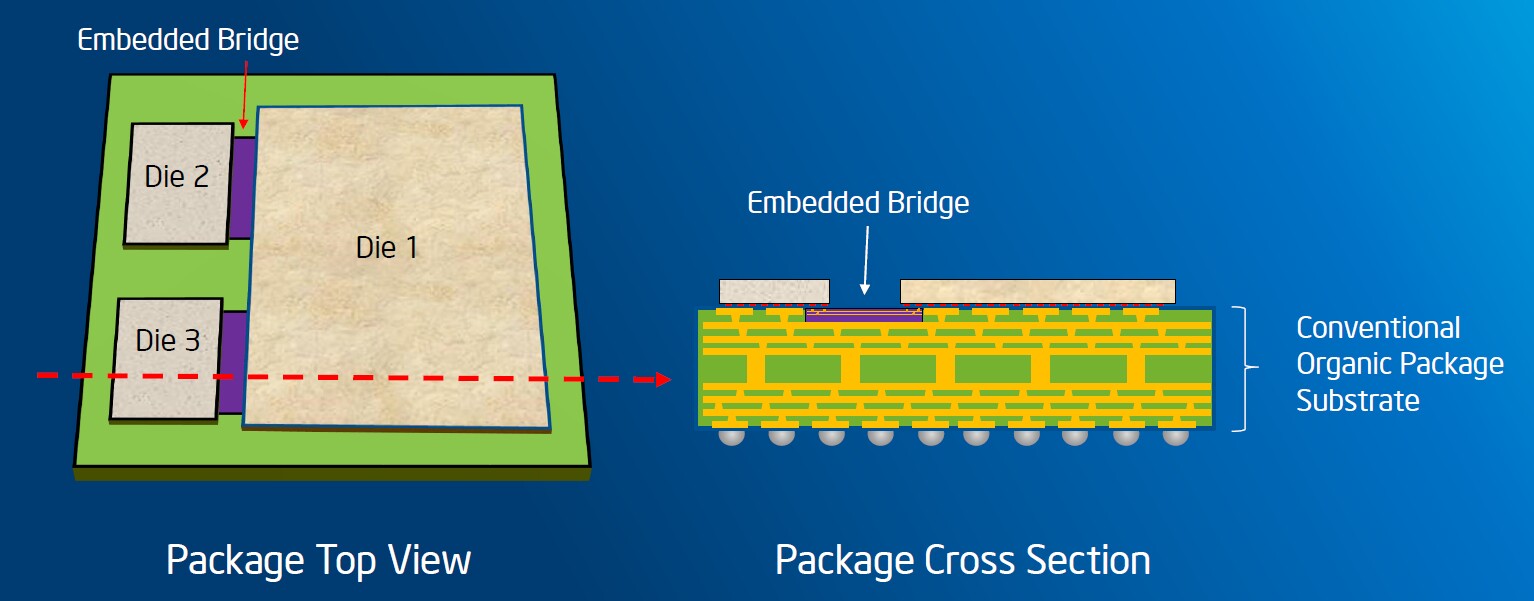

No entanto, a Intel / Altera, é claro, não fica parada, observando o sucesso dos concorrentes. Seu mais recente desenvolvimento em sistemas fechados é a EMIB (Embedded Multi-Chip Interconnect Bridge). É conveniente analisá-lo usando o Intel Stratix 10 FPGA.

Como você pode ver, o EMIB interconecta (um!) Chip FPGA, memória (e aqui estruturas de vários andares) e cristais periféricos. Então, o que é esse EMIB? Um pouco mais alto, escrevi sobre o interposer de silício que, devido a um processo técnico mais difícil, tem um preço muito mais baixo do que um chip de tamanho semelhante fabricado com tecnologia fina. No entanto, o interpositor é enorme. É possível diminuí-lo?

A resposta da Intel é sim. A idéia do EMIB é usar vários pequenos em vez de um grande interpositor e, por sua vez, integrá-los diretamente no substrato do corpo.

Aqui está uma pequena seleção de produtos criados usando interposers de silicone. Preste atenção às suas dimensões colossais pelos padrões microeletrônicos e ao fato de que, como discutimos acima, os chips de combate da Xilinx são divididos em vários pequenos pedaços.

Mais do que apenas desempenho.

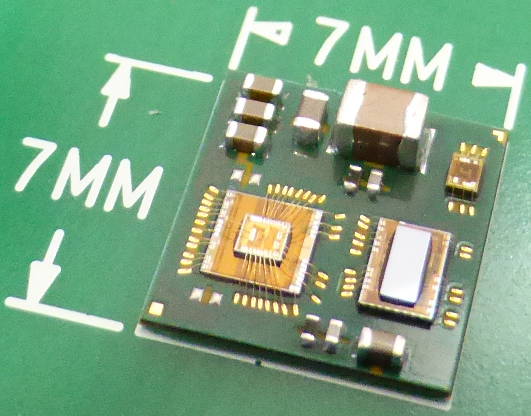

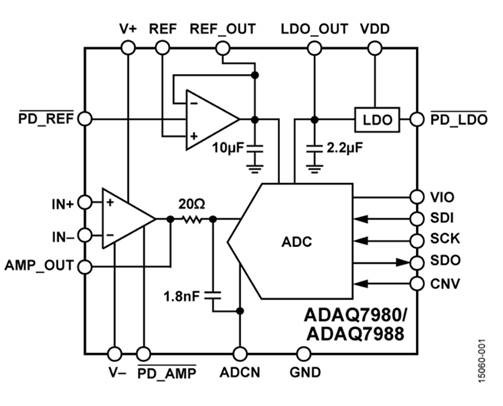

A figura abaixo mostra o interior de uma carcaça do ADC da Analog Devices e diagrama de circuito. Parece uma placa de circuito impresso completamente comum para o ADC, só que menor, certo? É isso mesmo, apenas devido ao uso de componentes de estrutura aberta, os erros associados a elementos espúrios foram reduzidos, e o fato de a placa ser desenvolvida em dispositivos analógicos permite economizar muito tempo do cliente e, ao mesmo tempo, garantir que o usuário não estrague a escolha dos errados. componentes ou placa com fio inadequado.

No entanto, há um pequeno truque na figura acima: veja cristais dispostos em dois andares? O cristal superior é um chip com os componentes ativos do próprio ADC e (aparentemente) um amplificador operacional duplo, e o cristal inferior são os componentes passivos (capacitores e resistores). A execução em um cristal separado permite torná-los muito maiores em tamanho (e, portanto, reduzir erros) sem aumentar (e, portanto, aumentar o custo) do cristal principal.

Tudo o mesmo pode ser feito em um chip (o que, de fato, não é incomum, especialmente para ADCs incorporados em microcontroladores), mas esse chip será muito maior (o que significa que, como descobrimos, existe o risco de diminuir a porcentagem de utilização), e a tecnologia para ele terá que suportar todas as opções adicionais necessárias. Além disso, a combinação de diferentes blocos no mesmo cristal levará à necessidade de garantir que eles não se afetem (por exemplo, de alguma forma, livre-se do ruído no substrato do cristal).

Recursos adicionais da caixa

Como já descobrimos, embalar elementos diferentes (incluindo componentes SMD passivos) em uma caixa permite reduzir significativamente as dimensões do produto final e até aumentar sua velocidade. Mas e se usarmos o próprio estojo como um elemento funcional do dispositivo?

Em 2013, os processadores Intel (microarquitetura Haswell) implementaram um regulador de tensão integrado (FIVR - regulador de tensão totalmente integrado), no qual a parte ativa do regulador foi implementada no chip do processador e a parte passiva (capacitores e indutores) foi integrada ao gabinete.

A indutância integral é uma dor de cabeça para todos os desenvolvedores de chips, porque as bobinas no chip são obtidas não apenas com os melhores parâmetros, mas também com parâmetros enormes (o que significa que são muito caros, especialmente com tecnologias finas). E trata-se de bobinas de sinal sem núcleo, não se fala em nenhuma transmissão de energia. A Intel contornou esse problema com sucesso, integrando dezenas de bobinas pequenas paralelas operando a uma frequência de 160 MHz no compartimento do microprocessador. Portanto, eles foram capazes de simplificar significativamente os requisitos de energia do microprocessador.

No entanto, algo deu errado com esse desenvolvimento e não havia mais processadores Intel FIVR na próxima geração de processadores Haswell. Desde então, houve rumores de que eles voltarão ao FIVR, mas até agora eles permaneceram rumores.

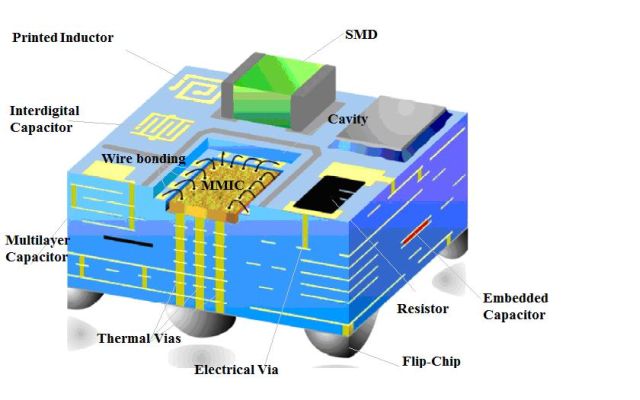

No entanto, mesmo sem a Intel, a direção da integração de componentes passivos no caso está se desenvolvendo ativamente, por exemplo, em casos do tipo LTCC (cerâmica de baixa temperatura). É claro que existem limitações e armadilhas (associadas, por exemplo, à precisão das classificações), mas essa tecnologia está em demanda e está se desenvolvendo ativamente. O caso LTCC em camadas é mais ou menos assim:

A figura mostra todos os tipos de elementos passivos feitos em cerâmica multicamada e até um dissipador de calor de metal (é o caso de um poderoso circuito de micro-ondas). De fato, é uma mistura do gabinete com uma placa de circuito impresso de cerâmica. Tais peças são muito populares para os módulos de RF e também são relativamente baratas na produção em pequena escala.

O que mais?

Existem muitas aplicações em potencial para sistemas no caso, e é quase impossível listar todas elas; além disso, algo novo está aparecendo constantemente, inclusive devido ao fato de que essas tecnologias são muito mais acessíveis que os transistores de 10-7-5-3 nanômetros.

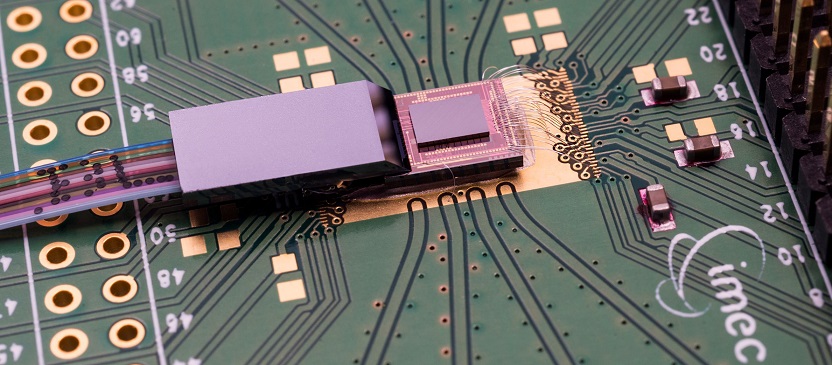

Um bom exemplo das novas aplicações e propriedades que a integração de chips heterogêneos abre em um único pacote é uma variedade de sistemas ópticos nos quais o SiP permite montar um receptor ou emissor (geralmente não feito de silicone) e seus circuitos de potência e controle. Na ilustração abaixo - um link óptico de protótipo a 400 Gb / s (e promessa antes de terabit), montado no instituto de pesquisa belga IMEC.

Além disso, esses aplicativos promissores para sistemas no caso consideram interpozers com capilares internos para refrigeração líquida (não apenas processadores de jogos, mas também chaves de poder e lasers), unidades MEMS integradas no caso e muito mais não se enquadra na estrutura estreita da lei de Moore. Além disso, a onipresente Internet das coisas é considerada um mercado importante para sistemas no caso em que são importantes tamanhos pequenos, a ausência de perdas (principalmente energia, não tempo) em elementos espúrios e a capacidade de integrar componentes passivos, por exemplo, partes do caminho do rádio, no microcircuito.