Na semana passada, a Intel anunciou a aquisição do eASIC, que está desenvolvendo ferramentas de desenvolvimento baseadas em FPGA para "ASICs estruturais". ASICs estruturais são um cruzamento entre FPGAs convencionais e ASICs convencionais; eles permitem reduzir o tempo de comercialização do produto e reduzir seu custo.

A Intel usa a tecnologia eASIC

desde 2015 em versões personalizadas dos processadores Xeon; O eASIC (120 pessoas) agora fará parte do Intel Programmable Solutions Group (PSG).

Mesmo aqueles que há muito tempo fizeram "amigos" mutuamente de FPGA e ASIC não se recusam a explicar o que são "ASICs estruturais". O poder de computação do computador não se limita à CPU ou GPU, existem outras classes de processadores, como, por exemplo, FPGA - eles são desenvolvidos pela Altera, adquirida pela Intel. Nos FPGAs, milhões de portas podem ser programadas de maneira flexível para implementar a funcionalidade necessária. De fato, a maioria das CPUs e GPUs são inicialmente simuladas em FPGAs para testar o desempenho. Os FPGAs são uma maneira simples de modelar circuitos de interconexão e seu escopo é amplo. Os FPGAs também podem conter unidades de hardware disponíveis no mercado, como núcleos ARM ou transceptores para comunicações externas.

Outro exemplo é o ASIC (Application Specific Integrated Circuit), um chip projetado para executar um conjunto bem definido de tarefas. O ASIC é otimizado ao máximo para suas tarefas, e a lógica de seu trabalho não pode ser alterada. Freqüentemente, a CPU e a GPU são classificadas como ASICs no sentido de que sua microarquitetura também é fixa, mas elas são projetadas para resolver vários problemas e são universais, enquanto ASICs são criadas para tipos de cálculos claramente definidos. Recursos do ASIC: eles são rápidos, econômicos, mas relativamente caros e difíceis de fabricar.

Os ASICs estruturais do EASIC podem ser chamados de uma solução sem entusiasmo. Os engenheiros criam um protótipo usando FPGA, mas não perdem tempo otimizando seus circuitos, mas fabricam um chip com uma arquitetura fixa em sua base. Devido a isso, ele funciona mais rápido do que uma amostra com blocos personalizados, embora perca os benefícios da eficiência energética. No entanto, o tempo para o seu desenvolvimento é comparável ao FPGA, não ao ASIC - economiza até 6 meses. A contribuição do eASIC é que a otimização da camada de camada única é usada para substituir o roteamento SRAM pelo end-to-end, o que reduz significativamente os custos de produção. O eASIC também fornece bibliotecas de células fixas, também de camada única, o que reduz ainda mais o consumo, o tamanho do cristal e o tempo de colocação no mercado. Além disso, os designers podem ignorar os procedimentos padrão ao criar ASICs, como balanceamento de sincronização, análise de integridade de sinal, teste de atenuação de energia e outros. Assim, “ASICs estruturais” podem ser descritos como FPGAs, que não podem mais ser programados, que possuem as melhores qualidades dos FPGAs e ASICs.

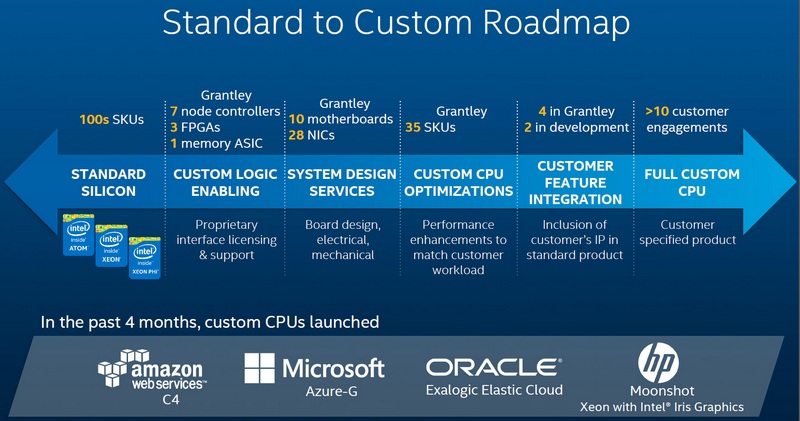

O gráfico mostra a situação atual e as perspectivas no campo dos processadores Intel Xeon personalizados

O gráfico mostra a situação atual e as perspectivas no campo dos processadores Intel Xeon personalizadosA Intel precisa da tecnologia eASIC para integrar a lógica programável nos processadores Xeon para melhorar o desempenho, o consumo de energia e o preço. Juntamente com o Xeon padrão, a Intel está lançando opções personalizadas para seus maiores clientes. Como podemos ver no diagrama, a profundidade da personalização aumentará. Com a aquisição da eASIC, esse processo irá acelerar e expandir. Parece que a abordagem “CPU como ASIC” pode nos trazer muitas coisas interessantes.