1. Introdução

Todos conhecemos o problema da galinha e dos ovos: os empregadores não querem contratar graduados sem experiência profissional, mas onde, então, os graduados podem obter experiência profissional? Na microeletrônica, esse problema é especialmente agudo, tendo em vista a enorme quantidade de experiência específica necessária. Desde os tempos soviéticos, nossas universidades são famosas pelo treinamento teórico mais amplo, o que deve ajudar o graduado em qualquer situação difícil da vida. No entanto, a indústria moderna requer experiência prática. Acrescentamos aqui a falta de motivação, o que leva ao fato de que 15% dos graduados trabalham na especialidade, e temos a mais severa escassez de pessoal do setor, exigindo muito a qualidade do pessoal. Mas se cada aluno pudesse "piscar uma lâmpada" de seu próprio cristal, a situação poderia se desenvolver de uma maneira completamente diferente.

Figura 1. KDPV

O que impede que gigantes de treinamento em microeletrônica doméstica, como MEPhI e MIET, ajam de maneira semelhante a seus colegas estrangeiros (por exemplo, MIT ou UZH), ou seja, permitindo que estudantes de pós-graduação emitam seus próprios cristais? Obviamente, pode-se supor que a produção do próprio cristal é uma tarefa extremamente longa, complicada e cara, e, portanto, é cara para um instituto e impossível para um aluno. No entanto, isso não é verdade. Vamos dar uma olhada em uma das tecnologias disponíveis no mercado doméstico de microeletrônica, familiaridade que permitirá ao aluno se tornar muito mais atraente em termos de emprego futuro, e cuja oferta para o estudante permitirá que a universidade aumente significativamente sua classificação aos olhos de candidatos e empregadores.

2. O que é BMK?

BMK é um cristal de matriz básica. Não está claro agora? Dê um passo para o lado e observe o ciclo de produção ASIC (custom-chip manufacturing) bastante simplificado:

- Desenvolvimento da descrição do esquema

- Criação de Topologia

- Transferindo arquivos de tecnologia para a fábrica e aguardando a preparação dos cristais

- Medições dos cristais obtidos

- Invólucro

- Para venda

Existem dois pontos muito "longos" aqui - o desenvolvimento do esquema e a expectativa dos resultados da planta. Várias metodologias são usadas para reduzir o tempo de desenvolvimento e, em um ambiente estudantil, a melhor solução é o trabalho em equipe, mas estamos interessados no segundo ponto - o horário de trabalho da planta. Como a usina microeletrônica é uma produção muito inerte, tudo deve estar de acordo com o planejado. Não está na hora da data de lançamento da produção? A próxima tentativa é através do trimestre. A produção em si, dependendo da complexidade do produto, pode durar até seis meses. Além disso, esses seis meses são o ciclo de produção aprovado em máquinas altamente automatizadas, e não a falta de pessoal. Como esses termos podem ser reduzidos? Ao introduzir uma certa base comum em todos os esquemas produzidos, para que o estágio de introdução das diferenças seja rápido.

Essa base comum é a BMK - um cristal com transistores pré-arranjados, cuja finalidade funcional é determinada pelas camadas de metalização, que permitem a interconexão dos transistores. Essas interconexões formam a funcionalidade exclusiva do cristal.

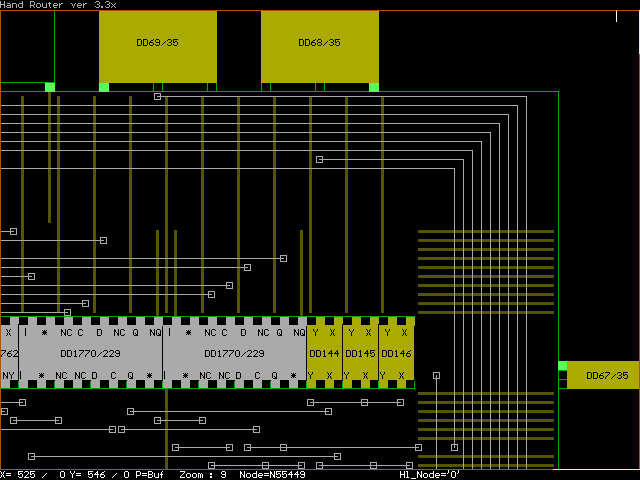

Figura 2. Roteador manual v3.3, originalmente das entranhas do NICEVT, criado nas décadas de 1980 a 1990.

Em uma BMK, usando diferentes esquemas de metalização, é possível produzir centenas de microcircuitos diferentes para várias organizações. Nesse caso, a própria BMK se torna um produto de produção em massa para a planta, e os estágios de acabamento - camadas de metalização, podem ser rapidamente alterados de acordo com as necessidades do cliente. Assim, obtemos “lançamentos” mais frequentes de novos produtos para produção e preços mais baixos. Para o desenvolvimento do aluno, esses dois pontos são extremamente relevantes.

3. Por que BMK?

Vamos comparar os benefícios do uso de diferentes métodos de treinamento e ver o que produz o maior efeito ao menor custo.

Tabela 1. Comparação do efeito educacional da aprendizagem usando vários métodos

Codificação de cabeçalho caso contrário, não caberá na largura do layout.

A - Desenvolvimento orientado a FPGA

B - BMK sem o uso de FPGAs e com um release real

C - BMK usando FPGA e com lançamento real

D - ASIC sem FPGA e sem versão real

E - ASIC com FPGA e sem versão real

F - ASIC com FPGA e versão real

G - Programa atual de treinamento no MEPhI, kaf. 27

| Componente de rota | Um | B | C | D | E | F | G |

|---|

| Declaração do problema | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| Programação RTL | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| Programação RTL baseada em ASIC | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Trabalhar com CAD moderno | ○ | ■ | ■ | ■ | ■ | ■ | ○ |

| Compreendendo o código específico do FPGA | ■ | □ | ■ | □ | ■ | ■ | ○ |

| Compreendendo o sintetizador | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Entendendo os requisitos de restrição | ○ | ■ | ■ | □ | □ | ■ | □ |

| Entendendo a importância do posicionamento e rastreamento | ○ | ■ | ■ | □ | □ | ■ | □ |

| Teste | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Criação do ambiente de verificação | ■ | ■ | ■ | □ | ■ | ■ | □ |

| Simulação de vários cantos | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Modelagem de extração | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Invólucro | □ | ■ | ■ | □ | □ | ■ | □ |

| Circuito analógico | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Trabalhar com instalações de medição | □ | ■ | ■ | □ | □ | ■ | ○ |

| Trabalho em laboratório | ■ | ■ | ■ | □ | □ | ■ | ○ |

| Custo | 1 | 2 | 3 | 0 0 | 1 | 4 | 0 0 |

■ - está presente no programa;

□ - ausente no programa;

○ - opções são possíveis.

Esta tabela é preenchida apenas pela minha visão de como a presença de um estágio específico em um projeto de graduação esférica no vácuo afeta a diligência dos alunos. Na realidade, alguém pode dominar toda a rota sem ensinar assistência, enquanto alguém não consegue escrever um multiplexador no Verilog. A linha "custo" reflete o posicionamento no topo, mas em nenhum caso multiplicadores. Além disso, o "custo" não leva em consideração o custo real do CAD, por vários motivos diferentes.

Agora fica claro que, com um custo adicional menor, a rota destinada ao lançamento do BMK, usando FPGAs e com o lançamento real, cobre exatamente o mesmo conjunto de habilidades necessárias para o lançamento do ASIC. O resto das rotas, embora abranjam nominalmente uma ampla gama de habilidades, na prática, elas não são executadas conscientemente pelos alunos devido à falta de motivação para aplicar uma grande quantidade de esforço sem nenhum resultado visível.

4. Observação do Mercado

Até a presente data, o design de microcircuitos básicos tornou-se uma tarefa bastante simples: todo mundo já ouviu falar em FPGAs (circuitos integrados lógicos programáveis), sintetizadores de código, programas para organizar componentes e subsequente rastreamento do microcircuito. Ao mesmo tempo, muitos desenvolvedores iniciantes têm dificuldade em imaginar o que é BMK, como trabalhar com ele e quais vantagens ele oferece. Infelizmente para os fabricantes de BMK, essa situação leva aos seguintes resultados:

"A análise de 2009 mostra a saída de alguns consumidores devido à expansão do escopo de aplicação de FPGAs importados com base nas licenças emitidas." (C) o relatório anual da Anstrem OJSC para 2009.

Existem muitos fabricantes de BMK no mercado moderno de microeletrônica: nacional e estrangeira. Em particular, no Estado da União da Rússia e da Bielorrússia, existem pelo menos seis fabricantes de chips que oferecem seus BMCs para desenvolvimento: Angstrem OJSC, IEC NN, Progress NIIMA JSC, Centro Tecnológico e Centro de Produção Científica, NPO OJSC de Física e Minsk Integral "

Geralmente, sistemas CAD especializados de empresas conhecidas, como Cadence, Synopsis ou Mentor Graphics, são usados para o desenvolvimento de microcircuitos, mas no caso da BMC, tudo é um pouco mais complicado. Este software não fornece suporte oficial para o BMK, como um tipo separado de microcircuito, mas é possível fazê-lo funcionar no modo correto usando vários truques. Nessa situação, os desenvolvedores da BMK precisam desenvolver suas próprias rotas de design exclusivas, que às vezes usam o software OpenSource, por exemplo, o Yosis, junto com o software desenvolvido de forma independente.

- No caso do Angstrom OJSC, é muito difícil encontrar as informações exatas e o CAD usado. No entanto, existem pré-requisitos para acreditar que seu CAD "Nevod" não é mais usado e a transição para o uso dos produtos Cadence foi concluída.

- IEC NN, OJSC NPO Fizika, JSC NIIMA Progress e Integral não fornecem informações sobre o CAD usado; no entanto, a Integral possui PDK sob Cadence, para que possamos concluir que o restante da rota também está lá.

- O NPK "Technological Center" usa seu CAD "Ark", que implementa quase toda a rota do projeto. De qualquer forma, isso é aprovado em seu site.

5. Quantas válvulas são suficientes para todos?

Um motivo popular para a falta de vontade de trabalhar com a BMK é a incerteza sobre se o esquema desenvolvido se encaixará nessa BMK e a que velocidade tudo isso funcionará. Obviamente, é bom quando há uma série BMK com uma única biblioteca de design e você pode pular para um cristal mais amplo ou mais rápido, se necessário, mas isso nem sempre é possível. Aqui, por exemplo, tudo está claro sobre o TSMC: existem muitas empresas que declaram abertamente a velocidade de seus circuitos executados em um ou outro. processo. E a nossa BMK? Onde posso obter uma lista de produtos criados com base no BMK e ver o desempenho deles?

Alguns exemplos:

- BMK digital para analógico. Cerca de 300 portas + 8 transistores de potência. Um esquema de timer por 2 minutos com dois níveis de proteção é implementado. Monitoramento de carga nos espelhos atuais, transistores de potência para controlar a carga. Consumo de energia reduzido, trabalho com quartzo 32.768 kHz, faixa de tensão de alimentação de 1.8V a 9V.

- Digital contente. BMK persistente. 100.000 válvulas. Especiais de lógica. destino + NCO (oscilador controlado numericamente). Fase da bateria 40 bits, seno - 12 bits. Dois registros controlam a freqüência senoidal, controle paralelo e serial. A saída é paralela.

- BMK digital para analógico. Cerca de 400 portões + DAC de 10 categorias. Gerador senoidal de 7 bits com saída de corrente.

- BMK digital. De 1500 a 3000 válvulas. Vários terminais do canal multiplex GOST 26765.52-87.

- BMK digital. Cerca de 500 portões. Um gerador de oito canais para controlar os enrolamentos primários dos transformadores.

- BMK digital. Cerca de 3000 portões. Circuito maioritário para barramento de 8 bits.

Infelizmente, as especificidades do mercado levam ao fato de que a grande maioria dos desenvolvimentos na BMK permanece desconhecida para o público em geral. Os dados públicos não dão uma idéia clara da velocidade, e os números indicados nas brochuras parecem ambíguos. No entanto, para as tarefas de conhecer a tecnologia, não é necessário muito, e já ter alguma experiência por trás disso é muito mais fácil fornecer uma estimativa aproximada da complexidade de um esquema específico.

6. Processo de desenvolvimento

Vamos para o mais interessante. Temos: BMK para ~ 3k gates (1 válvula = 2 transistores CMOS) com arquitetura de canal, fiação em uma camada de metal e uma subcamada de polissilício; entusiasmo; aprovação da gerência da empresa para auto-treinamento de funcionários.

A idéia do futuro cristal nasceu da ociosidade, ou seja, da leitura de um fórum, onde, em particular, houve uma conversa sobre soluções compactas de circuitos para o cálculo de códigos senoidais. Este tópico me pareceu interessante e decidi ver o que pode ser feito nessa direção.

Agora vamos ver o que foi feito, o que não foi, que erros e que conclusões foram feitas.

6.1 Design

Estudos de superfície mostraram que existe um algoritmo para calcular valores senoidais, o qual, a partir de operações matemáticas, requer apenas soma, subtração e deslocamento para a direita. Descobriu-se que este não é apenas um algoritmo, mas uma família inteira chamada CORDIC (Computador Digital de Rotação por Coordenadas). Aqueles que estão interessados nos detalhes do algoritmo podem consultar a lista de referências no final do artigo, mas vou esclarecer apenas que, usando esse algoritmo, você pode calcular não apenas o seno, mas também o cosseno, a tangente do arco, multiplicar e dividir os argumentos e contar algumas funções hiperbólicas.

Tendo estudado muitas publicações sobre esse algoritmo e sistematizado esse conhecimento em minha cabeça, concluí que você pode tentar implementar esse algoritmo em uma BMK com capacidade para cerca de 3k válvulas.

Então, com o que terminamos na arquitetura de circuitos?

- Algoritmo CORDIC em pipeline expandido para calcular o seno.

- 4 bits extras em barramentos de dados internos para compensar erros de arredondamento.

- Totalizador acumulativo de 11 bits para o valor da fase.

- O incremento de fase é definido pelo barramento paralelo.

- Formato de saída de dados: 7 bits + sinal, barramento paralelo.

Tudo parece estar bem, mas o que acontece se você não compensar os erros de arredondamento? E aqui está o que (comparando o barramento interno de 11 bits e 8 bits):

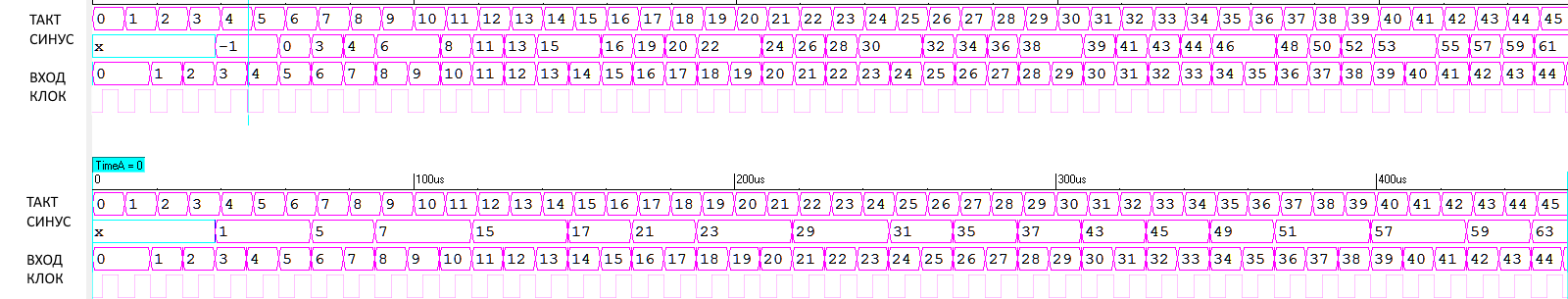

Figura 3. Comparação da saída do algoritmo CORDIC usando barramentos internos de 11 bits e 8 bits, respectivamente.

Se você prestar atenção às segundas linhas de dados, poderá ver que os erros de arredondamento podem efetivamente diminuir a qualidade de seus cálculos.

Se, no futuro, conectar este chip ao DAC de 7 bits, obteremos um gerador senoidal totalmente adequado (DDS, em nossa opinião - síntese digital direta). Nesse caso, teremos a oportunidade de modulação de frequência do seno, mas não haverá possibilidade de modulação de fase.

Em geral, a rota para trabalhar com pequenas BMCs é um pouco diferente da rota de design atual. Se você pensar bem, as diferenças se tornam óbvias: com um volume tão pequeno de válvula, é necessário usar cada válvula com extrema eficiência, e o principal paradigma do design moderno não é de todo isso. Ela diz que o produto deve, em todas as etapas, ser arquitetonicamente compatível com os sistemas modernos de teste, verificação e medição automatizados. Nesse caso, a questão da eficiência da válvula permanece fora dos suportes, como a sobrecarga necessária. De fato, nos anos de desenvolvimento dinâmico das tecnologias de produção, pensar em eficiência era supérfluo. Então, quando (e se) ainda atingirmos o limite físico e pararmos de aumentar a densidade dos transistores no cristal, os problemas de eficiência do uso da área chegarão até nós em pleno crescimento. Bem, com pequenas BMKs, elas permanecem em altura total e, portanto, a conclusão: na BMK de pequenos tanques, você pode e deve usar projetos complexos usando vários esquemas complicados de geração de blocos, várias travas, feedbacks e outras coisas, cuja utilização na rota moderna um engenheiro sênior teria rasgado suas mãos.

O principal problema com o uso dessas coisas é que, para usá-las, o engenheiro deve estar claramente ciente do que está fazendo e por quê. No entanto, se houver entendimento, o ganho pode ser fantástico. Se não houver entendimento ... bem, você pode atirar na perna com um milhão de maneiras efetivas diferentes.

Como era a rota de design no meu caso:

- Gráficos manuais como um gráfico de itens da biblioteca

- Estimativa do volume do circuito resultante

- Processar o circuito até que o volume exceda 80% da capacidade da BMK

- Isso também inclui trabalho na criação de novos elementos da biblioteca, seus testes e integração na rota de design

- Elaboração de testes para o circuito

- Rastreamento manual de circuitos

Designers experientes aqui podem objetar imediatamente que várias etapas importantes foram perdidas, mas eu realmente esqueci de mencionar qualquer coisa.

O design manual mostra muito bem a importância de uma biblioteca de componentes de qualidade. As primeiras variantes do circuito não se encaixavam no cristal simplesmente pelo volume da lógica, mas no caso de um canal BMC - aquele em que a fiação passa pelos canais dispostos entre as "filas" dos transistores - aproximadamente 30% do volume do circuito é ocupado por interconexões. Portanto, tive que expandir um pouco a biblioteca, com base na topologia obtida neste projeto em particular. Essa abordagem permitiu economizar um número significativo de portões e ainda mais ou menos livremente estabelecer todas as rotas.

O enchimento final do cristal é de 72%, outro terço do cristal foi para a fiação. Em seguida, os arquivos foram transferidos para a fábrica e retornei aos meus projetos de trabalho atuais.

Com o método de design “manual”, os seguintes pontos devem ser lembrados:

- Você não pode usar elementos da biblioteca sem pensar, com base em suas funções. É necessário estudar do que esse elemento é composto no nível do transistor, seja ele digital ou analógico. Quais são suas habilidades de suporte de carga em termos de entradas e saídas, seja ele puramente lógica CMOS, TG ou qualquer outra coisa.

- É necessário levar em conta e coordenar a potência dos elementos e sua carga.

- Se você tiver um gatilho síncrono, precisará cronometrá-lo com sinais de potência igual.

- Se você usar algum tipo de sinal sem amplificação intermediária e for carregado em muitos consumidores, o sinal poderá falhar muito. Isso pode ser insignificante em condições normais, mas é crítico ao testar WWF (fatores externos).

Nenhum sistema de modelagem pode substituir seu próprio cérebro. Em geral, você não pode executar uma simulação se não entender como o circuito funciona.

6.2 Medições

Uma etapa extremamente importante no trabalho com um cristal são suas medições. É possível distinguir três tipos de medidas: tecnológica, funcional e elétrica. Os primeiros verificam que a planta não parou e que o cristal é tecnologicamente fabricado corretamente. Estes últimos verificam que a teoria (isto é, modelagem) converge com a prática (cristal real). , : , , . , , . , - . , . — , — . , … , , . .

, . , Fairchild 80- USB, . FORMULA "", . HP - Unix' . National Instruments , , , (). Agilent, . , ?) .

, -, , . , , , , Fairchild, , NI. , . - , , .

, , :

- , .

- . , .

- "" .

- , , , .

- .

- :

- /, , . /.

- , .

- , – . .

- , «» , .

- , .

, , .

. 4 (!) . , , . , ?) " ".

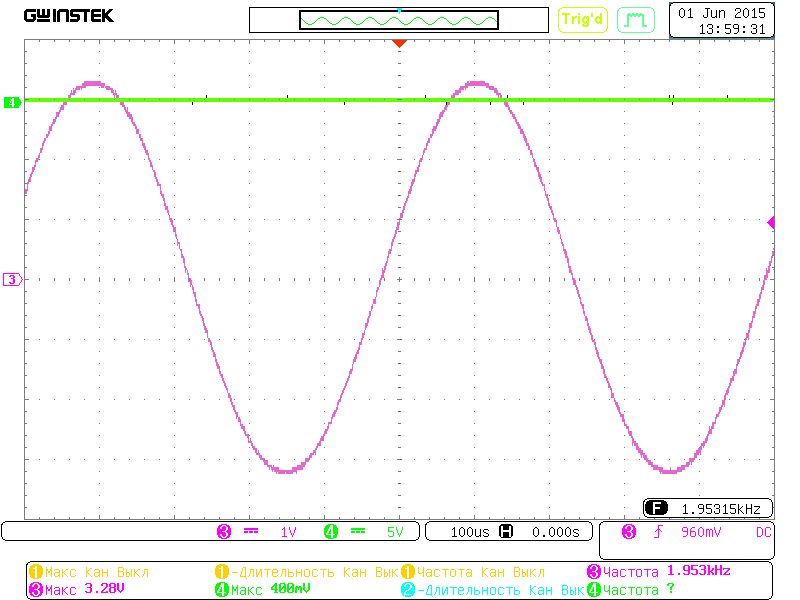

4. .

, . , , . 80 , , , , 8- .

, . :

5.

6.

, , .

, — . , . 8- . .

6.3

?

- ;

- NCO(numerically controlles oscillator);

- , , NCO ROM(cROM);

- ;

- :

- , ;

- ;

7. , HRT.

:

- — 83%.

- 14

- 11

- (sin & cos, 12 )

- 16

, , ? , . , - .

, . , . , — . .

7. ?

.

.

30 000 100 2. , " " . , , Setup&Hold, , Verilog' , , , — , , . , — , , , … . — , .

. .

-

MIT Massachusetts Institute of Technology

UZH Universität Zürich

ASIC Application specific integrated circuit

-- []

CORDIC Coordinate Rotation Digital Computer

-

NCO Numerically controlled oscillator

ROM Read-only memory

cROM Compressed ROM

- CORDIC IP Block Design, Vitaliy Kuhar, Stockholm, Sweden 2008

- CORDIC. , . . , . .

- Comparison of parallel and pipelined CORDIC algorithm using RCA and CSA, Guerrero, Meloni

- CORDIC for dummies.pdf

- Sine/Cosine using CORDIC Algorithm, Prof. Kris Gaj

- Lecture_cordic.pdf