O uso da arquitetura von Neumann para aplicativos com inteligência artificial é ineficiente. O que a substituirá?

Usar arquiteturas existentes para resolver os problemas de aprendizado de máquina (MO) e inteligência artificial (IA) tornou-se impraticável. A energia consumida pela IA cresceu significativamente e a CPU, juntamente com a GPU, parece cada vez mais ferramentas inadequadas para este trabalho.

Os participantes de vários simpósios concordaram que as melhores oportunidades para mudanças significativas surgem na ausência de recursos herdados que precisam ser arrastados. A maioria dos sistemas evoluiu gradualmente ao longo do tempo - e mesmo que isso garanta um progresso seguro, esse esquema não fornece soluções ideais. Quando algo novo aparece, torna-se possível dar uma nova olhada nas coisas e escolher uma direção melhor do que as tecnologias convencionais oferecerão. Isso é exatamente o que foi discutido em uma conferência recente, onde foi estudada a questão de saber se a estrutura complementar de metal-óxido-semicondutor (

CMOS ) é a melhor tecnologia básica na qual vale a pena criar aplicativos de IA.

Um Chen, nomeado pela IBM como diretor executivo da Nanoelectronics Research Initiative (NRI), preparou o terreno para a discussão. “Há muitos anos pesquisamos tecnologias novas e modernas, incluindo a busca de uma alternativa ao CMOS, principalmente por causa de seus problemas relacionados ao consumo de energia e à escala. Depois de todos esses anos, surgiu uma opinião de que não encontramos nada melhor como base para a criação de circuitos lógicos. Hoje, muitos pesquisadores estão se concentrando na IA, e ela realmente oferece novas formas de pensar e novos padrões, além de novos produtos tecnológicos. Os novos dispositivos de IA terão a capacidade de substituir o CMOS? ”

AI hoje

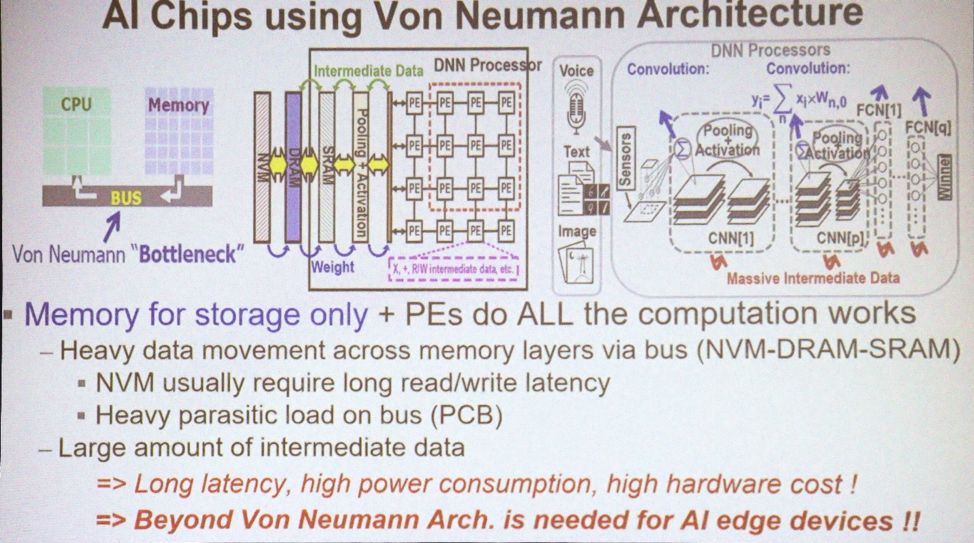

A maioria dos aplicativos para MO e AI usa a arquitetura von Neumann. "Ele usa memória para armazenar matrizes de dados e a CPU realiza todos os cálculos", explica Marvin Chen, professor de engenharia elétrica da Universidade Nacional de Xinhua. “Grandes quantidades de dados estão se movendo pelo barramento. Hoje, as GPUs também são frequentemente usadas para treinamento aprofundado, incluindo convolucionais [redes neurais]. Um dos principais problemas é o aparecimento de dados intermediários necessários para tirar conclusões. A movimentação de dados, especialmente além do chip, resulta em perda de energia e atrasos. Este é um gargalo de tecnologia. ”

Arquiteturas usadas para IA

Arquiteturas usadas para IAO que você precisa hoje é combinar processamento de dados e memória. "O conceito de computação na memória foi proposto por especialistas em arquitetura de computadores por muitos anos", diz Chen. - Existem vários esquemas para SRAM e memória não volátil, com os quais eles tentaram usar e implementar esse conceito. Idealmente, se isso der certo, você pode economizar uma enorme quantidade de energia, eliminando o movimento de dados entre a CPU e a memória. Mas isso é ideal. ”

Mas por hoje, não temos cálculos em mente. “Ainda temos a IA 1.0 usando a arquitetura von Neumann, porque os dispositivos de silício que implementam o processamento na memória nunca apareceram”, reclama. Chen "A única maneira de usar o 3D TSV de qualquer forma é usar a memória de alta velocidade com a GPU para resolver o problema de largura de banda". Mas ainda permanece um gargalo de energia e tempo ".

Haverá processamento de dados suficiente na memória para resolver o problema da perda de energia? "O cérebro humano contém cem bilhões de neurônios e 10

15 sinapses", disse Sean Lee, diretor assistente da Taiwan Semiconductor Manufacturing Company. "Agora observe o IBM TrueNorth." TrueNorth é um processador multinúcleo desenvolvido pela IBM em 2014. Possui 4.096 núcleos e cada um possui 256 neurônios artificiais programáveis. “Suponha que desejemos dimensioná-lo e reproduzir o tamanho do cérebro. A diferença é de 5 ordens de magnitude. Mas se apenas aumentarmos diretamente os números e multiplicarmos o TrueNorth, consumindo 65 mW, obteremos uma máquina com um consumo de 65 kW contra o cérebro de uma pessoa que consome 25 watts. O consumo deve ser reduzido em várias ordens de magnitude ".

Lee oferece outra maneira de imaginar essa oportunidade. "O supercomputador mais eficiente até hoje é o Green500 do Japão, emitindo 17 Gflops por watt ou 1

flop a 59 pJ". O site Green500 diz que o sistema ZettaScaler-2.2 instalado no Centro de Comunicações e Computação Avançada do Japão (RIKEN) mediu 18,4 Gflops / W durante a execução do teste Linpack, que exigiu 858 TFlops. “Compare isso com

o princípio de Landauer , segundo o qual, à temperatura ambiente, a energia mínima de comutação do transistor é da ordem de 2,75 zJ [10

-21 J]. Novamente, a diferença é de várias ordens de magnitude. 59 pJ é de cerca de 10

-11 contra a baixa teórica de cerca de 10

-21 . Temos um enorme campo de pesquisa ".

É justo comparar esses computadores com o cérebro? "Depois de examinar os sucessos recentes do treinamento aprofundado, veremos que, na maioria dos casos, pessoas e máquinas competem pelos últimos sete anos seguidos", diz Kaushik Roy, professor emérito de engenharia elétrica e ciência da computação da Universidade de Purdue. “Em 1997, o Deep Blue derrotou Kasparov, em 2011 o IBM Watson venceu o jogo Jeopardy! E em 2016 o Alpha Go derrotou Lee Sedola. Essas são as maiores conquistas. Mas a que custo? Essas máquinas consumiram 200 a 300 kW. O cérebro humano consome cerca de 20 watts. Enorme lacuna. De onde virá a inovação?

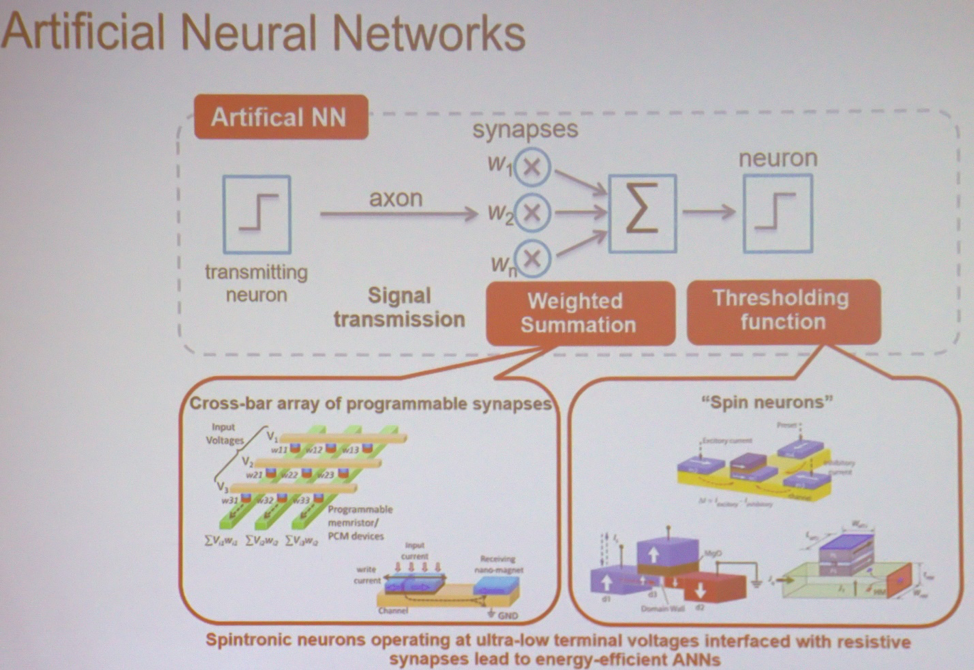

No coração da maioria das aplicações, MO e AI são os cálculos mais simples realizados em grande escala. "Se você usar a rede neural mais simples, ela realiza uma soma ponderada, seguida de uma operação de limite", explica Roy. - Isso pode ser feito em vários tipos de matrizes. Pode ser um dispositivo de spintronics ou memória resistiva. Nesse caso, a tensão de entrada e a condutividade resultante serão associadas a cada ponto de interseção. Na saída, você obtém a soma das tensões multiplicadas pela condutividade. Este é o atual. Em seguida, você pode usar dispositivos semelhantes que executam uma operação de limite. A arquitetura pode ser imaginada como um monte desses nós conectados entre si para realizar cálculos. ”

Os principais componentes da rede neural

Os principais componentes da rede neuralNovos tipos de memória

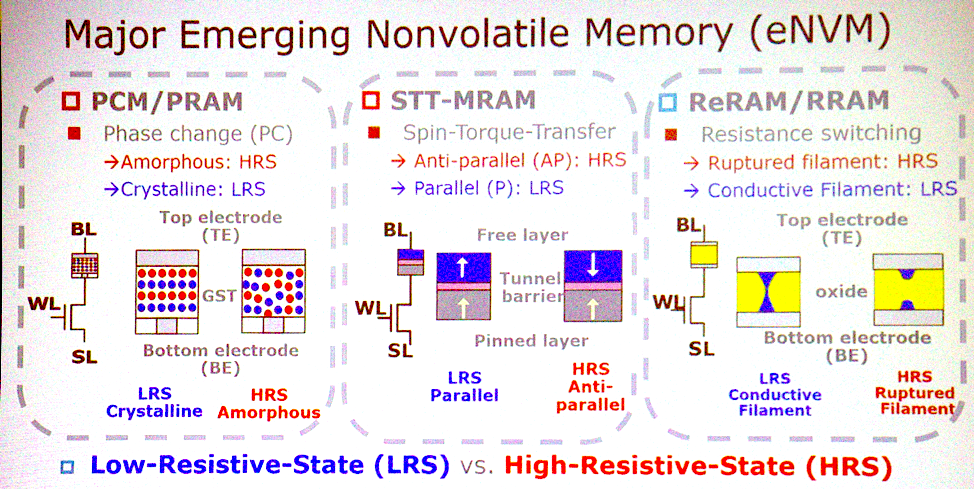

A maioria das arquiteturas em potencial está associada a tipos emergentes de memória não volátil. "Quais são as características mais importantes?" “Pergunta Jeffrey Barr, pesquisador da IBM Research. “Eu colocaria memória resistiva analógica não volátil, como memória com mudança de fase, memristores e assim por diante. A idéia é que esses dispositivos sejam capazes de fazer todas as multiplicações para camadas totalmente conectadas de redes neurais em um ciclo. Em um conjunto de processadores, isso pode levar um milhão de ciclos de relógio e, em um dispositivo analógico, isso pode ser feito usando a física que trabalha no local dos dados. Existem aspectos bastante interessantes em termos de tempo e energia para que essa idéia se transforme em algo mais ".

Novas tecnologias de memória

Novas tecnologias de memóriaChen concorda com isso. “PCM, STT tem lances sérios a ganhar. Esses três tipos de memória são bons candidatos à implementação da computação na memória. Eles são capazes de operações lógicas básicas. Algumas espécies têm problemas de confiabilidade e não podem ser usadas para treinamento, mas é possível chegar a uma conclusão ".

Mas pode acontecer que não seja necessário mudar para esta memória. "As pessoas estão falando sobre o uso da SRAM exatamente para o mesmo objetivo", acrescenta Lee. "Eles fazem computação analógica com SRAM." O único aspecto negativo é que a SRAM é muito grande - 6 ou 8 transistores por bit. Portanto, não é fato que usaremos essas novas tecnologias na computação analógica. ”

A transição para a computação analógica também implica que a precisão dos cálculos não será mais uma necessidade. "A IA é especializada, classifica e prevê", diz ele. "Ele toma decisões que podem ser rudes." Em termos de precisão, podemos desistir de algo. Precisamos determinar quais cálculos são resistentes a erros. Em seguida, algumas tecnologias podem ser aplicadas para reduzir o consumo de energia ou acelerar a computação. O CMOS probabilístico trabalha desde 2003. Isso inclui diminuir a tensão até o aparecimento de vários erros, cujo número permanece tolerável. Hoje, as pessoas já estão usando técnicas de cálculo aproximadas, como quantização. Em vez de um número de ponto flutuante de 32 bits, você terá números inteiros de 8 bits. Computadores analógicos são outro recurso já mencionado. ”

Saia do laboratório

Mover a tecnologia do laboratório para o público pode ser um desafio. "Às vezes você precisa procurar alternativas", diz Barr. - Quando a memória flash bidimensional não decolou, a memória flash tridimensional começou a parecer uma tarefa tão difícil. Se continuarmos a melhorar as tecnologias existentes, obtendo uma duplicação de características aqui, duplicando ali, os cálculos analógicos dentro da memória serão abandonados. Mas se as seguintes melhorias forem insignificantes, a memória analógica parecerá mais atraente. Como pesquisadores, devemos estar preparados para novas oportunidades. ”

A economia geralmente desacelera o desenvolvimento, especialmente na área da memória, mas Barr diz que isso não acontecerá neste caso. “Uma das nossas vantagens é que este produto não será relacionado à memória. Não será algo com pequenas melhorias. Este não é um produto de consumo. Isso é algo que compete com a GPU. Eles são vendidos a um preço 70 vezes o custo da DRAM colocado sobre eles, portanto esse é claramente um produto sem memória. E o custo do produto não será muito diferente da memória. Parece bom, mas quando você toma decisões no valor de bilhões de dólares, todos os custos e o plano de desenvolvimento de produtos devem ficar claros. Para superar essa barreira, precisamos oferecer protótipos impressionantes. ”

Substituição CMOS

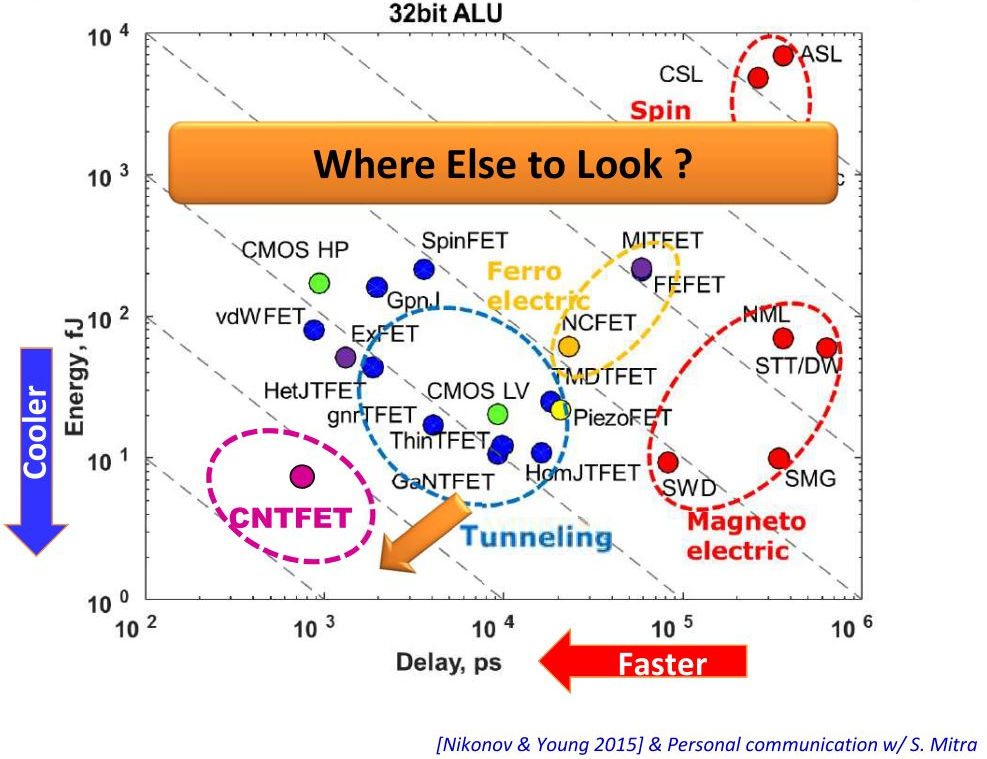

O processamento de dados na memória pode fornecer benefícios impressionantes, mas é necessário mais para implementar a tecnologia. Qualquer outro material além do CMOS pode ajudar nisso? "Observando a transição do CMOS de baixo consumo para os FETs de túnel, estamos falando de uma redução de 1-2 vezes no consumo", diz Lee. - Outra possibilidade são os circuitos integrados tridimensionais. Eles reduzem o comprimento da fiação usando o TSV. Isso reduz o consumo de energia e a latência. Olhe para os data centers, todos eles removem a fiação metálica e conectam a óptica ".

Vertical - consumo de energia, horizontal - atrasos no dispositivo

Vertical - consumo de energia, horizontal - atrasos no dispositivoEmbora você possa obter alguns benefícios ao mudar para uma tecnologia diferente, eles podem não valer a pena. "Será muito difícil substituir o CMOS, mas alguns dos dispositivos discutidos podem complementar a tecnologia CMOS para que ele faça cálculos na memória", diz Roy. - O CMOS pode suportar cálculos na memória em forma analógica, possivelmente na célula 8T. É possível criar uma arquitetura com uma clara vantagem sobre o CMOS? Se tudo for feito corretamente, o CMOS me proporcionará milhares de vezes mais eficiência energética. Mas isso leva tempo.

Claramente, o CMOS não será substituído. “As novas tecnologias não rejeitarão as antigas e não serão fabricadas em outros substratos além do CMOS”, conclui Barr.