Olá

O artigo analisa a arquitetura do sistema de memória virtual ARMv7.

Título de spoilerAs sutilezas de armazenamento em cache, DMA, LPAE e similares não são consideradas aqui. Para uma descrição mais detalhada, consulte a literatura no final do artigo.

1. Introdução

O sistema de memória virtual executa várias tarefas. Em primeiro lugar, ele permite que você coloque os processos do usuário em espaços de memória separados e isolados um do outro. Isso permite aumentar a confiabilidade do sistema, os erros de um processo não afetam a operação de outros processos. Em segundo lugar, o sistema operacional pode fornecer ao processo mais memória do que o sistema possui. As páginas de memória não utilizadas são colocadas no armazenamento permanente e as necessárias são carregadas a partir daí, formando a ilusão de uma quantidade maior de memória do que realmente é. Em terceiro lugar, o espaço virtual contínuo facilita a gravação de software personalizado. Todos os processos são executados no mesmo espaço, o sistema operacional oculta a configuração real da memória no sistema.

Definições

As seguintes definições são usadas no artigo:

Endereço virtual - o endereço usado pelo núcleo do processador. O ponteiro da pilha, o contador de instruções e o registro de retorno usam um endereço virtual.

Endereço físico - O endereço de saída no barramento do processador.

Uma página é uma unidade de endereçamento de memória virtual.

Seção - um análogo da página, tem um tamanho maior.

Um quadro é uma unidade de endereçamento de memória física.

Tabela de páginas - uma matriz de registros para traduzir endereços.

ASID é o identificador do espaço de endereço.

TLB - buffer de tradução rápida de endereços.

MMU é uma unidade de gerenciamento de memória.

TLB

O TLB é um buffer de hardware muito rápido que contém os resultados das últimas traduções de endereços. A solicitação do kernel para converter o endereço da página e o ASID atual chega no TLB. Se houver uma entrada válida, as permissões para acessar esta memória são verificadas, o método de acesso e o endereço de quadro correspondente são retornados à MMU. Se o acesso à memória for negado, uma exceção de hardware será lançada. Se um erro TLB ocorreu (nenhum registro foi encontrado), o comportamento adicional diferencia maiúsculas de minúsculas pelo TTBCR. Uma pesquisa pode ser feita nas tabelas de páginas ou uma exceção é lançada.

É importante observar que, ao manipular tabelas de páginas, você deve redefinir corretamente o TLB, porque informações irrelevantes podem ser armazenadas lá.

A atualização de entradas no TLB é transparente para o programador round-robin.

Também é possível fazer o upload e garantir algumas entradas no TLB para evitar que elas sejam excluídas.

Figura 1. TLB

Figura 1. TLBTabelas de Páginas

O ARMv7 é uma arquitetura de 32 bits, por isso temos 4 GB de memória virtual endereçável.

As tabelas de páginas são divididas em 2 níveis - L1 e L2.

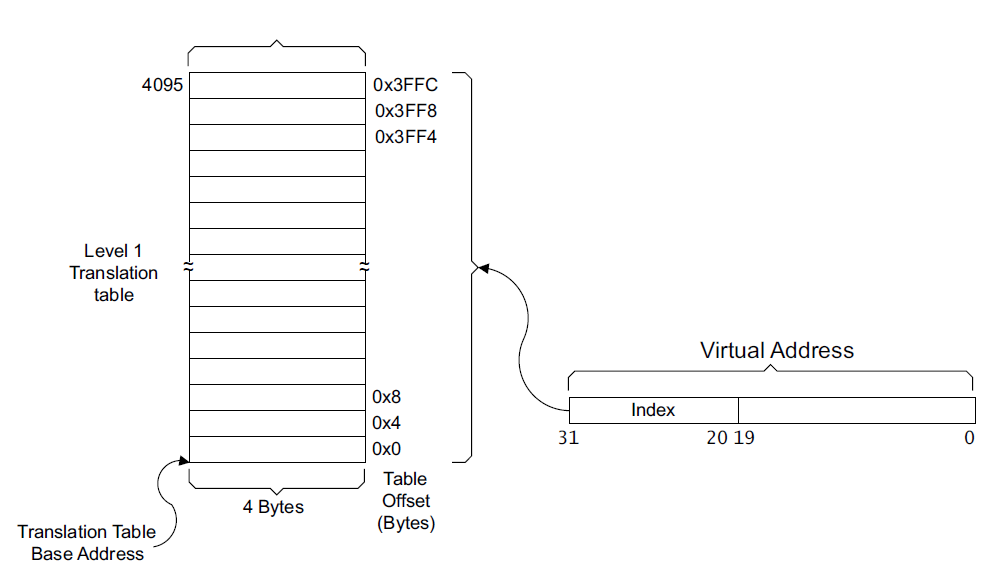

A tabela L1 descreve todos os 4 GB de espaço de endereço. Consiste em 4096 registros de 32 bits, cada um dos quais descreve 1 Mb. As entradas na tabela são selecionadas pelos 12 bits mais altos do endereço virtual.

Fig. 2 Pesquise entradas na tabela L1

Fig. 2 Pesquise entradas na tabela L1A tabela L1 está localizada na memória física e alinhada a uma borda de 16 KB. Existem 4 opções para essas entradas: para descrever páginas, seções e superseções. Bem, um registro vazio, para memória que ainda não está mapeada.

Fig. 3 Tipos de entradas em L1

Fig. 3 Tipos de entradas em L1Os bits 0 e 1 indicam o tipo de registro 00b-Falha, 01b é o descritor da página, 10b é o descritor da seção (e superseção).

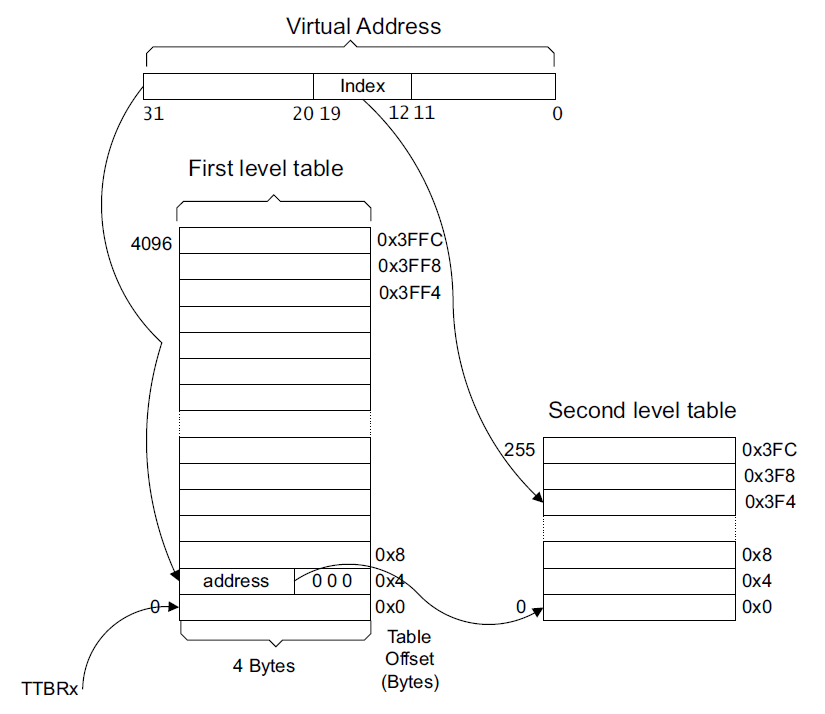

Se a memória física for paginada, a tabela L1 armazenará o endereço da tabela L2 (física, alinhada a 1Kb). O bit 9 é determinado pelo fabricante (Implementação definida), bits [8: 5] - para o mecanismo de domínio (Descontinuado no ARMv7), SBZ - zeros.

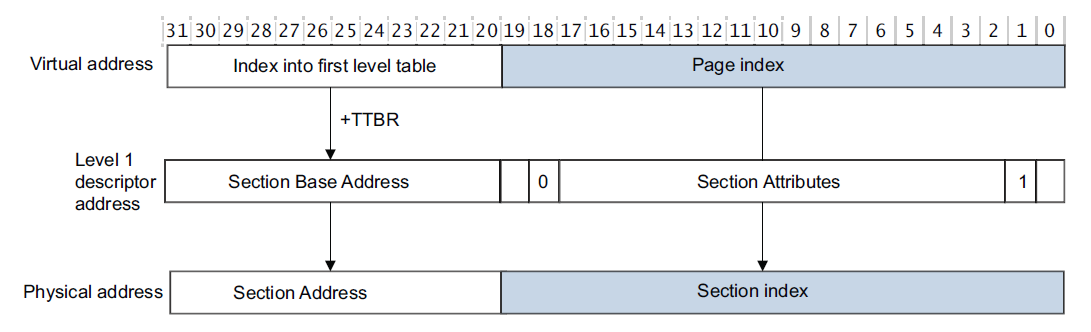

Se decidirmos dividir a memória em seções, em L1 é necessário escrever o endereço físico correspondente. A seção se refere diretamente à área de memória física alinhada de 1 MB. Não há necessidade da tabela L2. A substituição é um caso especial de particionamento, a entrada na tabela L1 deve ser repetida 16 vezes, o alinhamento dos blocos alocados de memória física e virtual também é de 16 MB.

A tabela L2 consiste em 256 entradas de 32 bits. Deve estar alinhado a 1Kb.

Fig. 4 Pesquise entradas na tabela L2

Fig. 4 Pesquise entradas na tabela L2Os índices na tabela L2 são formados a partir da média de 8 bits [19:12] do endereço virtual. Cada entrada da tabela contém o endereço do quadro.

Fig. 5 Tipos de entradas em L2

Fig. 5 Tipos de entradas em L2As páginas podem ter dois tamanhos: 64 KB (página grande) e 4Kb (página pequena).

Os bits AP e APX definem permissões de leitura / gravação no modo privilegiado / não privilegiado (kernel / usuário). Os bits TEX, C, B, S são responsáveis pelo tipo de memória, seu cache e buffer de leitura e gravação. O bit nG - nonGlobal permite acesso à página para todos os processos ou apenas para um ASID específico.

O uso de páginas grandes reduz o número de entradas no TLB. Em vez de 16 entradas (4Kb * 16 = 64Kb), apenas uma será armazenada lá. No entanto, 16 entradas idênticas devem ser inseridas na tabela L2.

A capacidade de endereçar diferentes tamanhos de blocos permite, por um lado, alocar memória com a granularidade desejada, por outro lado, reduzir o número de chamadas para tabelas de páginas em uma memória relativamente lenta.

Registros

Para controlar o sistema (incluindo o MMU) na arquitetura ARM, um coprocessador CP15 especial é projetado. Para o gerenciamento de memória, há uma dúzia e meia de seus registros. Estamos interessados em vários deles - Control, TTBR0 / 1, TTBCR, ContextID.

No registro de controle, o bit menos significativo é responsável por ativar / desativar o MMU, tudo é simples.

O par de registros TTBR0 / 1 contém os endereços físicos das tabelas do primeiro nível. Nesses endereços, o MMU começa a procurar a página desejada.

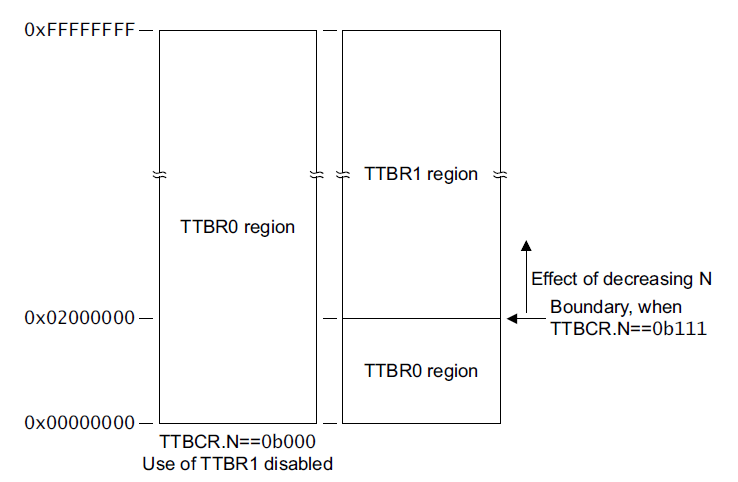

O registro TTBCR permite dividir todo o espaço de endereço em 2 partes entre TTBR0 e TTBR1. Cada um deles transmitirá sua parte dos endereços. Os bits [2: 0] são usados para definir o tamanho. O número gravado (de 0 a 7 decimal) mascara a parte mais antiga dos endereços virtuais. Se o seu valor for "0", todos os endereços são transmitidos via TTBR0. Se "1", os endereços de 31 bits são mascarados e os 2 GB de espaço virtual inferior passam pelo TTBR0, os superiores pelo TTBR1. "2" - 31 e 30 bits são mascarados e a divisão em 1 GB e 3 GB é obtida, respectivamente. Assim, a parte inferior dos endereços pode ser usada para aplicativos do usuário, sobrecarregando o registro TTBR0 para um novo processo, e a parte superior pode ser deixada para as necessidades do sistema.

Fig. 6 Espaço de endereço dividido

Fig. 6 Espaço de endereço divididoOs bits [5: 4] são responsáveis pelo comportamento de falta do TLB - pesquise nas tabelas de páginas ou uma exceção.

O registro ContextID contém o campo ASID para o processo atual. Ele deve ser alterado juntamente com o conteúdo do registro TTBR0 ao alterar o contexto.

Tradução de endereços

O algoritmo para converter endereços virtuais em físicos é o seguinte:

- Procure o endereço virtual solicitado e o ASID no buffer TLB

- Se o TLB não tiver o endereço necessário, será realizada uma pesquisa de hardware nas tabelas de páginas

Se o kernel solicitou anteriormente uma página virtual, ela será armazenada no TLB. Nesse caso, o MMU o remove do cache e nada precisa ser feito. Se a página for solicitada pela primeira vez (ou forçada a partir daí - o TLB não é muito grande), a pesquisa nas tabelas L1-L2 é realizada. Assim, o mapeamento dos endereços virtuais e físicos é o seguinte:

- No registro TTBR0 \ TTBR1, o endereço da tabela L1 é pesquisado.

- Os 10 bits principais do endereço virtual formam um índice na tabela.

- a) Se o registro corresponder à seção (supersecção), os atributos da seção serão verificados e, se estiver tudo bem, o endereço físico resultante será composto pelo endereço base da seção (supersecção) e pelos 20 (24) bits inferiores do endereço virtual.

Título de spoiler Fig. 7 Tradução de endereços em superseção

Fig. 7 Tradução de endereços em superseção

b) Se o registro for uma tabela L2, a pesquisa continuará nela. A parte do meio do endereço virtual da página forma o índice da tabela.

Título de spoiler Fig. 8 Tradução de endereços na tabela L2

Fig. 8 Tradução de endereços na tabela L2

- Atualização do TLB em andamento

No total, o subsistema de memória virtual consiste nas seguintes partes:

- Vários Registradores de Controle CP15

- Tabelas de páginas que contêm regras de conversão de endereço

- TLB - cache de transmissões bem-sucedidas

- MMU é uma unidade de conversão de endereço.

Literatura

Manual de referência da arquitetura ARM Edição ARMv7-A e ARMv7-R

Guia do programador da série ARM Cortex-A