Modernas tecnologias microeletrônicas - como "Dez Pequenos Índios". O custo do desenvolvimento e do equipamento é tão grande que, a cada novo passo em frente, alguém cai. Após as notícias sobre a GlobalFoundries se recusarem a desenvolver 7 nm, restavam três: TSMC, Intel e Samsung. E o que exatamente são "padrões de design" e onde está esse tamanho muito estimado de 7 nm? E ele está aí?

Figura 1. Transistor Fairchild FI-100, 1964.Os primeiros transistores MOS seriais entraram no mercado em 1964 e, como os leitores sofisticados podem ver no desenho, eles

quase não eram diferentes dos mais modernos ou menos modernos - exceto pelo tamanho (veja o fio em escala).

Por que reduzir o tamanho dos transistores? A resposta mais óbvia a essa pergunta é chamada lei de Moore e afirma que a cada dois anos o número de transistores em um chip deve ser dobrado, o que significa que as dimensões lineares dos transistores devem diminuir em um fator de dois. "Deve" - de acordo com as observações de Gordon Moore (e alguns outros engenheiros) nos anos setenta. Da lei de Moore, existem muitos outros fatores que compõem o roteiro de microeletrônica da ITRS. A formulação mais simples e aproximada de métodos para implementar a lei de Moore (também conhecida como lei de miniaturização de Dennard) é que um aumento no número de transistores em um chip não deve levar a um aumento na densidade do consumo de energia, ou seja, com uma diminuição no tamanho dos transistores, a tensão de alimentação e a corrente de operação devem ser proporcionalmente reduzidas.

A corrente através do transistor MOS é proporcional à razão entre sua largura e comprimento, o que significa que podemos manter a mesma corrente, reduzindo proporcionalmente esses dois parâmetros. Além disso, reduzindo o tamanho do transistor, também reduzimos a capacitância da porta (proporcional ao produto do comprimento e largura do canal), tornando o circuito ainda mais rápido. Em geral, em um circuito digital, praticamente não há razão para aumentar o tamanho dos transistores. A seguir, começam as nuances de que, nos transistores lógicos de canal p, geralmente são um pouco mais amplos que os de canal n, a fim de compensar a diferença na mobilidade dos portadores de carga, e na memória, pelo contrário, os transistores de canal n são mais amplos, de modo que a memória pode ser escrita normalmente através de uma chave não complementar, mas realmente nuances e globalmente - quanto menor o tamanho do transistor - melhor para os circuitos digitais.

É por isso que o comprimento do canal sempre foi o menor tamanho na topologia do microcircuito e a designação de designação mais lógica.

Deve-se notar aqui que o raciocínio acima sobre tamanho não é válido para circuitos analógicos. Por exemplo, agora, no segundo monitor do meu computador, há um par de transistores usando a tecnologia de 150 nm, 32 peças com 8/1 mícrons de tamanho. Isso é feito para garantir a identidade desses dois transistores, apesar da variação tecnológica dos parâmetros. A área é de importância secundária.Tecnólogos e topólogos têm o chamado sistema lambda de tamanhos típicos de topologia. É muito conveniente para estudar design (e foi inventado na Universidade de Berkeley, se não me engano) e transferir projetos de fábrica para fábrica. De fato, essa é uma generalização de tamanhos típicos e limitações tecnológicas, mas um pouco áspera, para que funcione exatamente em qualquer fábrica. No exemplo dela, é conveniente observar os tamanhos típicos dos elementos no chip. Os princípios no núcleo do sistema lambda são muito simples:

- se a troca de elementos em duas máscaras fotolitográficas diferentes tiver consequências catastróficas (por exemplo, um curto-circuito), a margem de tamanhos para evitar inconsistências deve ser de pelo menos duas lambdas;

- se a mudança de elementos tiver consequências indesejáveis, mas não catastróficas, a margem de tamanho deve ser de pelo menos um lambda;

- o tamanho mínimo permitido das janelas de máscara fotográfica é de duas lambdas.

Do terceiro parágrafo, segue-se, em particular, que lambda em tecnologias antigas é metade da norma de design (mais precisamente, o comprimento do canal do transistor e as normas de design são duas lambdas).

Figura 2. Um exemplo de uma topologia executada por um sistema lambda.O sistema lambda funcionou perfeitamente nos antigos padrões de design, permitindo transferir convenientemente a produção de fábrica para fábrica, organizar fornecedores de segundo chip e fazer coisas muito mais úteis. Porém, com o aumento da concorrência e o número de transistores em um chip, as fábricas começaram a se esforçar para tornar a topologia um pouco mais compacta. Portanto, agora você não pode atender às regras de design correspondentes a um sistema lambda "limpo", exceto nas situações em que os desenvolvedores os ásperam independentemente, tendo em vista a probabilidade de produção chip em diferentes fábricas. No entanto, ao longo dos anos, a indústria desenvolveu uma conexão direta “padrões de projeto = comprimento do canal do transistor”, que existia com sucesso até os transistores atingirem dezenas de nanômetros.

Figura 3. Seção esquemática do transistor.Esta figura mostra uma seção MUITO simplificada de um transistor plano (plano) convencional, mostrando a diferença entre o comprimento do canal topológico (Ldrawn) e o comprimento efetivo do canal (Leff). De onde vem a diferença?

Falando em tecnologia microeletrônica, a fotolitografia é quase sempre mencionada, mas com muito menos frequência são outras operações tecnológicas menos importantes: gravação, implantação de íons, difusão etc. etc. Para nossa conversa com você, um lembrete de como a difusão e a implantação de íons funciona não é supérfluo.

Figura 4. Comparação de difusão e implantação de íons.Com a difusão, tudo é simples. Você pega uma pastilha de silício na qual é aplicado previamente (com a ajuda da fotolitografia), cobrindo com óxido de silício os locais onde a impureza não é necessária e abrindo aqueles onde é necessário. Em seguida, você precisa colocar a impureza gasosa na mesma câmara com o cristal e o calor a uma temperatura na qual a impureza começa a penetrar no silício. Ajustando a temperatura e a duração do processo, é possível atingir a quantidade e a profundidade desejadas de impurezas.

O óbvio menos a difusão é que a impureza penetra no silício em todas as direções da mesma maneira, para baixo e para aquele lado, reduzindo assim o comprimento efetivo do canal. E agora estamos falando de centenas de nanômetros! Embora os padrões de projeto fossem medidos em dezenas de mícrons, tudo estava bem, mas é claro que esse estado de coisas não poderia durar muito e a difusão foi substituída pelo implante de íons.

Durante a implantação de íons, um feixe de íons de impureza acelera e é direcionado para uma pastilha de silício. Nesse caso, todos os íons se movem em uma direção, o que praticamente elimina a propagação para os lados. Em teoria, é claro. Na prática, os íons, no entanto, se afastam um pouco, embora a distâncias muito mais curtas do que durante a difusão.

No entanto, se retornarmos ao padrão do transistor, veremos que a diferença entre o comprimento topológico e efetivo do canal começa precisamente por causa dessa pequena fluência. Ela, em princípio, poderia ser negligenciada, mas não é a única razão para a diferença. Ainda existem efeitos de canal curto. Existem cinco deles e, de várias maneiras, eles alteram os parâmetros do transistor se o comprimento do canal se aproximar de várias restrições físicas. Não vou descrever todos eles, vou me debruçar sobre os mais relevantes para nós - DIBL (redução de barreira induzida pelo dreno, diminuição induzida pelo dreno na barreira potencial).

Para entrar na pia, um elétron (ou orifício) deve superar a barreira potencial da junção pn da pia. A tensão do portão reduz essa barreira, controlando a corrente através do transistor, e queremos que a tensão do portão seja a única tensão de controle. Infelizmente, se o canal do transistor for muito curto, a junção pn de dreno começa a influenciar o transistor, o que reduz a tensão dos poros (veja a figura abaixo) e, em segundo lugar, a tensão no transistor começa a afetar não apenas a tensão do portão , mas também no dreno, porque a espessura da junção pn do dreno aumenta proporcionalmente à tensão no dreno e, consequentemente, reduz o canal.

Figura 5. Efeito de redução de barreira induzida pelo dreno (DIBL).

Fonte - Wikipedia.Além disso, uma diminuição no comprimento do canal leva ao fato de que os transportadores de carga começam a passar livremente da fonte para o dreno, ignorando o canal e gerando uma corrente de fuga (corrente ruim na figura abaixo), que também é consumo de energia estática, cuja ausência foi uma das razões importantes para o sucesso inicial do CMOS. tecnologias, bastante inibitórias em comparação com os concorrentes bipolares da época. De fato, cada transistor na tecnologia moderna possui um resistor paralelo a ele, cujo valor é menor, menor o comprimento do canal.

Figura 6. O aumento no consumo estático devido a vazamentos nas tecnologias de canal curto.

Fonte - Sinopse.Figura 7. A proporção do consumo de energia estática dos microprocessadores em diferentes padrões de design.

Fonte - B. Dieny et. al., “Efeito de transferência de spin e seu uso em componentes spintrônicos”, International Journal of Nanotechnology, 2010Agora, como você pode ver na figura acima, o consumo estático excede significativamente a dinâmica e é um obstáculo importante à criação de circuitos de baixa potência, por exemplo, para eletrônicos vestíveis e a Internet das coisas. Na verdade, mais ou menos na época em que isso se tornou um problema importante, o marketing muhlezh com padrões de design começou, porque o progresso na litografia começou a superar o progresso na física.

Para combater os efeitos indesejáveis do canal curto nos padrões de projeto de 800-32 nanômetros, muitas soluções tecnológicas diferentes foram inventadas, e não vou descrevê-las todas, caso contrário, o artigo aumentará para tamanhos muito indecentes, mas a cada nova etapa eu tive que introduzir novas soluções - adicionais dopagem de áreas adjacentes às junções pn, dopagem em profundidade para evitar vazamentos, transformação local de silício em transistores em silício-germânio ... Não foi feito um único passo na redução do tamanho dos transistores. oh sim.

Figura 8. O comprimento efetivo do canal em tecnologias de 90 nm e 32 nm. Os transistores são disparados na mesma escala. Os semicírculos nas figuras são uma forma de correspondência fraca adicional de drenos (LDD, dreno levemente dopado), feitos para reduzir a largura das junções pn.

Fonte - Sinopse.Os tamanhos típicos de metalização e as distâncias entre os elementos durante a transição de 90 nm para cerca de 28 nm diminuíram em proporção a uma diminuição na norma de projeto, ou seja, o tamanho típico da próxima geração foi de 0,7 em relação à anterior (de modo que, de acordo com a lei de Moore, uma redução de área em duas vezes). Ao mesmo tempo, o comprimento do canal diminuiu, na melhor das hipóteses, em 0,9 em relação à geração anterior, e o comprimento efetivo do canal praticamente não mudou. É claramente visto na figura acima que as dimensões lineares dos transistores não mudaram três vezes, de 90 nm para 32 nm, e todos os jogos dos tecnólogos estavam em torno de reduzir a sobreposição de obturador e áreas dopadas, bem como em torno do controle de vazamentos estáticos, que não eram permitidos. o canal é mais curto.

Como resultado, duas coisas ficaram claras:

- ir abaixo de 25-20 nm sem uma inovação tecnológica não funciona;

- tornou-se cada vez mais difícil para os profissionais de marketing desenhar uma imagem do progresso da tecnologia com a lei de Moore.

A lei de Moore é geralmente um tópico controverso, porque não é uma lei da natureza, mas uma observação empírica de alguns fatos da história de uma empresa em particular, extrapolada para o progresso futuro de todo o setor. Na verdade, a popularidade da lei de Moore está indissociavelmente ligada aos profissionais de marketing da Intel, que fizeram dela sua bandeira e, de fato, impulsionaram o setor por muitos anos, forçando-o a cumprir a lei de Moore, onde talvez valesse a pena esperar um pouco.Como é que os profissionais de marketing descobriram a situação? Muito elegante.

O comprimento do canal do transistor é bom, mas como você pode estimar o ganho na área dele, o que dá a transição para novos padrões de design? Há muito tempo, a indústria usava a área de uma célula de memória de seis transistores, o bloco de construção de microprocessador mais popular. São essas células que geralmente consistem em uma memória cache e em um arquivo de registro que podem ocupar metade de um cristal, e é por isso que o esquema e a topologia de uma célula de seis transistores sempre são cuidadosamente lambidos até o limite (geralmente pessoas especiais que fazem isso), então essa é uma medida realmente boa. densidade de embalagem.

Figura 9. Esquema de uma célula de memória estática de seis transistores.Figura 10. Diferentes opções de topologia para uma célula de memória estática de seis transistores. Fonte - G. Apostolidis et. al., “Design e simulação de arquiteturas de células 6T SRAM em tecnologia de 32 nm”, Journal of Engineering Science and Technology Review, 2016Portanto, durante muito tempo nas descrições das tecnologias, o número de padrões de design foi acompanhado pela segunda figura - a área da célula de memória, que, em teoria, deveria ser derivada do comprimento do canal. E depois houve uma substituição interessante de conceitos. Em um momento em que o dimensionamento direto parou de funcionar e o comprimento do canal parou de diminuir a cada dois anos, de acordo com a lei de Moore, os profissionais de marketing perceberam que é possível não derivar a área da célula da memória das normas de design, mas derivar o número de normas de design da área da célula da memória!

Ou seja, naturalmente “costumávamos ter um comprimento de canal de 65 nm e uma área de células de memória de X, e agora o comprimento de canal é de 54 nm, mas pressionamos a metalização, e agora a área de células se tornou X / 5, o que corresponde aproximadamente a uma transição de 65 para 28 nm. Então, vamos dizer a todos que temos padrões de design de 28 nm e não contaremos a ninguém sobre o comprimento do canal de 54 nm? " Para ser justo, “metalização ardente” também é uma conquista importante e, por algum tempo após o início de problemas com a miniaturização dos próprios transistores, a largura mínima de metalização, o tamanho do contato com o transistor ou alguma outra figura na topologia correspondeu aos padrões de projeto declarados. Mas então as danças começaram com os transistores FinFET, nos quais as principais dimensões nada tinham a ver com a resolução da litografia, as taxas de miniaturização dos transistores e tudo o mais finalmente divergiram, e a área da célula de memória permaneceu a única figura normal, com base na qual agora somos informados sobre "10", " 7 "e" 5 "nanômetros.

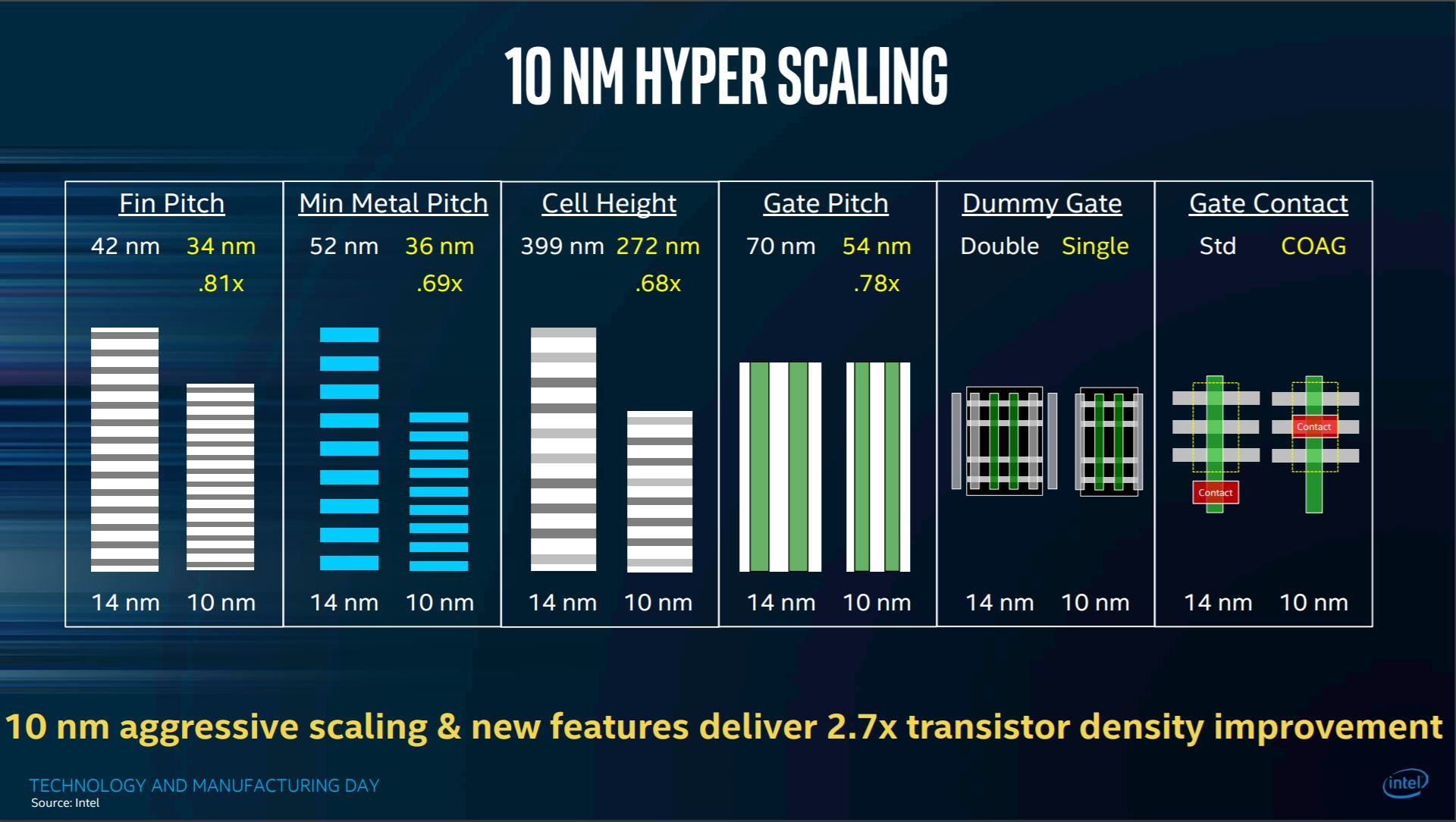

Fonte - Intel.Aqui está um ótimo exemplo dessa "nova escala". Somos mostrados como os tamanhos das características na célula da memória mudaram. Muitos parâmetros, mas nem uma palavra sobre o comprimento e a largura do canal do transistor!

Como eles resolveram o problema da impossibilidade de reduzir o comprimento do canal e controlar o vazamento de tecnologia?

Eles encontraram duas maneiras. O primeiro está na testa: se a causa dos vazamentos for uma grande profundidade de implantação, vamos reduzi-la, de preferência radicalmente. A tecnologia de silício em um isolador (SIC) é conhecida há muito tempo (e tem sido usada ativamente todos esses anos, por exemplo, nos processadores AMD de 130 a 32 nm, no processador set-top box Sony Playstation 3 de 90 nm e nos aparelhos eletrônicos de radiofreqüência, energia ou espaço), mas com uma diminuição nos padrões de design, ela teve uma segunda chance.

Figura 12. Comparação de transistores feitos usando as tecnologias volumétricas convencionais e FDSOI (SOI totalmente esgotada).

Fonte - ST Microelectronics .Como você pode ver, a idéia é mais do que elegante - o óxido está localizado sob uma camada ativa muito fina, eliminando a corrente de fuga prejudicial na videira! Ao mesmo tempo, devido a uma diminuição na capacidade das junções pn (quatro dos cinco lados do cubo de drenagem foram removidos), a velocidade aumenta e o consumo de energia diminui. É por isso que agora a tecnologia FDSOI 28-22-20 nm é anunciada ativamente como uma plataforma para a Internet das coisas - o consumo é realmente reduzido várias vezes, se não por uma ordem de magnitude. E, no entanto, essa abordagem permite no futuro escalar o transistor plano convencional para um nível de 14-16 nm, o que a tecnologia volumétrica não permitirá mais.

No entanto, o FDSOI não cai especialmente abaixo de 14 nm, e a tecnologia também tem outros problemas (por exemplo, o terrível alto custo dos substratos SOI), em relação aos quais a indústria encontrou outra solução - os transistores FinFET. A idéia de um transistor FinFET também é bastante elegante. Queremos que a maior parte do espaço entre o dreno e a fonte seja controlada pelo obturador? Então, vamos cercar este espaço com um obturador de todos os lados! Bem, nem todos, três serão suficientes.

Figura 13. Estrutura do FinFET.

Fonte - A. Tahrim et.al., “Análise de Projeto e Desempenho de Células de 1-Bit FinFET Full Adder para Região Sub-limiar na Tecnologia de Processo de 16 nm”, Journal of Nanomaterials, 2015Figura 14. Comparação do consumo de energia de diferentes opções do somador feitas em transistores planares e no FinFET.

Fonte - A. Tahrim et.al., “Análise de Design e Desempenho de Células de 1-Bit FinFET Full Adder para Região Sub-limiar na Tecnologia de Processo de 16 nm”, Journal of Nanomaterials, 2015No FinFET, o canal não é plano e está localizado diretamente abaixo da superfície do substrato, mas forma uma barbatana vertical (Fin é a barbatana), projetando-se acima da superfície e cercada por um obturador em três lados. Assim, todo o espaço entre o dreno e a fonte é controlado por um obturador, e os vazamentos estáticos são bastante reduzidos. Os primeiros FinFETs a serem produzidos em massa foram a Intel nos padrões de design de 22 nm, o restante foi puxado por outros fabricantes de ponta, incluindo um apologista da KNI como a Global Foundries (antiga AMD).

A verticalidade do canal no FinFET, entre outras coisas, permite economizar na área da célula, porque o FinFET com um canal amplo é bastante estreito na projeção, e isso, por sua vez, novamente ajudou os profissionais de marketing com suas histórias sobre a área da célula de memória e sua dupla redução a cada novo etapa "padrões de projeto", não mais vinculada às dimensões físicas do transistor.Figura 15. Topologias de diferentes opções para células de memória (5T-9T) em tecnologia com FinFET. Fonte - M. Ansari et. al., “Uma célula SRAM 7T de limite próximo, com altas margens de gravação e leitura e baixo tempo de gravação para tecnologias FinFET abaixo de 20 nm”, o VLSI Journal on Integration, volume 50, junho de 2015.Aqui estão exemplos de opções diferentes para células de memória na tecnologia com FinFET. Veja como a largura geométrica do canal é muito menor que o comprimento? Você também pode ver que, apesar de todas as perturbações, o sistema lambda entre os topologistas ainda está sendo usado para estimativas quantitativas. E os números absolutos?Figura 16. Alguns tamanhos de transistores nas tecnologias de 14-16 nm.

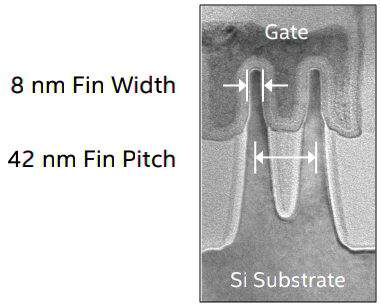

Fonte - os anais da conferência ConFab 2016.Como pode ser visto na figura, o comprimento do canal topológico nas tecnologias FinFET de 16 nm ainda é maior que os 20-25 nm, mencionados acima. E isso é lógico, porque a física não pode ser enganada. Porém, outra conclusão mais interessante pode ser tirada da mesma figura: se você olhar de perto, fica claro que o tamanho mínimo disponível nos transistores não é o comprimento do canal, mas a largura da aleta. E aqui uma descoberta engraçada nos espera: a largura da barbatana no processo de fabricação da Intel de 16 nm é (rolo de bateria!) OITO nanômetros. Figura 17. Dimensões da aleta na tecnologia de processo Intel de 14 nm.

Figura 17. Dimensões da aleta na tecnologia de processo Intel de 14 nm.

Fonte - wikichip.orgComo você pode ver, aqui os profissionais de marketing, apegados ao tamanho da célula da memória, se enganaram e agora são forçados a expressar a figura mais do que podiam. De fato, é claro, em condições de uma mudança fundamental na estrutura do transistor e na expectativa dos usuários de ouvir algum tipo de métrica, o uso de uma métrica que reflete a densidade da embalagem foi provavelmente a única decisão certa e os profissionais de marketing estavam certos, embora isso às vezes leve a situações engraçadas quando os mesmos padrões de design em empresas diferentes são chamados de maneira diferente. Por exemplo, lendo as notícias de que o TSMC já lançou 7 nm e a Intel está atrasando novamente o início da produção de 10 nm, vale lembrar que TSMC de 7 nm e Intel de 10 nm são realmente os mesmos padrões de design em termos de densidade de embalagem e tamanho de transistores individuais.O que vem a seguir? De fato, ninguém sabe. A lei de Moore se esgotou há algum tempo e, se há dez anos, a resposta para a pergunta "o que vem depois?" Como pode ser encontrado nos relatórios dos centros de pesquisa, agora é cada vez mais ouvido que desenvolvimentos promissores precisam ser abandonados, pois se tornam excessivamente difíceis de implementar. Isso já aconteceu com bolachas com um diâmetro de 450 milímetros, esse é parcialmente o caso da litografia EUV (que os cientistas costumavam circular por vinte anos), e isso provavelmente acontecerá com transistores em grafeno e nanotubos de carbono. É necessário outro avanço tecnológico, mas, infelizmente, o caminho para isso ainda não é visível. Chegou ao ponto que o novo diretor do TSMC Mark Liu chamouA direção mais promissora no desenvolvimento da tecnologia microeletrônica não é reduzir o tamanho dos transistores, mas a integração 3D. A integração 3D "verdadeira", em vez de combinar vários chips em um único pacote, será de fato um grande marco no desenvolvimento de microeletrônica, mas a lei de Moore, como a lei de redução do tamanho dos transistores, parece ter morrido completamente.