O Quad Data Rate (QDR-IV) é um padrão de memória de alto desempenho para aplicativos de rede e é ideal para a próxima geração de dispositivos de rede, equipamentos de comunicação e sistemas de computação.

O QDR-IV SRAM possui uma unidade integrada de detecção e correção de erros (ECC) para garantir a integridade dos dados. Esta unidade é capaz de processar todos os erros de memória de bit único, incluindo os causados por raios cósmicos e partículas alfa. Como resultado, os módulos de memória terão uma taxa de erro de programa (SER) de no máximo 0,01 falhas / MB. O QDR-IV está equipado com uma função de paridade de endereço programável que garante a integridade dos dados no barramento de endereço.

Recursos distintos da memória QDR SRAM:

- O módulo de correção de erros integrado garante a integridade dos dados e elimina erros de software

- Os módulos estão disponíveis em duas versões: QDR-IV HP (taxa de dados de 1334 Mtrans / s) e QDR-IV XP (taxa de dados de 2132 Mtrans / s)

- Duas portas de dados de memória DDR1 bidirecional independentes

- Função de inversão de barramento para reduzir o ruído ao conectar as linhas de entrada e saída

- Esquema de Negociação Integrado (ODT) reduz a complexidade da placa

- Inclinar o treinamento para melhorar o tempo de captura do sinal

- Intensidade do sinal de E / S: 1.2V a 1.25V (Lógica do transceptor de alta velocidade (HSTL) / Lógica terminada (SSTL)), 1.1V a 1.2V (POD2)

- Pacote FCBGA3 de 361 pinos

- Largura do barramento: x18, x36 bit

1. Introdução

O Assistente DDRx é uma ferramenta fácil de usar no HyperLynx que permite controlar em lote formas de onda temporais e analisar a integridade do sinal dos protocolos DDR JEDEC padrão. O DDRx Wizard pode ser iniciado tanto na fase de análise pré-topológica de acordo com o cenário "what if", quanto em uma placa totalmente rastreada. Além disso, a ferramenta permite importar a maioria dos formatos de modelo criados pelos principais fornecedores de chips.

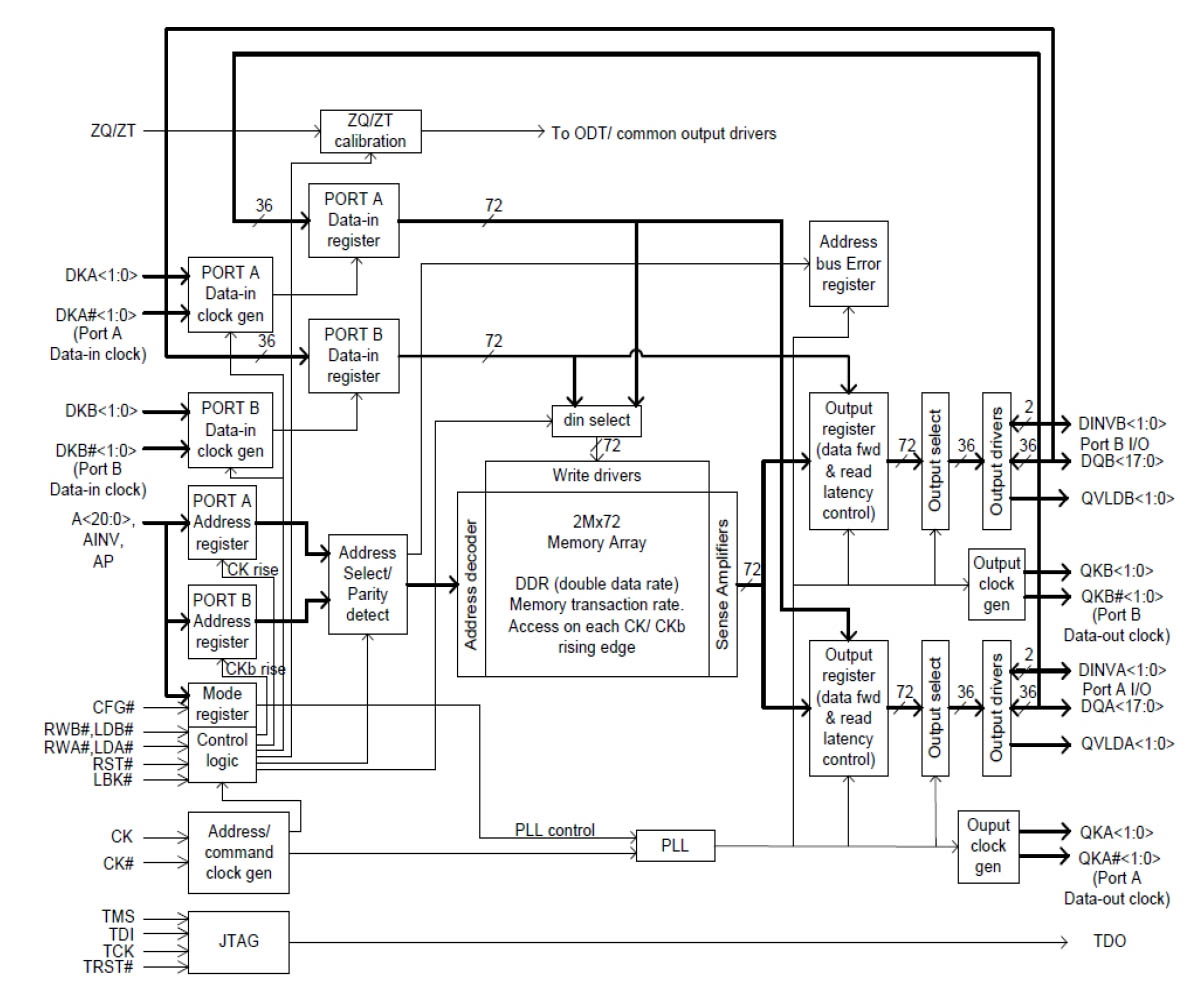

O Assistente de DDRx permite verificar todos os bits do barramento de memória quanto à conformidade com a integridade do sinal, bem como com os requisitos de sincronização entre sinais. Este artigo detalha o uso do assistente interativo para analisar projetos implementando o protocolo QDR4 (Fig. 1).

Fig. 1. A arquitetura interna do QDR no exemplo do módulo CY7C4142KV13 (clicável)

Fig. 1. A arquitetura interna do QDR no exemplo do módulo CY7C4142KV13 (clicável)Primeiro, veja QDR-IV no HyperLynx DDRx WIZARD

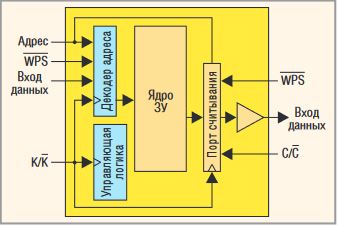

O protocolo QDR-IV define dois pares unidirecionais de um sinal estroboscópico de dados: um para leitura de dados e outro para gravação, que suportam operações independentes uma da outra e operações simultâneas de leitura e gravação, e as portas podem operar em diferentes frequências (Fig. 2). Assim, o risco de um mau funcionamento é completamente eliminado.

Fig. 2. Disponibilidade de portas de leitura e gravação separadas na arquitetura QDR SRAM

Fig. 2. Disponibilidade de portas de leitura e gravação separadas na arquitetura QDR SRAMPara este protocolo, o Assistente DDRx utilizará portas separadas para leitura e gravação de dados. O QDR IV geralmente é implementado usando um barramento x36 ou x18 bits (consulte as Fig. 3a e 3b).

O Assistente DDRx permite a simulação QDR-IV em três etapas:

- Verificação de leitura de dados

- Verificação de registro de dados

- Verificação de barramento de endereço / controle

Como as verificações de barramento de endereço / controle podem ser executadas independentemente das verificações de leitura / gravação de dados, você pode economizar tempo combinando esta etapa com qualquer uma das etapas de teste de dados. A seguir, são descritos todos os três cenários para esses testes.

Características tecnológicas

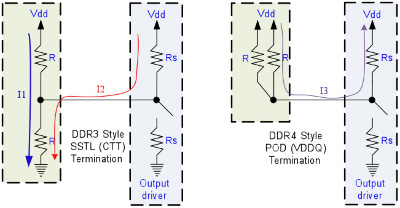

O QDR-IV suporta a tecnologia de pseudo aberto dreno (POD) e a lógica de terminação Stub Series Terminated Logic (SSTL) (Figura 4).

Fig. 4. Diferenças entre POD e SSTL

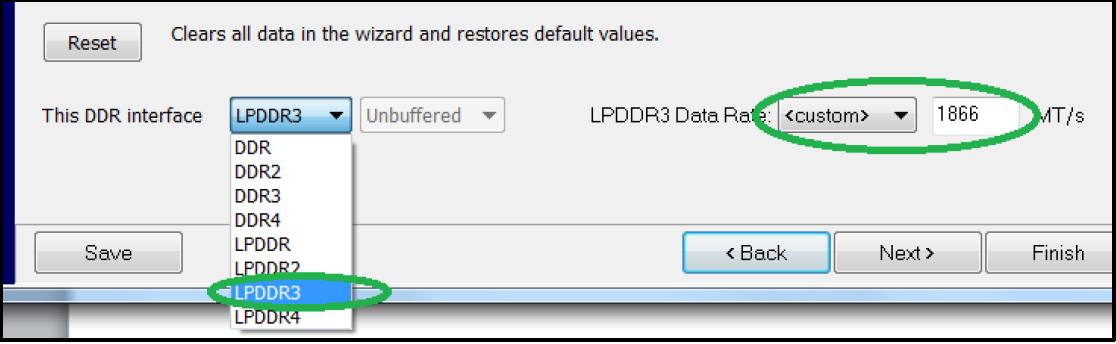

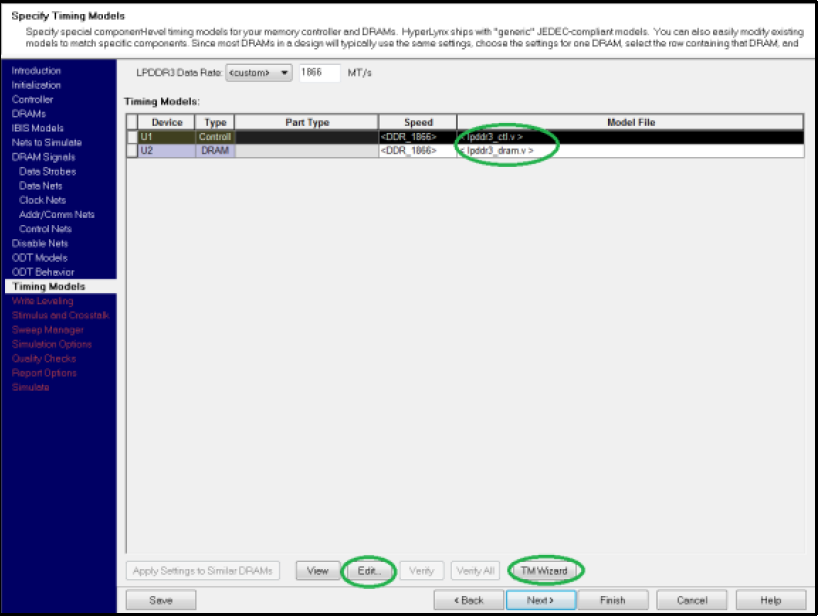

Fig. 4. Diferenças entre POD e SSTLIndependentemente do padrão lógico usado, selecione

LPDDR3 como a tecnologia (Fig. 5), pois não há suporte para o

treinamento Vref , como é o caso do módulo POD do DDR4. Em vez disso, são usados os valores fixos Vref e Vinh / Vinl, semelhantes aos DDR3 e LPDDR3. Como o QDR-IV usa uma taxa de dados dupla para sinais de endereço como LPDDR3, é recomendável que você selecione essa opção. Em seguida, insira a taxa de transferência de dados do usuário, por exemplo, 1866 MT / s ou 2133 MT / s, em que MT / s é o número de megatransfers por segundo (megatransfers por segundo).

Fig. 5. A escolha da lógica padrão

Fig. 5. A escolha da lógica padrãoSinal de dados: operação de leitura

Para operações de leitura do sinal de dados, a DRAM controlará os sinais DQ em conjunto com os sinais QK do estroboscópio diferencial. Assim, a configuração se concentra na operação de leitura de dados e atribui os circuitos (sinais) necessários à porta QK correspondente.

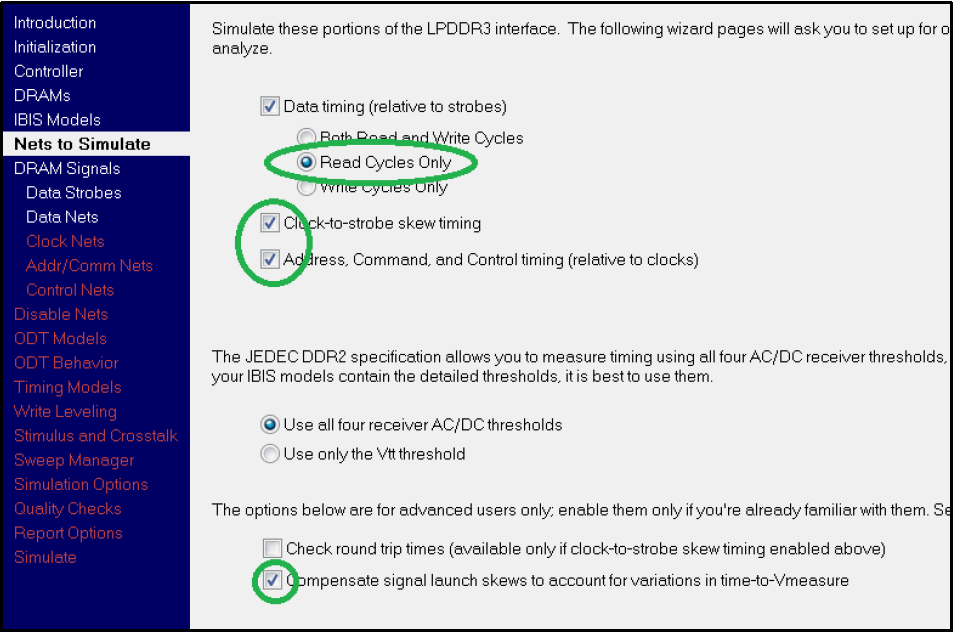

Na seção

Redes para simular (Figura 6), marque a caixa “

Somente ciclos de leitura ”. As

caixas de seleção Clock-to-strobe e Address são opcionais.

Além disso, verifique a instalação das

inclinações de ativação do

sinal Compensar para levar em conta variações na caixa de seleção Tempo até a medição .

Fig. 6. Lendo dados

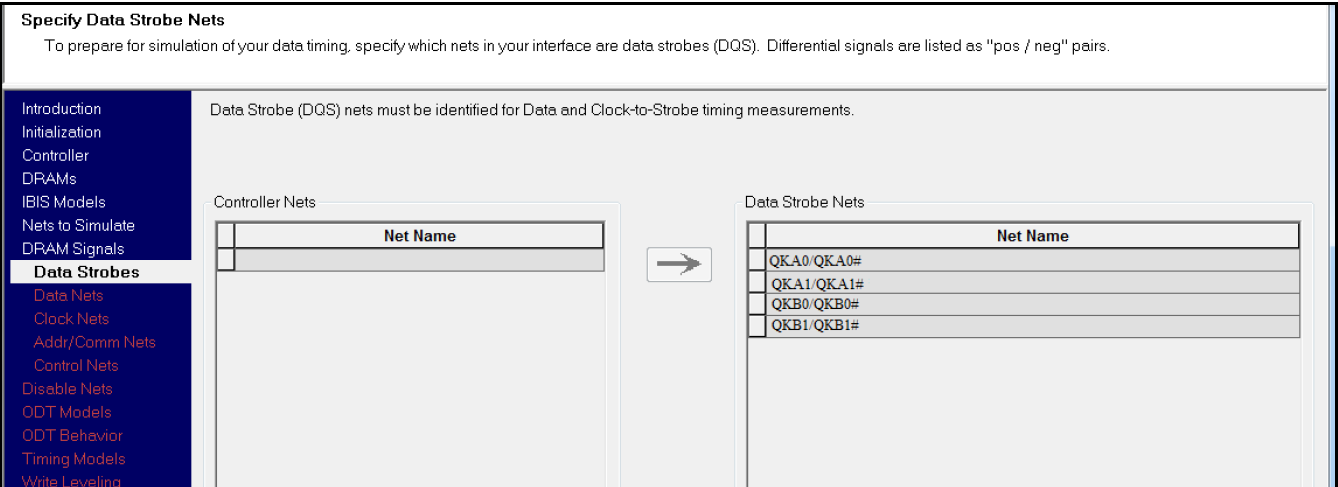

Fig. 6. Lendo dadosVerifique se todos os estroboscópios de dados necessários estão selecionados (Figura 7).

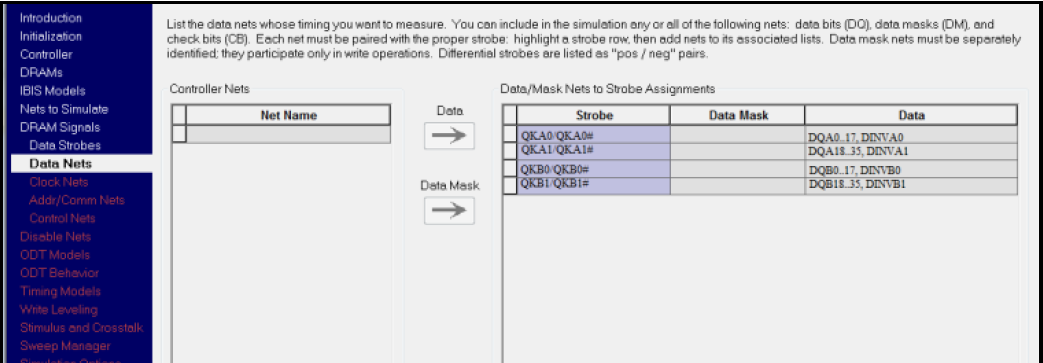

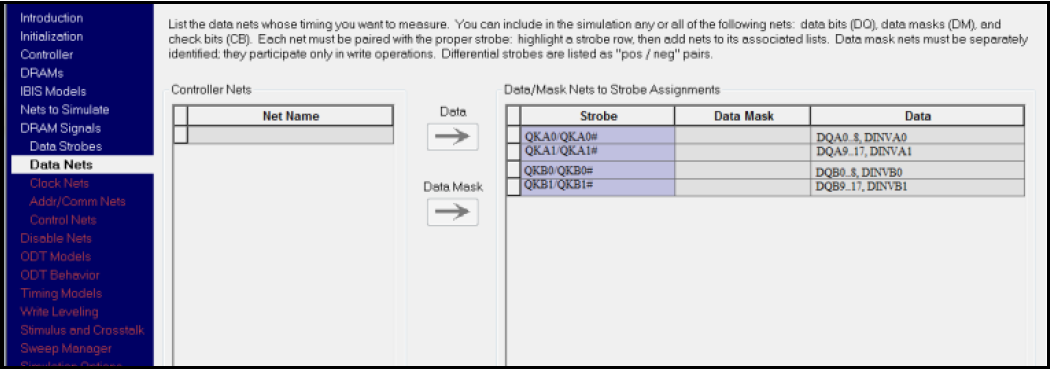

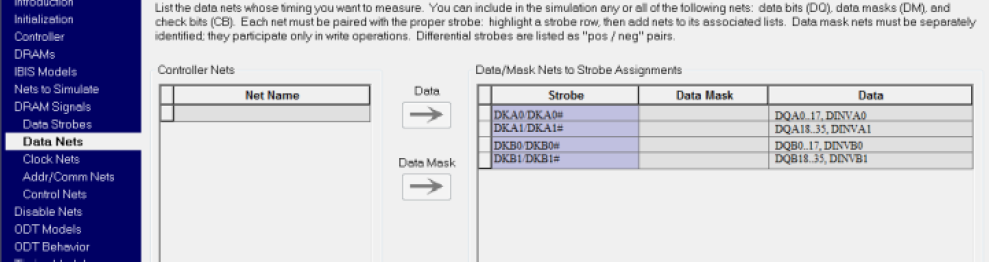

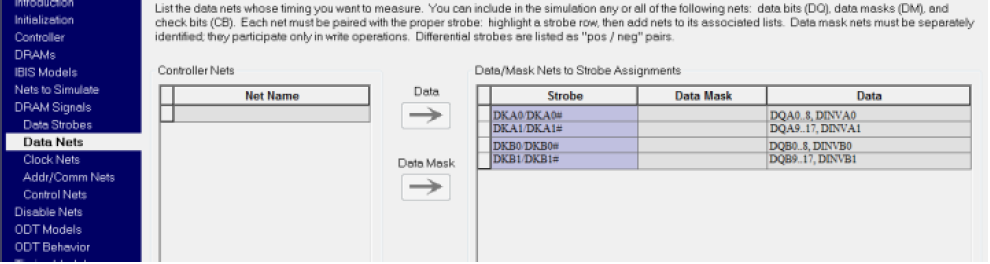

Na seção

Redes de dados , verifique se cada sinal corresponde a cada porta corretamente. Observe que os sinais são diferentes para os barramentos x18 e x36 bits, portanto, verifique se a pinagem é adequada ao seu caso em particular (Fig. 8a e 8b).

Fig. 7. Leitura de strobe de dados

Fig. 7. Leitura de strobe de dados Fig. 8a Grupo de sinais para barramento de 36 bits

Fig. 8a Grupo de sinais para barramento de 36 bits Fig. 8b. Grupo de sinais para o barramento de 18 bits

Fig. 8b. Grupo de sinais para o barramento de 18 bitsO teste do barramento paralelo geralmente é feito ajustando / mantendo o tempo entre o estroboscópio e o sinal. Todos esses requisitos, além de outros valores temporários, são exigidos pelo Assistente DDRx para verificar os resultados. Esses valores podem diferir de microchip para microchip; portanto, é recomendável inserir valores que se apliquem a um dispositivo de memória específico. Além disso, as informações de tempo padrão para LPDDR3 não são compatíveis com QDR-IV. Portanto, todas as informações de tempo do QDR-IV devem ser inseridas e corresponder à documentação do seu chip.

Isso pode ser feito usando o

Assistente de Timing (Fig. 9), que solicita ao usuário que preencha vários formulários para a geração subsequente de valores temporários ou você pode editar os arquivos de sincronização .V que correspondem ao seu controlador e DRAM.

Fig. 9. Definir valores de temporizaçãoObserve

Fig. 9. Definir valores de temporizaçãoObserve : como a simulação é realizada no modo

LPDDR3 , os resultados devem ser interpretados de acordo.

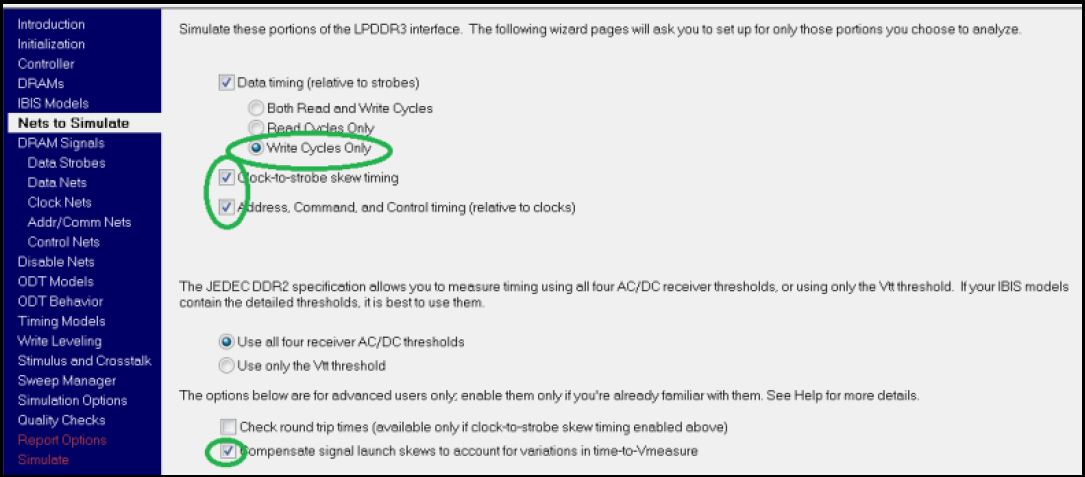

Sinal de dados: operação de gravação

A operação de gravação de dados e sua análise são semelhantes às da operação de leitura descrita acima. Mas há duas diferenças principais que consideraremos agora. Com exceção dessas duas nuances, as etapas adotadas para a operação de leitura de dados podem ser repetidas para simular a gravação de dados.

Na seção

Redes para simular (Figura 10), verifique se a opção

Write Cycles Only está selecionada.

Também é possível simular

operações de gravação de sinal de endereço . E não se esqueça de

verificar se a caixa de seleção Compensar inclinação inclusa para contabilizar variações no tempo até a medição está marcada .

Fig. 10. Gravação de Dados

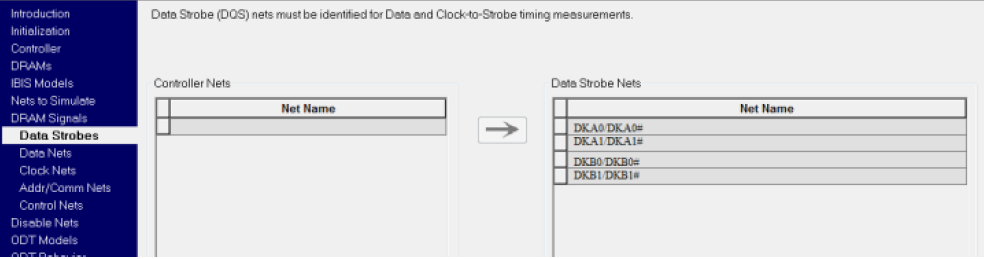

Fig. 10. Gravação de DadosVerifique se as portas corretas estão selecionadas na seção

Strobe de dados (Figura 11). A principal diferença entre uma transação de leitura e uma transação de gravação é o estroboscópio usado para sincronizar os dados; esse estroboscópio é diferente do estroboscópio usado para a operação de leitura de dados (Fig. 12 e 13).

Fig. 11. Portões dos dados registrados

Fig. 11. Portões dos dados registrados Fig. 12. Grupos de sinais estroboscópicos de sinais (barramento de 36 bits)

Fig. 12. Grupos de sinais estroboscópicos de sinais (barramento de 36 bits) Fig. 13. Grupos de sinais estroboscópicos de sinais (barramento de 18 bits)

Fig. 13. Grupos de sinais estroboscópicos de sinais (barramento de 18 bits)Endereço, comando e controle do barramento

O QDR-IV usa bloqueios diferenciais CK / CK # para selecionar sinais de controle, endereço e sinais de comando. A borda principal do sinal CK é usada para inserir informações sobre a porta A e a borda posterior é usada para selecionar informações sobre a porta B.

Levando em consideração a integridade do sinal, as formas de onda para as linhas de endereço devem atender aos requisitos de instalação e atrasos das bordas inicial e posterior do sinal do relógio. Isso é muito semelhante ao comportamento do LPDDR3.

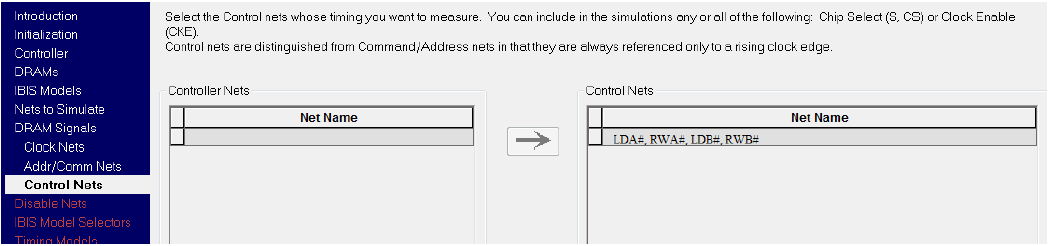

Os sinais

LDA #, LDB #, RWA # e RWB # são sincronizados na mesma taxa de dados (taxa de dados única). Isso significa que esses sinais são sincronizados apenas em uma das duas frentes dos pulsos do relógio. Os sinais LDA # e RWA # são sincronizados na borda ascendente do relógio e os sinais LDB # e RWB # estão na borda descendente.

Os blocos são em grande parte simétricos - o diferencial dianteiro dianteiro não é muito diferente do traseiro. Isso significa que, para garantir a integridade do sinal, os valores de tempo para o

LDB # e o RWB # devem ser quase os mesmos, se não idênticos, ao amostrar nas

bordas ascendentes ou

descendentes do relógio. Os sinais de controle LPDDR3 também são sincronizados apenas na borda ascendente.

As etapas a seguir são específicas para simulação de barramento de endereços, comando e barramento de controle usando QDR-IV.

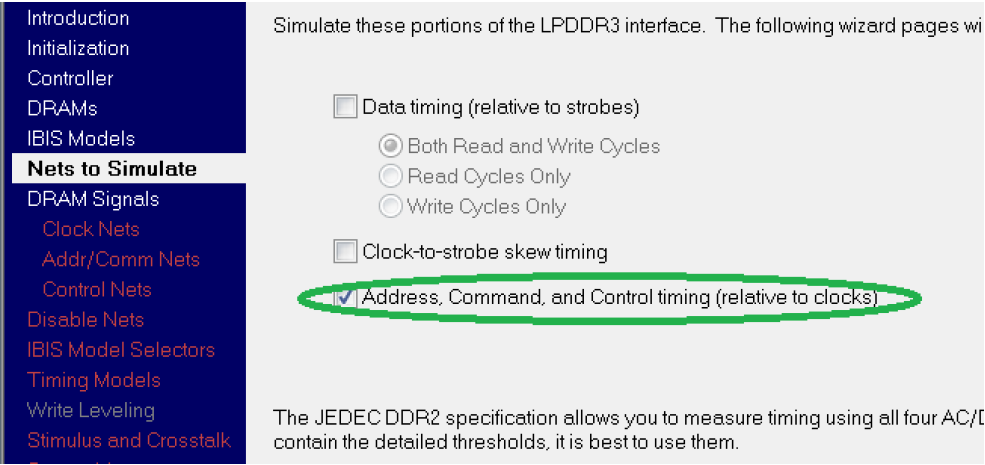

Certifique-se de que, na seção

Redes para simular , a caixa de seleção

Endereço, comando e tempo de controle (em relação aos relógios) esteja

marcada (Fig. 14).

Fig. 14. Marque a caixa Endereço, comando e tempo de controle

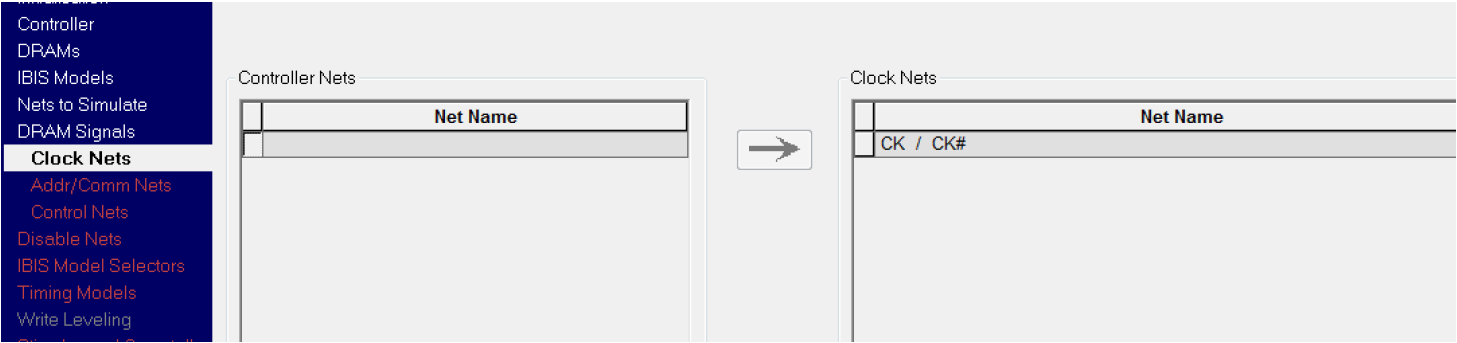

Fig. 14. Marque a caixa Endereço, comando e tempo de controleNa seção

Redes do

relógio , verifique se o par diferencial de sinais de relógio CK / CK # está selecionado (Fig. 15).

Fig. 15. A escolha do relógio diferencial

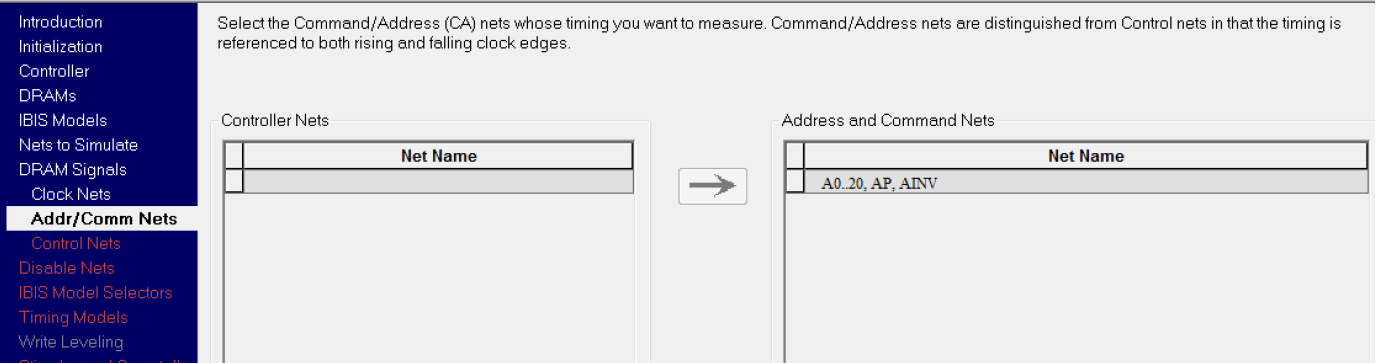

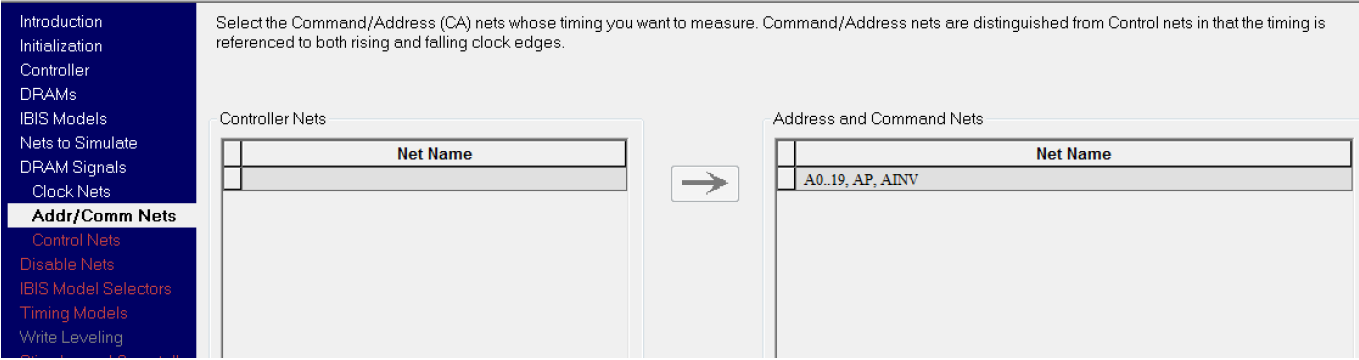

Fig. 15. A escolha do relógio diferencialNa seção

Addr / Comm Nets , verifique se os bits

A [20: 0] estão selecionados para dispositivos com x36 bits e os bits

A [19: 0] estão selecionados para dispositivos com x18 bits. Além disso, defina os

sinais AP e AINV (Fig. 16 e 17).

Fig. 16. Configurações para barramentos de x36 bits

Fig. 16. Configurações para barramentos de x36 bits Fig. 17. Configurações para barramentos de x18 bits

Fig. 17. Configurações para barramentos de x18 bitsNa seção

Redes de controle , selecione os sinais LDA #, LDB #, RWA # e RWB # (Figura 18).

Fig. 18. sinais de controle

Fig. 18. sinais de controleAssim como na modelagem de um sinal de dados, verifique se você está usando os arquivos corretos com parâmetros de tempo. O restante da modelagem e avaliação dos resultados é semelhante ao LPDDR3.

“Interpretando os resultados do relatório HyperLynx DDRx”Conclusão

Seguindo as instruções simples deste artigo, você pode se beneficiar e usar o pacote auxiliar do DDRx Wizard para simular e testar os barramentos QDR-IV.

Espero que este manual seja útil para alguém.

Atenciosamente, Filipov Bogdan (

pbo ).

Aproveitando também esta oportunidade, desejo convidar os desenvolvedores da REU para um seminário organizado pela Nanosoft e Mentor Graphics:

“Uma nova geração de soluções de design de dispositivos eletrônicos da Mentor Graphics”