Saudações, Habr! Meu nome é Daniil Smirnov, estou estudando na escola de graduação da ITMO University, onde nossa equipe está envolvida em eletrônica programável para projetos relacionados a sensores de fibra óptica no laboratório de programação e modelagem. Como base de hardware para sensores, FPGAs são usados - Matriz de portas programável em campo. Há alguns anos, aprendemos que os fabricantes de FPGA estão realizando competições entre estudantes de desenvolvimento. Desde então, todos os anos, uma equipe é formada por nós para participar deste evento e, como este ano se tornou especial, decidimos compartilhar como tudo era por dentro.

Entrada

Em outubro de 2017, fiz uma verificação de rotina semanal: uma análise das conferências em andamento sobre os tópicos que estão sendo implementados em nosso departamento. A certa altura, recebo um boletim da Terasic: uma

nova competição está começando

no desenvolvimento de projetos usando placas de depuração no FPGA , agora em todo o mundo. A experiência da mesma competição do ano passado passa pela minha cabeça e me lembro: adiando até as últimas duas semanas do mês, longa depuração e ajuste de algoritmos e emitindo todos os canais para o monitor e uma promessa de não adiar até o último dia.

Foi uma experiência interessante, durante a qual aprendemos muito sobre uma plataforma como o SoC FPGA - a interconexão de uma enorme variedade de elementos lógicos e o processador Cortex-A9, bem como a interação entre si e com os periféricos na placa de depuração.

Nova competição - novas regras, novos requisitos, um novo nível. Agora, a competição é realizada em várias etapas: primeiro, as etapas regionais, e depois a final em San Jose; o quadro é enviado a todos os participantes da mesma forma,

DE10-Nano , e agora você pode escolher não apenas os três módulos básicos, mas também uma versão grande dos quadros da Analog Devices! Porém, diferentemente das competições dos anos anteriores, desta vez é necessário assinar uma garantia do projeto e, em caso de não cumprimento, os participantes devem enviar as taxas de volta. É bastante justo, levando em consideração as estatísticas dos últimos anos:

<...> 71 equipes de 20 países europeus inscreveram o concurso <...> 25 juízes da Indústria (ALTERA) e Academia (CNFM) na França revisaram os 32 projetos [1].

O orientador científico, como os alunos que queriam se envolver neste trabalho, já estava sob uma carga pesada em vários projetos, mas a emoção durante a competição e a motivação para aprender muitas coisas novas se tornaram argumentos importantes para participar da competição novamente. Restava criar um projeto com o qual você pudesse se inscrever.

Idéia para um projeto

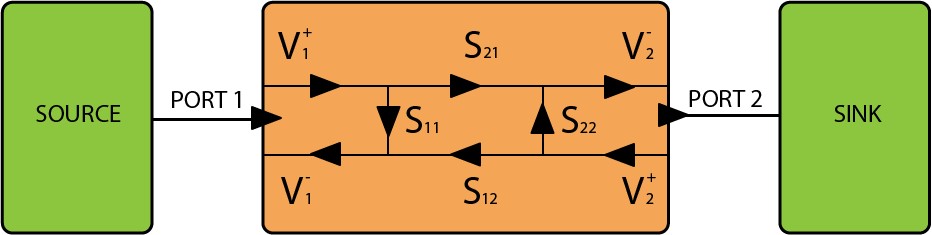

Para que o projeto não se destacasse, foi decidido implementar um dispositivo útil para o departamento, que posteriormente poderia ser facilmente desenvolvido e aprimorado. Com base nas áreas de atividade do departamento, havia várias opções: um refletômetro óptico, um osciloscópio estroboscópico, etc. Observando rapidamente as aplicações existentes e as placas adicionais disponíveis, foi revelado que o refletômetro já havia sido anunciado, mas um osciloscópio estroboscópico não pôde ser montado nesses elementos. A única idéia que permanece viva é o analisador de rede vetorial. No outro dia, duas bobinas foram trazidas para o laboratório, para as quais não havia documentação. A tarefa era determinar pelo menos as características aproximadas dessas bobinas. Sabia-se que o circuito oscilatório estava montado neles, então a principal tarefa era descobrir a frequência ressonante. Nessas tarefas, um analisador de rede vetorial (VAC ou VNA - Vector Network Analyzer) pode apenas encontrar o aplicativo. O VNA permite definir uma matriz de dispersão, também conhecida como matriz de parâmetro S. Nesse método, o elemento em estudo é considerado como uma caixa preta, na qual são analisados os sinais incidentes e refletidos das portas deste dispositivo. Portanto, para um sistema de duas portas, a matriz é a seguinte:

Onde V1 + V2 + são ondas eletromagnéticas que chegam às portas;

V1- V2- - ondas eletromagnéticas saindo das portas;

Sij são elementos da matriz de dispersão de caminhos múltiplos. [2]

Esquema de medição dos parâmetros S de um multipolar

Esquema de medição dos parâmetros S de um multipolarFalhamos em examinar os componentes e o circuito usando um raio-X (pelo menos pelo raio-X do metrô); portanto, o seguinte circuito foi montado nos joelhos: as frequências foram definidas alternadamente com um passo através do circulador para a entrada da bobina usando um gerador, a segunda porta do circulador foi conectada à entrada da bobina e a terceira entrada a um osciloscópio que possui em seu software o modo de análise de amplitude-frequência. Tal circuito torna possível medir o parâmetro S11, isto é, reflexão. No final, depois de muita angústia e calibração, consegui remover essa característica - mas a que custo? O departamento esperava há muito tempo a aquisição de um analisador de rede vetorial para tarefas semelhantes (medir a AFC de dispositivos radioeletrônicos), mas essa compra sempre era de algum modo atrasada.

Após a confusão com as bobinas, foi decidido montar seu próprio analisador de circuitos com visualização e ajuste confortável. Não é difícil encontrar empolgação e desejo de aprender algo novo para você e para os alunos e estudantes de pós-graduação que trabalham no departamento, então a equipe foi rapidamente montada por um engenheiro eletrônico, um programador-desenvolvedor de sistemas em um chip, eu e dois mentores.

Mal disse o que fez! Após inúmeras discussões sobre a faixa de frequência, algoritmos de processamento e outros parâmetros do projeto, o aplicativo continha o seguinte:

- O projeto reivindicado é um analisador de circuitos Vector baseado no SoC FPGA em uma placa DE10-Nano;

- Placas adicionais solicitadas: uma placa com um gerador de frequência programável, um misturador de alta frequência e uma placa com um ADC;

- Faixa de frequência operacional: de acordo com os parâmetros apresentados de placas adicionais;

- Possibilidades de rápida expansão do número de portas conectadas;

- A saída do componente de amplitude e fase para a tela;

- Outras funções básicas de entrada / saída para o analisador de rede vetorial.

Para passar para a próxima etapa, era necessário que a página do projeto obtivesse um número suficiente de "curtidas" dos usuários que se registraram no site. No início, tudo correu bem, mas alguns projetos duvidosos começaram a ganhar valores irreais e contrastantes de gostos e visões em comparação com outros projetos. Aconteceu que o site do concurso era muito vulnerável a trapaças.

Depois de algum tempo, os organizadores informaram que o painel de juízes ainda escolheria os finalistas, de modo que os gostos dos usuários, de fato, perderam peso. Em 31 de janeiro, nossa equipe apareceu nas listas daqueles que passaram para a próxima etapa e começamos a pensar em nosso projeto com mais detalhes, antecipando a depuração.

Realidade dura

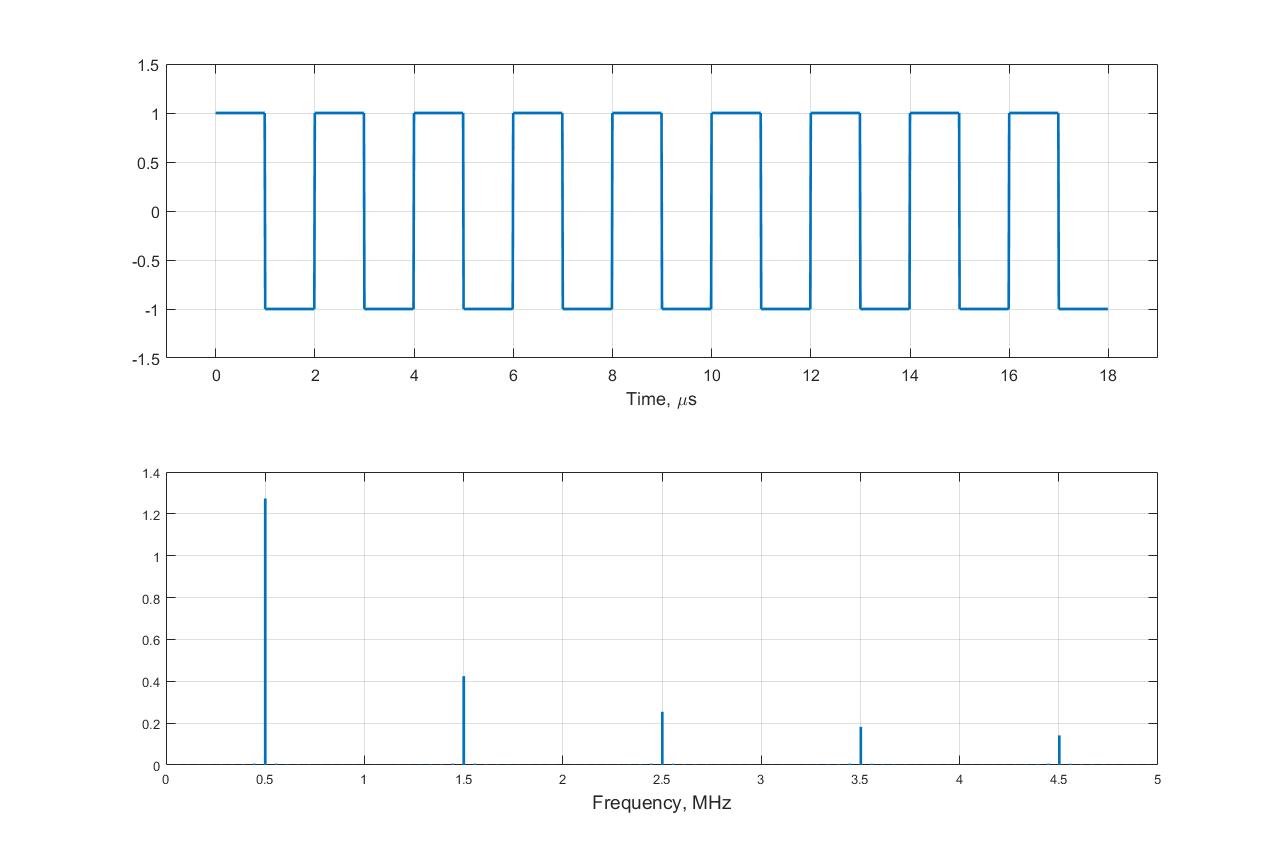

A primeira foi a placa DE10-Nano. Agradável, mas um pouco estranho: eles esperavam que as placas se unissem. Alguns dias depois, é recebida uma ligação da alfândega: as taxas chegaram, todas juntas excedem o limite de preço; portanto, você precisa pagar pelo desembaraço aduaneiro um valor aproximadamente igual ao custo dessas taxas. Tal situação nos incomodou, mas não nos convinha: recusamos os conselhos. Na presença de misturadores e geradores que não possuímos, é necessário encontrar novas soluções. O que fazer? A primeira coisa que veio à mente não foi a solução mais precisa, mas bastante incomum: use a perna GPIO habitual e gere um pouco dela. Um filtro passa-baixo analógico é instalado na saída deste pé com uma faixa de corte um pouco maior que a frequência máxima de meandros. Para iniciantes, foi proposto incluir análises de 1 MHz (por exemplo): depois do filtro, obteríamos um seno mais ou menos puro (os harmônicos mais altos seriam cortados pelo filtro) e assim sucessivamente até que a frequência caísse para aquela em que o sinal após o filtro haverá dois harmônicos. O meandro é a soma dos harmônicos ímpares, e a contribuição proporcional de cada harmônico é conhecida antecipadamente [3].

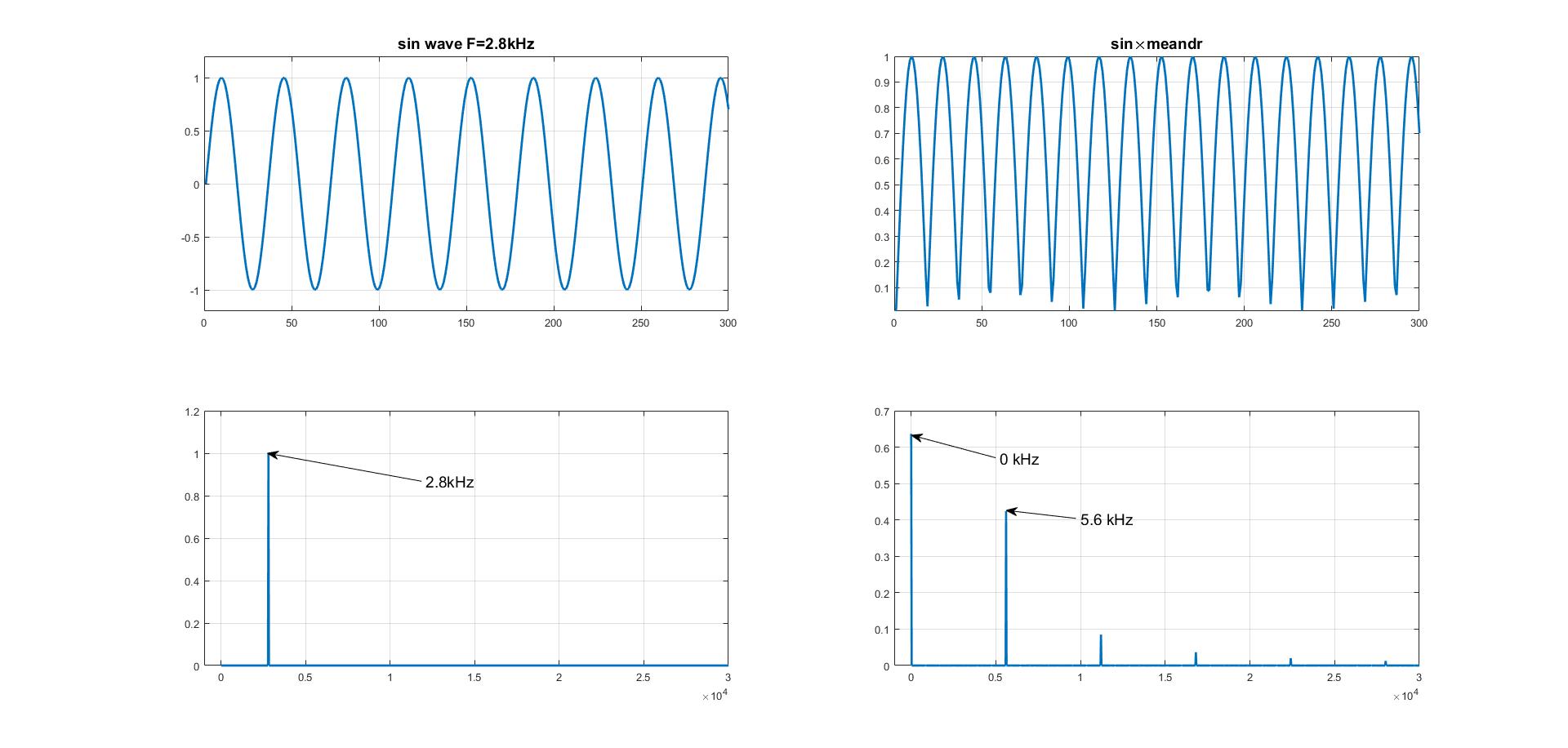

Um exemplo de meandro nos domínios de tempo e frequência: os componentes do sinal harmônico a 500 kHz, 1,5 MHz, etc., são visíveis no espectro.

Um exemplo de meandro nos domínios de tempo e frequência: os componentes do sinal harmônico a 500 kHz, 1,5 MHz, etc., são visíveis no espectro.Com um filtro com uma frequência de corte de 1 MHz, você pode descer para 33. (3) kHz. Após essa frequência, devemos obter a soma de dois senos atrás do filtro. A razão proporcional de suas amplitudes é conhecida (função sinc), a resposta do dispositivo medido a uma frequência de 1 MHz (primeiro harmônico ímpar) também, então precisamos compor uma equação com uma desconhecida e calcular a característica de resposta para uma frequência de 33, (3) kHz! No início, essa solução parecia muito simples; portanto, para iniciantes, era dito a todos na esperança de que alguém encontrasse um erro. Nenhum erro foi encontrado, mas várias limitações foram descobertas à medida que a discussão avançava:

- O pé GPIO não é a melhor fonte de meandros, especialmente com frequência crescente;

- Soldar um filtro compacto nos componentes disponíveis será uma tarefa não trivial;

- Mesmo que essas limitações possam ser contornadas, surge um problema de sincronização para a detecção de fase.

Suponha que resolvemos todos os problemas do lado analógico; programaticamente, outros dois surgem:

- Com a frequência decrescente, o erro de cada detecção e cálculo anteriores contribuirá para a medição subsequente;

- Com a frequência decrescente, o tempo para calcular as características aumentará significativamente.

E finalmente, por último mas não menos importante. O circuito descrito pode ser usado se o elemento medido puder ser descrito por uma função de transferência linear. No entanto, se medirmos uma caixa preta com características não lineares - a ideia terá mais problemas do que benefícios. Não sobrou muito tempo (o primeiro resultado deve ser mostrado dois meses após a chegada da placa); portanto, após alguma deliberação, decidimos verificar

novamente nossos suprimentos em relação às placas de depuração existentes - e encontramos um

DAC de 14 bits a 125 Msps ! Não é a solução mais elegante, mas não há escolha, nós a usamos como um gerador de sinal de saída.

Primeiro conceito

O DAC selecionado como gerador recebe dados na entrada do barramento paralelo e os trava com um sinal de relógio vindo do FPGA. Esse circuito é ideal para sincronização em nosso circuito. No entanto, as perguntas permaneceram com a detecção.

Sim, na mesma placa há um ADC de 14 bits a 65 Msps. Mas apenas as capacidades do gerador são potencialmente mais altas e, de acordo com o teorema de Kotelnikov, esse ADC não funcionará mais nas frequências máximas.

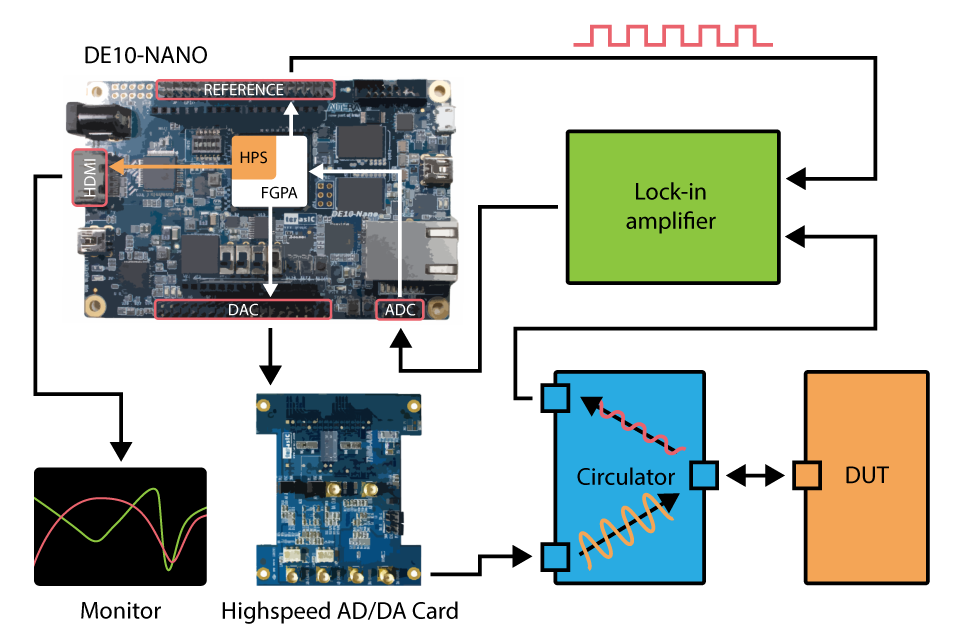

A solução foi encontrada durante uma discussão sobre esse problema com engenheiros eletrônicos experientes. Descobriu-se que, para a nossa tarefa, podemos usar um circuito amplificador de encaixe: a saída desse detector é de dois valores constantes, componentes de fase e quadratura, dos quais você pode obter a amplitude e a fase do sinal e, como são constantes, podem ser detectados mesmo com o ADC lento instalado no DE10-Nano! Foi decidido primeiro modelar o circuito no LTSpice, e somente então selecionar os componentes e montar o circuito, levando em consideração que a entrada do detector é um sinal do circulador e as saídas são conectadas ao ADC na placa DE10-Nano.

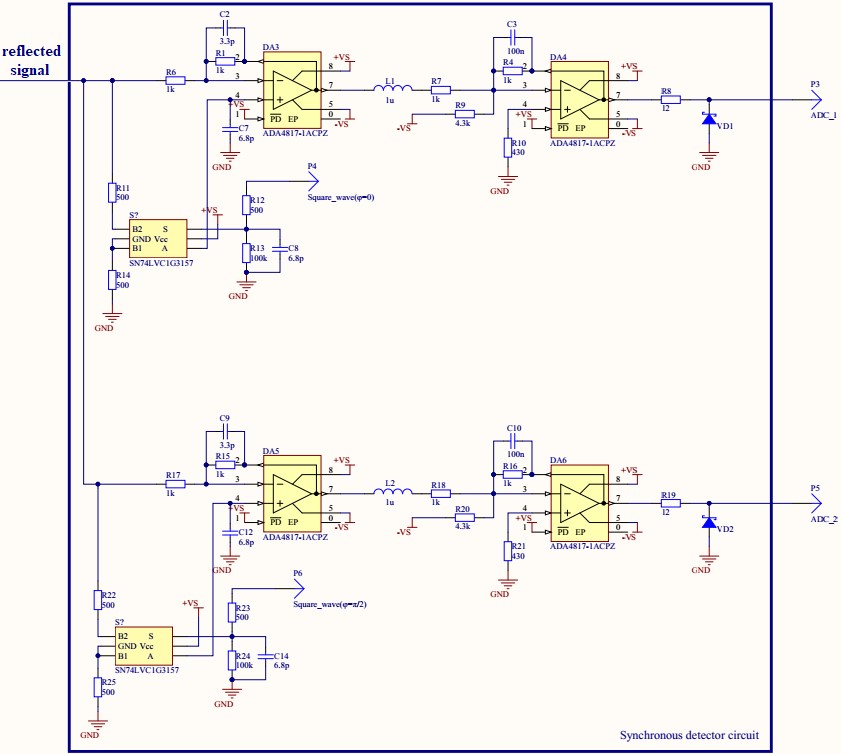

Sobre detector síncrono e circuladorUm detector síncrono também é usado no processamento de sinal digital para detectar vários sinais contra um ruído. A Zurich Instruments tem uma boa descrição [4], no nosso caso a detecção é a seguinte: o sinal refletido de frequência conhecida é multiplicado pelo meandro usando um comutador de alta frequência e um amplificador operacional:

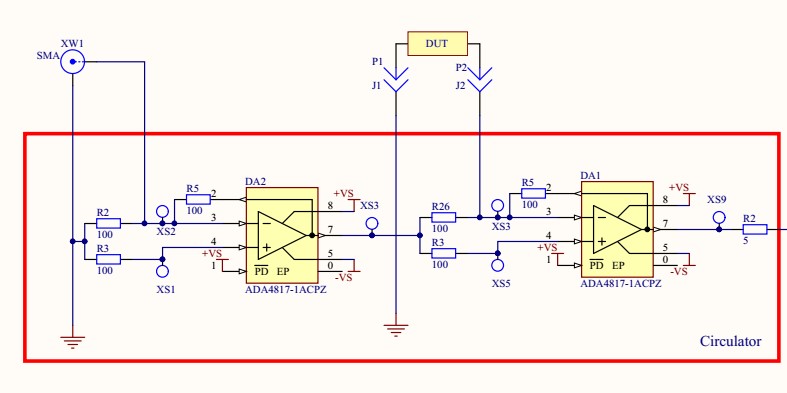

O circuito de detecção de reflexão

O circuito de detecção de reflexãoDe fato, a multiplicação é implementada como comutação do modo de operação do amplificador operacional, e a comutação é controlada por dois meandros provenientes da placa DE10-Nano: um deles está em fase com o sinal original (recebido na entrada do dispositivo) e o outro com um atraso de fase de 90 graus.

O resultado da multiplicação é a transferência do sinal útil para o componente DC, e todas as frequências acima não são mais interessantes e, portanto, podem ser filtradas:

Espectro de sinal antes e depois da multiplicação: na saída do amplificador operacional, você pode montar um filtro passa-baixo simples para isolar apenas o componente DC

Espectro de sinal antes e depois da multiplicação: na saída do amplificador operacional, você pode montar um filtro passa-baixo simples para isolar apenas o componente DCUm circulador em amplificadores operacionais (op amps) é um circuito de conexão em série de amplificadores operacionais fechados em um anel. Os circuladores OA são usados para muitos propósitos, em particular, para sintonizar antenas, amplificadores, geradores, Ethernet de gigabit, etc. na faixa de frequência de até centenas de megahertz. Ao criar o VAC, foi utilizado um circuito circulador criado com base em dois amplificadores operacionais [5].

Diagrama de circuito para conectar o dispositivo medido

Diagrama de circuito para conectar o dispositivo medido  Atualizado conceito de projeto

Atualizado conceito de projetoSinais sinusoidais com uma frequência de 1 Hz a 1 MHz com etapas definidas em alguns Hz foram alimentados na primeira porta do circulador. O dispositivo estudado foi conectado à segunda porta, dependendo da resposta em frequência da qual um coeficiente de reflexão do sinal foi alterado. O sinal refletido foi alimentado na porta 3, onde um circuito detector síncrono foi montado para determinar as características de frequência e fase. Para a operação correta, as portas do circulador foram equiparadas a uma impedância de 100 Ohms, que foi associada à resistência de saída do DAC e à escolha dos dispositivos em estudo.

Menos de um mês foi deixado antes da conclusão do projeto e, no final do prazo, era necessário preparar materiais de relatório: uma descrição detalhada do projeto na página da competição, um projeto publicado no GitHub em domínio público e um relatório em vídeo sobre o trabalho realizado.

Como agora entendemos quais dados seriam inseridos nas entradas e saídas, começamos a trabalhar em um projeto para o SoC FPGA. Vimos o projeto sendo implementado da seguinte forma: o usuário define a faixa de frequência na qual a medição é planejada, o FPGA começa a gerar harmônicos em um intervalo especificado, por sua vez, usando o DAC, o ADC recebe os componentes de quadratura e fase na entrada, convertendo-os para os valores de amplitude e fase na frequência atual , os valores obtidos são exibidos em tempo real no monitor conectado à placa de depuração. Já havia conquistas na exibição de informações no monitor; portanto, a parte principal era a renderização correta dos dados em tempo real e a saída da imagem para HDMI. Estamos desagrupados. O primeiro grupo assumiu tarefas no programa para o processador, para entender com mais detalhes as inicializações necessárias, questões sobre visualização de dados. Também pedimos que aumentassem a resolução da tela para 1024x768 [6]. O segundo grupo deixou detalhes sobre a implementação da peça no FPGA, que deve ser trazida para o processador através do barramento de interface leve_h2f, bem como um teste da operabilidade do primeiro detector síncrono de protótipo. Depois de eliminar as deficiências e medir com sucesso as características de vários elementos, não havia muito tempo, então os dois dias seguintes foram dedicados a conectar os sistemas, adicionar relatórios e editar o vídeo.

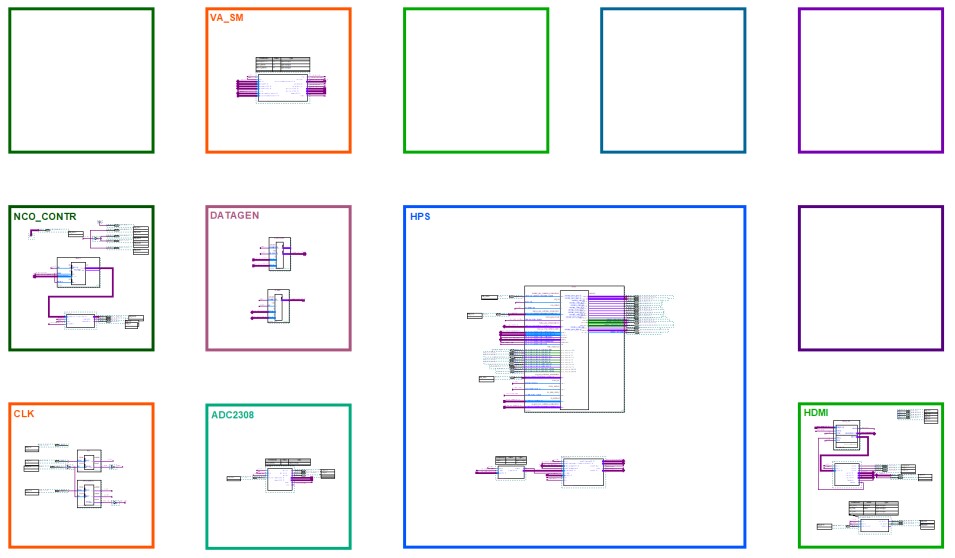

Aparência do arquivo de nível superior no Quartus II

Aparência do arquivo de nível superior no Quartus IIÚltimos minutos

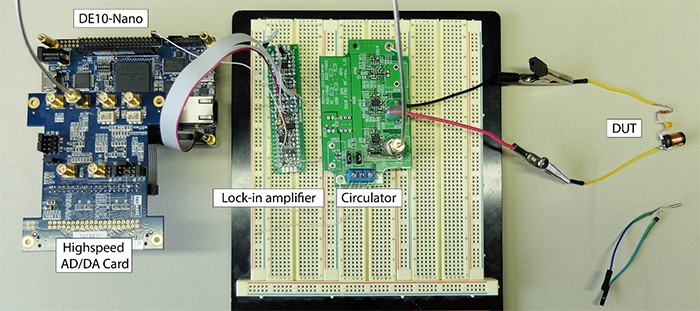

Depois de passar mais de dois dias de folga no laboratório, montamos todo o sistema. Ele não funcionou para toda a faixa de frequência potencial, mediu apenas o parâmetro S11 e refletiu as características de fase e amplitude medidas do dispositivo conectado no monitor. O dispositivo montado externamente ainda não parecia muito atraente - três placas separadas conectadas por fios de núcleo único, mas este é um protótipo

funcional e você pode colocar um marafet na próxima etapa. Escrevemos o texto, ilustramos as etapas de implementação, gravamos um vídeo, todos carregamos no site e começamos a esperar.

Obviamente, enviamos links de alguns amigos para esses materiais para adicionar visualizações ligeiramente. No entanto, em um dia, os pontos de vista começaram a crescer, como se alguém tivesse incorporado isso à promoção. Após uma pequena análise, verificou-se: nosso projeto foi notado no hackaday.io [7] e a grande maioria das visualizações era de lá. Foi interessante ver as primeiras respostas ao nosso projeto. Inspirados, começamos a esperar pelos resultados.

No entanto

Este não é o primeiro ano de nossa participação na competição. Este projeto foi para nós o mais ponderado entre os trabalhos dos alunos implementados anteriormente. Mas não cresceu juntos: não fomos para a próxima etapa. Talvez isso se deva a um mal-entendido entre nós e os juízes. Talvez o projeto simplesmente não entre completamente na área das tendências atuais dos FPGAs (criptografia, computação paralela, redes neurais, etc.). Mas para nós, este é um grande passo no desenvolvimento do SoC FPGA, um novo ramo de desenvolvimento e, mais importante, experiência.

Ps

Parabéns aos representantes russos que ficaram em segundo lugar na final do concurso!

Agradeço aos colegas de projeto Danila Nikiforovsky e

Yevgeny Vostrikov e aos líderes

Ivan Deineku ,

Philipp Shuklin e Artem Aleinik por sua participação e apoio ativos.

Referências

[1] Concurso Innovate Europe 2015

www.innovateeurope.org/eu/2015winner.html[2] Guia do engenheiro para testes automatizados de interface de alta velocidade, Jose Moreira, Hubert Wekmann, 2010, Apêndice F, página 503

[3] Espectro de uma sequência periódica de pulsos retangulares,

en.dsplib.org/content/fourier_series_pimp/fourier_series_pimp.html[4] Princípios de detecção de lock-in e o estado da arte, Zurich Instruments

www.zhinst.com/applications/principles-of-lock-in-detection[5] Circulador / isolador de baixa frequência sem ferrite e ímã

www.cqham.ru/oth9.htm[6] Projeto VAC para a placa DE10-Nano

github.com/tvShushtov/em078_vector_analyzer[7] Artigo sobre o VAC em Hackaday

hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga