A Intel desenvolveu o chip 8087 em 1980, a fim de melhorar o desempenho dos PCs com processadores de linha 8086/8088 (como o IBM PC) ao executar operações de ponto flutuante. Como os primeiros microprocessadores foram projetados para executar operações com números inteiros, a execução de operações com números de ponto flutuante foi lenta, ou seja, sobre o desempenho de operações transcendentais, como funções trigonométricas ou logaritmos. O coprocessador 8087 aumentou significativamente a velocidade de execução de tarefas de ponto flutuante; tudo foi feito quase 100 vezes mais rápido. A arquitetura 8087 também foi implementada nos processadores Intel posteriores, e as instruções 8087 ainda são usadas em PCs x86 modernos. A Intel lançou o chip 8087 em 1980, projetado para melhorar o desempenho da computação de ponto flutuante nos processadores 8086 e 8088.

Como os microprocessadores iniciais trabalhavam apenas com números inteiros, a aritmética de ponto flutuante era lenta e as operações transcendentais, como gatilhos ou logaritmos, pareciam ainda piores. A adição do coprocessador matemático 8087 ao sistema nos permitiu acelerar 100 vezes as operações de ponto flutuante. A arquitetura 8087 tornou-se parte dos processadores Intel posteriores, e as instruções 8087 (embora desatualizadas) ainda fazem parte dos desktops x86 modernos.

O chip 8087 forneceu aritmética rápida de ponto flutuante para o IBM PC original e tornou-se parte da arquitetura x86 usada hoje. Uma das características incomuns do 8087 é uma ROM de vários níveis (memória somente leitura), capaz de armazenar dois bits por transistor, que é o dobro da densidade de uma ROM convencional. Em vez de armazenar dados binários, cada célula na ROM do 8087 salvou um dos quatro valores diferentes, que foram decodificados em dois bits. Como o 8087 precisava de uma grande quantidade de ROM para o microcódigo (1), e o número de transistores no chip era muito limitado, a Intel usou uma tecnologia incomum para resolver o problema. Neste artigo, explicarei como a Intel implementou essa ROM em camadas.

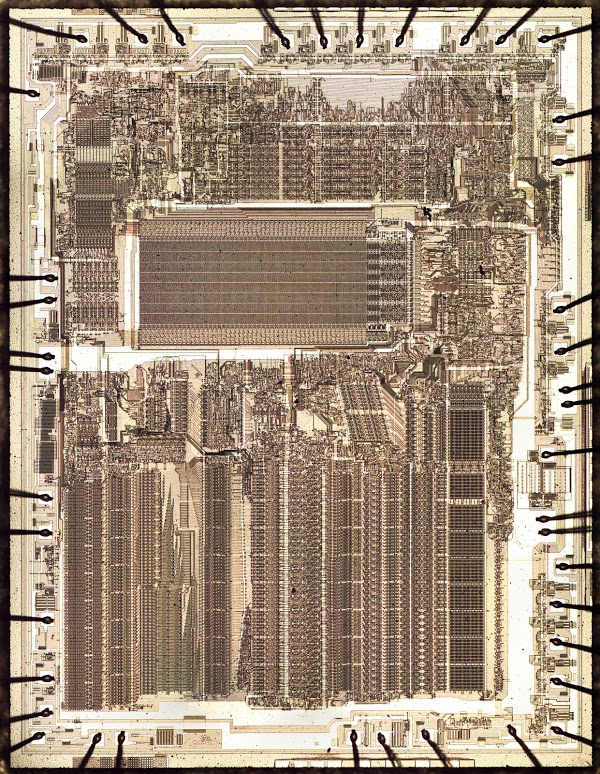

Abri o chip 8087 e fotografei com um microscópio, obtendo a foto abaixo. Na foto, indiquei os principais blocos funcionais com base em minha própria engenharia reversa (Clique para ampliar a imagem). A matriz do processador 8087 é bastante complexa, com 40.000 transistores (2). O 8087 usa números de ponto flutuante de 80 bits: 64 bits são reservados para a mantissa, 15 bits são para o expoente e outro bit assinado. (Exemplo de um número com uma base de 10: entre 6,02 × 1023, 6,02 é a mantissa e 23 é o expoente). Na parte inferior da fotografia, a palavra "processamento de fração" marca parte do circuito da mantissa. Da esquerda para a direita, isso inclui: armazenamento constante, deslocamento de 64 bits, somador / subtractor de 64 bits e pilha de registros. Um pouco mais alto é o esquema para processar o expoente.

Chip de coprocessador matemático para operações de ponto flutuante Intel 8087, com a designação dos principais blocos funcionaisA execução da instrução no 8087 exigiu várias etapas e, em alguns casos, mais de 1000. O firmware 8087 usava o microcódigo para determinar operações de baixo nível em cada etapa: turnos, incremento, amostras de memória, constantes de leitura etc. Você pode perceber o microcódigo como um programa simples, escrito na forma de microcommandos, nos quais cada microcommand gera sinais de controle para vários componentes do chip. A foto acima mostra uma ROM com o programa de microcódigo 8087. A ROM ocupa uma grande parte do chip, mostrando claramente por que uma ROM compacta e multinível era necessária. À esquerda da ROM está o "mecanismo" no qual o programa de microcódigo foi lançado, de fato, um processador simples.

O 8087 funcionou como um coprocessador com o processador 8086. Quando o 8086 detectou uma instrução especial de ponto flutuante, o processador a ignorou e permitiu que o 8087 executasse a instrução em paralelo. Não explicarei em detalhes o funcionamento interno do 8087, mas, em resumo, as operações de ponto flutuante foram implementadas usando operações de adição / subtração e troca de números inteiros. Para adicionar ou subtrair dois números de ponto flutuante, o 8087 executou um deslocamento bit a bit do número até que os delimitadores binários (ou seja, o separador decimal seja uma vírgula, mas no sistema binário) sejam iguais e, em seguida, adicionem ou subtraam a mantissa. A multiplicação, divisão e raiz quadrada foram realizadas por turnos repetidos, adições ou subtrações. As operações transcendentais (tan, arctan, log, power) usavam algoritmos CORDIC, que usam turnos e a adição de constantes especiais, processando um bit de cada vez. O 8087 também encontrou muitos casos especiais: infinito, excedente, NaN (não um número), números desnormalizados e vários modos de arredondamento. O microcódigo armazenado na ROM controlava todas essas operações.

Implementação de ROM

O chip 8087 consiste em uma pequena matriz de silício na qual o silício é dopado com impurezas em alguns locais para obter as propriedades semicondutoras desejadas. O polissilício (um tipo especial de silício) é aplicado à superfície do silício, que forma fios e transistores. E, finalmente, uma camada de metal sobre o silicone completa o circuito elétrico em funcionamento. Na foto abaixo, no lado esquerdo, uma pequena parte do chip é mostrada, como é visível ao microscópio, mostrando uma fiação de metal amarelado. No lado direito da foto, o metal foi removido com ácido, expondo polissilício e silício. Quando o polissilício atravessa o silício, um transistor é formado. As áreas rosadas são de silicone dopado e as finas linhas verticais são de polissilício. Pequenos círculos são os contatos entre as camadas de silício e metal, conectando-os.

Estrutura de ROM no Intel 8087 FPU. A camada de metal é mostrada à esquerda e polissilício e silício à direita.Embora existam muitas maneiras de criar ROMs, a maneira padrão é criar uma grade de "células" onde cada célula armazena um bit. Cada célula pode ter um transistor (o que significa 0 bits) ou não ter um transistor, o que significa 1 bit. Na imagem acima, você pode ver uma grade de células com transistores (onde o polissilício é aplicado ao silício) e transistores ausentes (onde há lacunas no silício). Para ler as informações da ROM, uma linha de seleção de coluna é ativada (com base no endereço) para selecionar os bits armazenados nesta coluna e obter um bit de cada linha na saída. Você pode ver as linhas de seleção de colunas verticais (linhas de seleção de colunas) de polissilício e as linhas horizontais de metal na foto acima. As linhas verticais de silicone dopado são aterradas.

O diagrama abaixo (correspondente ao segmento ROM 4x4) explica como a ROM funciona. Cada célula possui um transistor (preto) ou não possui um transistor (acinzentado). Quando a tensão é aplicada à linha de seleção da coluna de polissilício, os transistores desta coluna ligam e aterram as linhas de metal correspondentes. (neste caso, o transistor NMOS é como uma porta aberta se a entrada for 0 e fechada se a entrada for 1.) As “linhas” metálicas do circuito emitem os dados armazenados na “coluna” selecionada.

Esquema de segmento 4x4 ROMOs sinais de seleção de coluna são gerados por um circuito decodificador. Como esse circuito é construído a partir de válvulas NOR, explicarei primeiro o design das válvulas. O diagrama abaixo mostra uma porta NOR de quatro entradas, composta por quatro transistores e um resistor pull-up (embora, de fato, um transistor especial execute a função do resistor). No lado esquerdo do circuito, todas as entradas são 0, então todos os transistores são desligados e o resistor de pull-up mantém o sinal de saída em um nível "alto". No lado direito, 1 foi aplicado a uma das entradas, ligando o transistor. O transistor está aterrado, então o sinal de saída está agora no nível "baixo". Portanto, se alguma entrada for alta (1), a saída será baixa (0). Portanto, este circuito implementa a válvula NOR.

Porta NOR de 4 vias construída a partir de transistores NMOSO circuito decodificador de seleção de coluna recebe os bits de endereço recebidos e ativa a linha de seleção correspondente. O decodificador contém uma porta NOR de 8 entradas para cada coluna, ou seja, uma porta NOR para cada endereço. A foto mostra dois elementos NOR que geram sinais de seleção de coluna (por simplicidade, mostrarei apenas quatro das 8 entradas). Cada coluna usa uma combinação diferente de linhas de endereço e linhas de endereço preenchidas como entrada, escolhendo um endereço diferente. As linhas de endereço estão em uma camada de metal, que é removida na foto abaixo; as linhas de endereço são destacadas em verde. Para determinar o endereço associado à coluna, observe os pinos quadrados associados a cada transistor e observe quais linhas de endereço estão conectadas. Se todas as linhas de endereço conectadas aos transistores de uma coluna estiverem em um nível baixo (0), a porta NOR selecionará essa coluna.

Parte do decodificador de endereço. O decodificador de endereço seleciona colunas ímpares na ROM, contando da direita para a esquerda. Os números na parte superior mostram o endereço associado a cada saída.A foto abaixo mostra uma pequena parte do decodificador de ROM com todas as 8 entradas para portas NOR. Você pode ler endereços binários examinando cuidadosamente as conexões na barra de endereços. Observe o padrão binário: a1 junta valores alterados em cada coluna, a2 junta-se alternadamente a cada duas colunas, a3 junta-se a cada quatro colunas, etc. A0 é fixo porque esse circuito decodificador seleciona colunas ímpares; um circuito ROM semelhante seleciona endereços pares (tal separação era necessária para o decodificador caber no chip, pois cada coluna do decodificador tem o dobro da largura da célula ROM).

Parte do decodificador de endereço para o microcódigo ROM 8087. O decodificador converte o endereço de 8 bits em sinais de seleção de colunaO último componente da ROM é um conjunto de multiplexadores que reduz 64 linhas de saída para 8 linhas. Cada multiplexador 8 para 1 seleciona uma de suas 8 entradas com base no endereço. O diagrama abaixo mostra um dos multiplexadores de linha de processador 8087, construídos com oito transistores de passagem grandes, cada um dos quais está conectado a uma das linhas de "linha". Todos os transistores estão conectados à saída; portanto, quando o transistor selecionado é ligado, ele transfere sua entrada para a saída. Os transistores multiplexadores são muito, muito maiores que os transistores na ROM para reduzir a distorção do sinal da ROM. Um decodificador (semelhante ao considerado anteriormente, mas menor) gera oito linhas de controle multiplexador a partir de três linhas de endereço.

Um dos multiplexadores de 8 linhas na ROM. Aqui você pode ver camadas de (poli) silício, com compostos metálicos pintados em laranjaPara resumir, a ROM armazena bits em uma grade. Ele usa oito bits de endereço para selecionar uma coluna na grade. Em seguida, três bits do endereço selecionam as oito saídas desejadas nas "linhas".

ROM em camadas

Até agora, expliquei um dispositivo ROM típico que armazena um bit por célula. Então, como o 8087 foi capaz de armazenar dois bits por célula? Se você observar com atenção, o microcódigo ROM 8087 contém quatro tamanhos diferentes de transistores - se você considerar a ausência de um transistor como um dos tamanhos (6). Com quatro opções para cada transistor, uma célula pode codificar dois bits, duplicando aproximadamente a densidade (7). A seção atual explica como os quatro tamanhos de transistores geram quatro correntes diferentes e como os circuitos analógico e digital do chip convertem essas correntes em dois bits.

Uma micrografia do microcódigo ROM 8087 mostra quatro tamanhos diferentes de transistores. Isso permite que a ROM armazene dois bits por célula.O tamanho do transistor controla a corrente através do transistor (8). Um fator geométrico importante são as diferentes larguras de silício (rosa), onde se cruzam com o polissilício (linhas verticais), criando transistores com diferentes larguras de portas. Como a largura do portão controla a corrente através do transistor, os quatro tamanhos do transistor geram quatro correntes diferentes: o maior transistor passa a maior parte da corrente e nenhuma corrente flui se não houver transistor.

A corrente da ROM é convertida em bits em algumas etapas. Primeiro, um resistor pull-up converte corrente em tensão. Em seguida, três comparadores comparam a tensão com a tensão de referência para gerar sinais digitais, determinando qual tensão é maior / menor. Finalmente, as portas lógicas convertem os sinais de saída do comparador em dois bits de saída. Esse padrão é repetido oito vezes, gerando um total de 16 bits na saída.

Esquema para ler dois bits de uma célula ROMO diagrama acima executa essas etapas de conversão. Como resultado, um dos transistores ROM é selecionado pela linha de seleção "coluna" e pelo multiplexador (discutido anteriormente) que gera uma das quatro correntes. Então, um resistor pull-up (12) converte a corrente do transistor em tensão, como resultado da qual a tensão depende do tamanho do transistor selecionado. Os comparadores comparam essa voltagem com três voltagens de referência e a saída 1 se a voltagem da ROM for maior que a voltagem de referência. Comparadores e tensões de referência requerem um design cuidadoso, pois as tensões da ROM podem diferir em apenas 200 mV.

As tensões de referência estão no meio entre os valores de tensão esperados da ROM, o que permite algumas flutuações de tensão. A voltagem ROM "baixa" é mais baixa que todas as voltagens de referência, então todos os comparadores emitem 0. A segunda voltagem ROM é maior que Ref 0, portanto o comparador mais baixo gera 1. Na terceira voltagem ROM, os dois comparadores mais baixos produzem 1 e, no máximo, a tensão da ROM na saída dos três comparadores 1. Portanto, os três comparadores produzem quatro padrões de saída diferentes, dependendo da ROM do transistor. Os elementos lógicos convertem a saída do comparador em dois bits de saída (10).

O design do comparador é interessante, pois é uma ponte entre os mundos analógico e digital, produzindo 1 ou 0 se a tensão da ROM for maior ou menor que a tensão de referência. Cada comparador contém um amplificador diferencial que amplifica a diferença entre a tensão ROM e a tensão de referência. A saída do amplificador diferencial aciona uma porta que estabiliza a saída e a converte em um sinal de nível lógico. O amplificador diferencial (abaixo) é um circuito analógico padrão. A fonte atual (símbolo abaixo) fornece corrente contínua. Se um dos transistores tiver uma tensão de entrada mais alta que a outra, a maior parte da corrente passa por esse transistor. A queda de tensão nos resistores fará com que a saída correspondente fique mais baixa e a outra saída fique mais alta.

Um diagrama mostrando a operação de um par diferencial. A maior parte da corrente passa por um transistor com uma tensão de entrada mais alta, resultando em um sinal de saída mais baixo. O símbolo de círculo duplo abaixo é uma fonte de corrente contínua IA foto abaixo mostra um dos comparadores em um chip; camada de metal por cima, transistores por baixo. Vou considerar apenas os pontos principais desse complexo esquema; Veja nota 12 para detalhes. O sinal da ROM e do multiplexador é fornecido à esquerda. Um circuito de tração 12 converte corrente em voltagem. Dois transistores amplificadores diferenciais grandes comparam a tensão ROM com a tensão de referência (entrada de cima). As saídas do amplificador diferencial vão para o circuito do obturador (espalhado na fotografia); a saída do obturador está no canto inferior direito. A fonte de corrente do amplificador diferencial e dos resistores pull-up são feitos de transistores no modo de depleção. Três comparadores de saída são usados em cada circuito de saída, fornecendo um total de 24 comparadores.

Um dos comparadores em 8087. O chip contém 24 comparadores para converter níveis de tensão de uma ROM multinível em dados bináriosCada voltagem de referência é gerada por um transistor de tamanho cuidadosamente selecionado e um circuito de pull-up. O circuito de referência de tensão foi projetado para ficar o mais próximo possível do circuito de sinal da ROM, de modo que quaisquer alterações na fabricação de chips afetem igualmente os dois elementos. A tensão de referência e o sinal ROM usam o mesmo circuito de carga. Além disso, cada circuito de tensão de referência inclui um transistor muito grande, idêntico ao transistor do multiplexador, embora não haja multiplexação no circuito do sinal de referência - apenas para garantir a "correspondência" dos circuitos. Os três circuitos de tensão de referência são idênticos, exceto pelo tamanho do transistor de referência (9).

Um circuito gerando três tensões de referência. Os tamanhos dos transistores de referência estão entre os tamanhos dos transistores ROM. A camada de óxido não foi completamente removida desta parte da matriz, devido à qual redemoinhos de cores apareceram na fotoPara montar o quebra-cabeça inteiro, a foto abaixo mostra a localização dos componentes do microcódigo ROM no chip (12). A parte principal do circuito ROM consiste em transistores que armazenam dados. O circuito decodificador de coluna está localizado acima e abaixo dos dados da ROM. Metade dos decodificadores de seleção de coluna está na parte superior e metade na parte inferior, para um melhor layout. O circuito de saída está à direita. Oito multiplexadores cortam 64 linhas de linhas para oito. Em seguida, oito linhas entram nos comparadores, gerando 16 bits na saída da ROM à direita. O circuito de referência acima dos comparadores gera três tensões de referência. No canto inferior direito, um decodificador de linha pequena controla os multiplexadores.

ROM de firmware da FPU Intel 8087 rotulada com os principais componentesEmbora inicialmente possa parecer que uma ROM multinível seja metade da ROM convencional, o efeito não é tão perceptível devido ao circuito adicional dos comparadores, e pelo fato de os próprios transistores serem um pouco maiores, devido à necessidade de usar vários tamanhos. Apesar disso, uma ROM multinível economizou cerca de 40% do espaço que uma ROM comum ocuparia.

Agora que entendo a estrutura da ROM, posso simplesmente (mas tediosamente) ler o conteúdo da ROM, apenas olhando para o tamanho de cada transistor sob um microscópio. Mas, sem conhecer o conjunto de instruções do microcódigo, o conteúdo da ROM é inútil.

Conclusões

8087 « » . Intel 1981 iAPX 432.11 , 1980- . , - , , , , , , (14).

, , -. - (13). - 4 ( 16 ) , (QLC, quad-level cell). , 1980- , .

, @kenshirriff 8087. RSS-. 8087.

- 8087 1648 ( ), 16 , 26368 . , Intel .

- 8087: Intel , 40 000 , , 45 000. . , , PLA , , «» , . , .

- 8086 8087 ; . , 8087 8086 , 8087. , 8086 , . , 8087 8086 ( 8088), , 8086. , 8086, . 8087 , 8086. , 8086 8087, , . , 8087 , , . 8087 , , . 8087 8087, .

- , , , , , . , ROM, , . , 8 1/8 , 1/8 . , , (, 1 × 16) , . , «» . , Intel ; 1405 512 . , «» - 20 .

- IBM : ( , ), (link). , Xerox Alto, . , . , .

- , Hacker News , 8087 . , , .

- 1980- . Mostek : . , . Intel, ( ), . ( ) . ( ), , . Z-80 «», , , , . , , Z-80 , , , .

- . ( — .) ( , ) , . MOSFET . Wikipedia

- , -. , . , Reference 0 , . , , . : , , , . - , , , .

- : = 00, = 01, = 11, = 10. ; , , . (. «Two Bits Per Cell ROM», Stark).

- Intel iAPX 43203 (1981) , 8087. «The interface processor for the Intel VLSI 432 32 bit computer,» J. Bayliss et al., IEEE J. Solid-State Circuits, vol. SC-16, . 522-530, 1981 . 43203 - iAPX 432. Intel iAPX 432 1975 , «», Intel 1980- . iAPX 432 , Intel 8086 , 1978 . Intel 8086 , x86, iAPX 432 1986 .

- ( «Multiple-Valued ROM Output Circuits») . . (T3, T4, T5) . 4 5 , 3, ( ). ( ) T6, . ().

- - SLC ( single level cell — ), MLC (multi level cell — ), TLC (triple level cell — ) QLC (quad level cell — ). , - , , - .

- «Electronics» «Four-State Cell Doubles ROM Bit Capacity» (. 39, 9 1980 .), Intel, . Intel « » COMPCON (. 209-212, 1981 .). Intel «Multiple-valued ROM output circuits» (Proc. 14th Int. Symp. Multivalue Logic, 1984). , , — « A Survey of Multivalued Memories » («IEEE Transactions on Computers», 1986 ., . 99–106) « A review of multiple-valued memory technology » (IEEE Symposium on Multivalued Logic, 1998).

, . Você gosta dos nossos artigos? Deseja ver materiais mais interessantes? Ajude-nos fazendo um pedido ou recomendando a seus amigos, um

desconto de 30% para os usuários da Habr em um análogo exclusivo de servidores básicos que inventamos para você: Toda a verdade sobre o VPS (KVM) E5-2650 v4 (6 núcleos) 10GB DDR4 240GB SSD 1Gbps de US $ 20 ou como dividir o servidor? (as opções estão disponíveis com RAID1 e RAID10, até 24 núcleos e até 40GB DDR4).

VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps 1 ,

.

Dell R730xd 2 vezes mais barato? Somente nós temos

2 TVs Intel Dodeca-Core Xeon E5-2650v4 128GB DDR4 6x480GB SSD 1Gbps 100 a partir de US $ 249 na Holanda e nos EUA! Leia sobre

Como criar um prédio de infraestrutura. classe usando servidores Dell R730xd E5-2650 v4 custando 9.000 euros por um centavo?