Os FPGAs Stratix 10 SX / GX da Intel

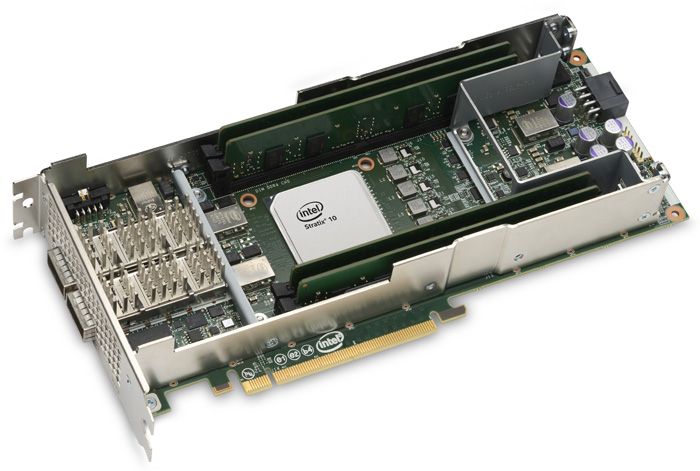

Os FPGAs Stratix 10 SX / GX da Intel , lançados há 2 anos, são uma nova palavra no campo de matrizes de gateways. Executados de acordo com o mínimo na época, a tecnologia de processo de 14 nm, eles eram duas vezes mais produtivos e 70% eficientes em energia do que seus antecessores. No entanto, para obter todos os recursos inerentes ao FPGA Intel, você precisa do mesmo "invólucro" avançado. A construção de hardware e software lançada pela Intel para usar o Stratix em sistemas host é chamada de PAC (Cartão de Aceleração Programável) - sua

próxima versão foi anunciada em setembro deste ano.

O novo PAC é baseado no Intel Stratix 10 SX FPGA - o modelo mais poderoso da família Stratix 10. Lembrarei brevemente de suas principais características:

- Arquitetura HyperFlex

- tecnologia de produção - Tri-Gate de 14 nm (FinFET);

- fábrica monolítica com 5,5 milhões de elementos lógicos;

- até 96 canais transceptores duplex;

- largura de banda de transceptores de até 28,3 Gb / s;

- correção de erros de hardware em cada canal do transceptor;

- controladores de memória de hardware que suportam memória DDR4-2666;

- unidades de processamento de sinal digital (DSP) com capacidade total de até 10 TFLOPS, eficiência energética de até 80 GFLOPS / W;

- processador ARM Cortex-A53 de 64 bits e 4 núcleos embutido com uma frequência de até 1,5 GHz;

- aceleração por hardware de criptografia / descriptografia AES-256, SHA-256/384 e ECDSA-256/384;

- suporte de hardware para autenticação multifator.

Quanto ao próprio cartão de aceleração programável, seu dispositivo funcional é o seguinte.

O mesmo em mais detalhes na forma de uma tabela.

| Fator de forma | PCIe Gen3 x16

Altura total, 3/4 de comprimento, slot duplo |

| A memória | ECC DDR4 de 32 GB (4x8 GB) |

| Interfaces de rede | 2X QSFP + até 100 Gbps |

| Interface de serviço | USB 2.0 para depuração e programação |

| Controlador de controle | Controladora de gerenciamento de rodapé (MAXC) Intel MAX 10 FPGA

• Leitura de dados de temperatura e tensão

• Modelo de dados no nível da plataforma (PLDM)

• IPMI 2.0 |

| Gerenciamento de energia | Soluções Intel Enpirion Power (telemetria e monitoramento de status em tempo real) |

| De software | • Pilha de aceleração para CPU Intel Xeon com FPGA

• Gerenciador de interface FPGA

• Intel Quartus Prime Pro Edition

• Intel FPGA SDK para OpenCL |

A placa estará disponível como parte dos produtos de servidor dos parceiros OEM da Intel (em particular, Hewlett Packard Enterprise) no início do próximo ano.