Projetar dispositivos eletrônicos usando módulos de memória DDR SDRAM rápidos requer atenção especial à integridade do sinal. O artigo fala sobre uma moderna ferramenta de modelagem para resolver esses problemas.Hoje, quase todos os eletrônicos modernos estão equipados com módulos de memória. Servidores, computadores, smartphones, consoles de jogos, navegadores GPS e a maioria dos outros dispositivos são projetados com base em processadores e FPGAs. Esses dispositivos requerem uma memória de alta velocidade com uma largura de banda de canal grande ou memória de memória de frequência dupla (DDR). Com cada nova geração de DDR SDRAM (memória dinâmica síncrona com acesso aleatório e velocidade de transferência de dados duplicada), a velocidade de troca de dados, capacidade e consumo de memória é reduzida.

Ao projetar as placas de circuito impresso de dispositivos com memória DDR, várias dificuldades podem surgir, uma das quais é o problema da integridade do sinal. Este artigo discute os problemas de garantir a integridade dos sinais em dispositivos que usam memória DDR.

Ruído e instabilidade do sinal de dados digitais

Ao receber / transmitir o sinal de clock do barramento de memória do controlador para o microcircuito, várias interferências podem ocorrer devido ao próprio jitter dos transmissores e receptores, perdas nas linhas de transmissão, ruído e interferência. Tudo isso leva ao aparecimento de tremulação e distorção da forma do sinal da interface digital.

Qualquer energia indesejada adicionada a um sinal ideal pode ser considerada ruído. Isso pode ser causado por interferência de linhas vizinhas, canais de transmissão mal projetados, impedância inconsistente e outros fatores que levam ao embaçamento da parte frontal do pulso. Na ausência de ruído, o sinal real é idêntico ao ideal.

Qualquer desvio da forma de onda ideal afeta sua integridade. Desvios de tempo (tremulação) e desvios de amplitude / tensão (ruído) também afetam o desempenho do sistema. Se você não garantir a integridade dos sinais, o sistema DDR utilizará as informações incorretas, o que aumentará significativamente a intensidade dos erros de bits BER (Bit Error Rate). Por fim, o sistema funcionará incorretamente e ineficientemente.

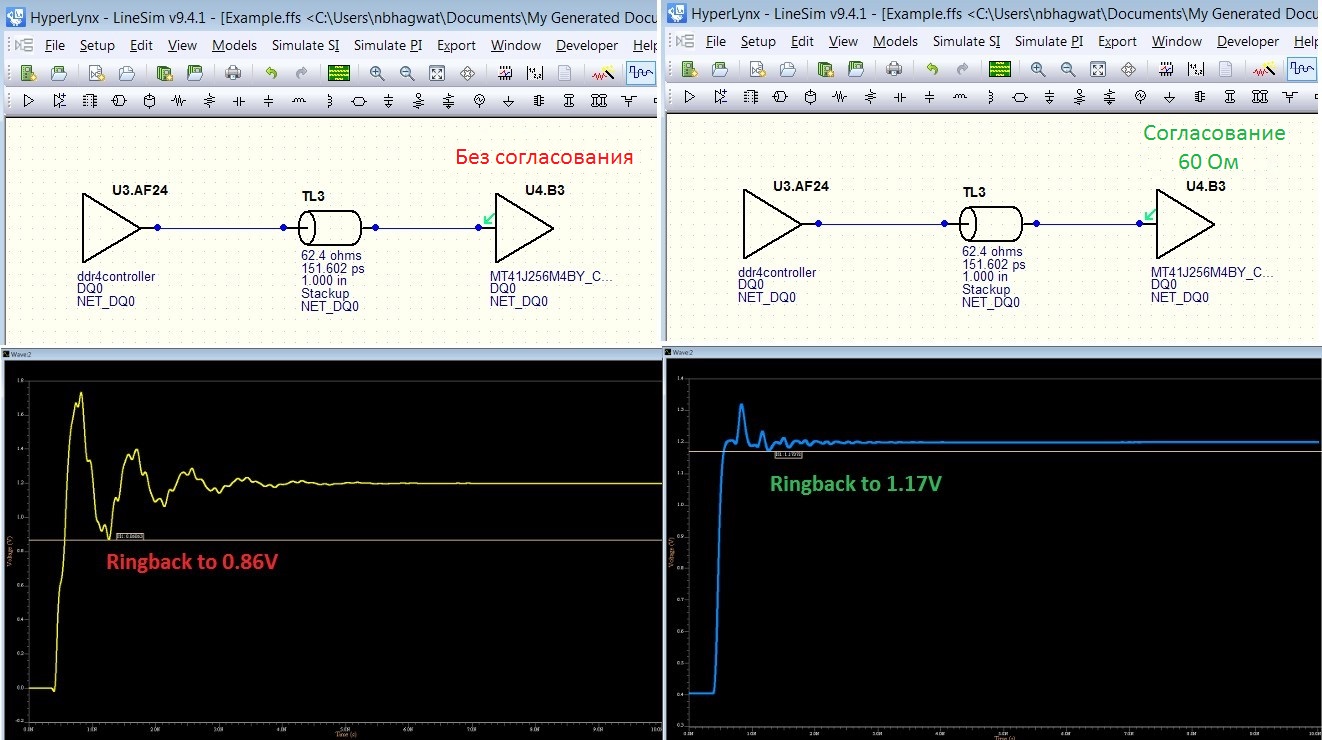

Considere um exemplo específico. Se o engenheiro conectar o transmissor a um receptor inconsistente localizado a alguma distância dele, a forma de onda será semelhante à mostrada na Figura 1a: aqui você pode ver claramente o "toque" em 0,86 V e as emissões espúrias de aumento em 1,75 V com um sinal de 1,2 V. Tudo isso pode levar ao mau funcionamento da lógica DDR4 e, se a placa de circuito for projetada com essa topologia, ocorrerão 100% de probabilidade de erros no fluxo de dados, o que, por sua vez, pode levar à operação incorreta do sistema. .

Teoricamente, é possível resolver problemas com o "toque" e as emissões, reduzindo o comprimento da linha de transmissão, mas, infelizmente, isso raramente funciona na prática. A maneira mais eficaz é combinar o receptor / transmissor por impedância, como resultado do qual o nível de ruído diminui e a forma do sinal se torna muito melhor (consulte a Fig. 1b).

Fig. 1. Uma topologia com problemas na qualidade do sinal: a) antes da coordenação b) após a coordenação

Fig. 1. Uma topologia com problemas na qualidade do sinal: a) antes da coordenação b) após a coordenaçãoNesse sentido, surge a pergunta sobre qual classificação de aprovação usar e como calculá-la, porque mesmo uma pequena alteração na classificação pode afetar significativamente o desempenho do sistema. A única maneira de resolver esse problema é simular, em particular, usando os assistentes de reconciliação interativos usados no HyperLynx.

Problemas de tempo no DDRx

Como os barramentos paralelos operando em frequências gigahertz, como DDR3 / 4, são cada vez mais usados no design de placas de circuito impresso, os problemas de integridade do sinal são especialmente graves. O DDR3 SDRAM, por exemplo, difere significativamente em termos de desempenho de velocidade e frequência do DDR2: a frequência máxima de clock do DDR2 é 800 MHz e a frequência máxima do DDR3 é 1600 MHz. Devido à redução da tensão de alimentação das células, os criadores do novo tipo de RAM conseguiram reduzir o consumo de energia em até 15%, o que, dado o impressionante desempenho da DDR2, pode ser chamado de verdadeiro avanço. O DDR3 usa uma topologia de barramento de comando / endereço / controle “Fly-by” da rede com correspondência intra-módulo (ODT). Ao mesmo tempo, o DDR3 cria novos problemas de integridade do sinal, em particular, associados a circuitos ODT, taxas de transferência de dados mais altas e distorção do tempo.

Apesar de existirem controladores que executam calibração automática de leitura / gravação, otimizando intervalos de tempo, o desenvolvedor precisa garantir o tempo correto. Os limites de tempo nas interfaces DDR3 são tão pequenos que a abordagem empírica da otimização não é mais suficiente e, para garantir a operação da interface em altas velocidades, é necessária uma análise detalhada do circuito.

Tais relações temporais complexas são difíceis de analisar sem a ajuda de ferramentas adicionais. Para identificar e eliminar possíveis problemas em geral ou calcular relacionamentos temporais complexos, os engenheiros devem analisar os relacionamentos de causa-efeito, que é uma tarefa complexa e demorada.

Tais problemas de design geralmente levam a atrasos no planejamento do projeto e, como resultado, aumentam significativamente o tempo necessário para o produto final entrar no mercado. Ferramentas de simulação avançadas e poderosas podem ajudar os engenheiros a encontrar e corrigir erros rapidamente, otimizando os sinais para um nível aceitável de BER.

Análise de integridade de sinal de sistemas DDR SDRAM

O Comitê de Padronização de Engenharia de Semicondutores da JEDEC aprovou uma lista de requisitos que devem ser seguidos ao desenvolver produtos de qualidade. É fundamental que as SDRAMs DDR atendam a esses requisitos para garantir a operação adequada e evitar problemas de integridade do sinal. No entanto, a realização de todas as medições e cálculos necessários é muitas vezes repleta de muitas dificuldades.

Às vezes, esses cálculos podem ser totalmente evitados seguindo estritamente as instruções de layout fornecidas pelo fornecedor do controlador. Mas e se essas recomendações não puderem ser implementadas devido a várias limitações em projetos específicos? O que fazer se demorar muito tempo para garantir que o projeto atenda a todas as recomendações e requisitos? Nessas situações, você precisa usar ferramentas para verificar rapidamente o projeto antes de colocá-lo em produção.

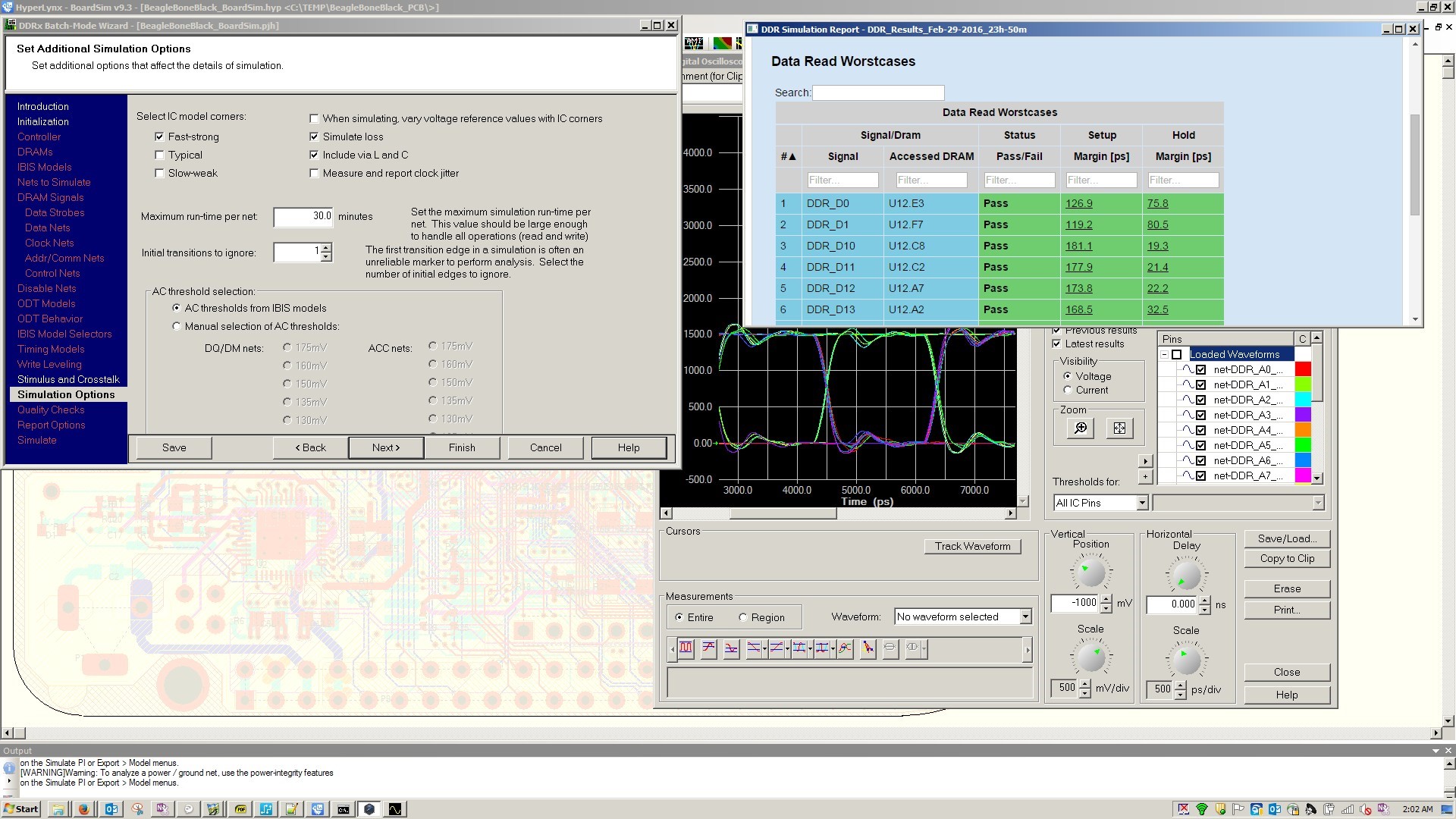

Usando o HyperLynx DDR (veja a Figura 2), você pode simular todo o canal DDR em uma iteração. Para fazer isso, você só precisa vincular os modelos de dispositivos apropriados disponíveis nos sites dos fabricantes. Depois disso, o tempo de configuração da simulação levará apenas dez minutos, o que permitirá modelagem adicional sem demora.

Fig. 2. Modelando com o Auxiliar Interativo HyperLynx DDR

Fig. 2. Modelando com o Auxiliar Interativo HyperLynx DDRO processo de configuração é intuitivamente simples, pois todos os parâmetros necessários para configurar a simulação são solicitados pelo assistente interativamente. O usuário simplesmente digita informações relevantes, como a escolha dos modelos IBIS para controladores e dispositivos de memória, taxas de transferência para ciclos de leitura / gravação, ODT etc. Todas as configurações criadas podem ser salvas para uso futuro, o que reduzirá o tempo de configuração em projetos futuros. As simulações podem ser executadas antes ou depois do rastreamento, ajudando a determinar os requisitos para a pilha de PCB.

Análise dos resultados da simulação

A simulação inclui análise de integridade do sinal e sincronização de todo o barramento DDR. Após a conclusão do processo de simulação, é criado um relatório que inclui dados sobre a aprovação (não aprovação) de verificações, de acordo com as informações de configuração e os dados inseridos no assistente interativo. Os resultados podem ser filtrados e organizados adequadamente para um estudo cuidadoso dos problemas de tempo e integridade do sinal nos ciclos de leitura / gravação de dados, nos barramentos de endereço e comando ou nos circuitos diferenciais. Todos os resultados do relatório estão vinculados aos dados de simulação correspondentes, para acesso rápido à ferramenta de visualização de formas de onda gráficas de sinais.

Os dados da simulação no modo batch, criados pelo assistente DDRx, podem ser salvos no disco, o que permite usar o osciloscópio HyperLynx para simular vários circuitos simultaneamente e estudar em detalhes os problemas de integridade do sinal no modo offline.

Conclusão

DDR SDRAM abre novas possibilidades no desenvolvimento de dispositivos eletrônicos. Como em outras interfaces de alta velocidade, o uso da memória DDR possui vários recursos. O problema da integridade do sinal deve ser cuidadosamente estudado para evitar iterações desnecessárias e caras na fabricação de produtos. A modelagem é uma excelente maneira de resolver esse problema, permitindo que você leve em consideração os efeitos no nível da placa, como alterações na impedância e atrasos no tempo, fornecendo controle abrangente sobre a interface da memória. Poderosas ferramentas de análise ajudarão a garantir que os projetos cumpram as recomendações da JEDEC e a garantir que o produto final funcione com alto desempenho e confiabilidade.

O HyperLynx DDR pode ser compartilhado por muitas empresas de design de PCB CAD, incluindo PADS e Xpedition.

Este artigo foi publicado na revista MODERN ELECTRONICS No. 7, 2018 (www.soel.ru)