Projeto tecnológico

DFM - esses são os princípios de desenvolvimento e gerenciamento de projetos, que visam o sucesso da produção do produto acabado. Seguir esses princípios foi projetado para reduzir o prazo de produção e teste de produtos acabados, além de melhorar a qualidade. O DFM começa muito antes do design, na fase de discussão das especificações técnicas, depende do tamanho da série e afeta o custo de design, fabricação e teste. Sobre o DFM escreveu em Habré, por exemplo

aqui . Hoje falaremos sobre testes funcionais de uma placa de circuito impresso e descreveremos sua preparação para esse fim. (tráfego)

No projeto industrial de placas de circuito impresso, o DFM também possui funções como: DRC (Design Rule Checking) para verificar limitações tecnológicas, CAM (Computer Aided Manufacturing) para preparar a produção da placa de circuito e DFA (Design For Assembly) para otimizar a montagem. Essas funções podem ser integradas ao software CAD (sistemas de automação de design de PCB) ou entregues como software separado. Aqui podemos mencionar o

Vayo , que possui módulos de software para teste de software: DFM Expert (usado inclusive para análise de locais de teste) e Test Expert (projetado para avaliar automaticamente a testabilidade de produtos e preparar dados para equipamentos de teste elétrico).

Usamos o software CAD Altium Designer (AD). Ele permite criar pontos de controle (CT) como componentes da biblioteca, definir as regras para colocar o CT no diagrama e, ao projetar uma topologia, colocar os CTs antes do rastreio. Uma abordagem semelhante pode ser aplicada em outro software CAD moderno.

Métodos de contato elétrico para testes em placas

Quatro podem ser distinguidos:

1) Manual

O método clássico no qual um especialista, usando sondas manuais, testa sequencialmente todos os circuitos. A eficiência depende das qualificações e qualidades pessoais do artista

2) "O leito das unhas"

(Do inglês “leito de unhas”, também “campo de contato”, “adaptador de agulha”, “testador de matriz” (MT)). O método pressupõe a presença de um dispositivo de conexão com contatos carregados por mola (pinos de pogo) opostos aos pontos de controle no painel. O testador pode fazer parte da linha de produção:

Ou seja, um dispositivo de desktop,

em vários projetos mecânicos: Ao garantir que todos os nós do PP testado sejam tocados por pinos de bloqueio, é possível atingir um nível de cobertura de teste próximo a 98%.

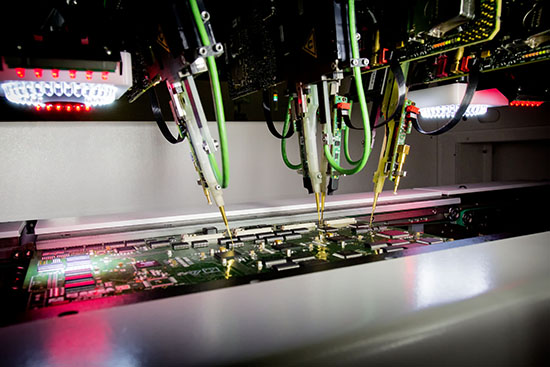

3) "Sondas voadoras"

(Do inglês. "Sondas voadoras"). O equipamento para o método da sonda voadora possui várias cabeças móveis (às vezes várias dezenas), cada uma das quais com uma sonda com acionamento axial. As sondas, de acordo com um programa criado anteriormente pelo operador, estão em contato com a placa, como resultado da qual são fornecidos energia, sinais e medições.

Ele é construído na linha ou usado separadamente, dependendo dos recursos do produto e da metodologia de teste selecionada. Parece assim, parece uma máquina de costura gigante.

4) "Matrizes voadoras"

(Do inglês "flying grid", também "flying bed of nails"). Um híbrido dos dois métodos anteriores, quando uma matriz de sonda é colocada em um carro em movimento e cada sonda também pode ter um acionamento de eixo independente. Uma ideia geral de como isso funciona pode ser obtida no

vídeo.Mais informações sobre os diferentes métodos de contato elétrico podem ser encontradas

aqui .

Várias vantagens e desvantagens dos quatro métodos são apresentadas na tabela:

Razões para escolher o teste de matriz e seus recursos

Em condições reais da realidade russa, o cliente precisa escolher entre as duas primeiras linhas da tabela, porque o equipamento para os dois últimos métodos não é barato (de 15 milhões de rublos por segunda mão) e ainda é raro na produção doméstica. Devido ao seu baixo custo, geralmente é dada preferência ao método manual, no qual apenas um desenvolvedor ou um especialista de nível comparável pode testar completamente um produto. Como resultado, os produtos podem deixar a produção completamente sem nenhum teste eletrônico ou apenas podem ser verificados ativando a "fumaça", muitas vezes já do lado do cliente. Em casos melhores, o teste manual usando snap-ins é encontrado na produção e, menos comumente, o teste automatizado em suportes de matriz.

A necessidade de um stand surgiu conosco durante o projeto

Blueberry . Este produto possui quatro saídas analógicas de precisão com calibração individual, portanto, testá-lo é uma tarefa demorada, mesmo para um engenheiro experiente. Queríamos simplificar o processo, a fim de eliminar a possibilidade de erro humano, reduzindo o procedimento a operações puramente mecânicas, garantindo testes funcionais de cada produto a partir de um lote experimental (1020 peças). O teste de matriz saiu mais caro que o teste manual, mas essa era a única maneira de garantir a operação correta de cada um. dispositivos.

Um fator importante na escolha de um método de teste pode ser a possibilidade de otimização preliminar do posicionamento dos blocos de contato (na grade de coordenadas) no software testado e minimizar seu número. Essa análise deve ser realizada antes do início do estágio de fiação da placa de circuito impresso e seu objetivo é obter o nível mais alto possível de cobertura de teste.

No nosso caso, isso não funcionou - a revisão do quadro no momento da decisão já era a quarta, tivemos que adicionar pequenos blocos de contato quase à topologia finalizada.

Com uma diminuição no número de blocos e pinos de pogo, aumenta a complexidade do desenvolvimento de software para testes funcionais. Ao mesmo tempo, uma diminuição no número de pinos de pog como um todo reduz o custo do equipamento e o tempo necessário para sua fabricação.

No nosso caso (para 42 pinos de pogo e 32 testes), o desenvolvimento exigiu 560 horas padrão, das quais 200,5 horas foram ocupadas por duas revisões do hardware, 31 - fornecimento e 328,5 - programação.

Na ausência de espaço suficiente para as almofadas no lado inferior da placa de circuito impresso, por exemplo, com uma instalação bilateral apertada de componentes, as almofadas de contato para teste também podem ser colocadas na parte superior da placa. Mas deve-se ter em mente que o custo de projetar um testador de dois lados será 1,5-2 vezes maior que o de mão única.

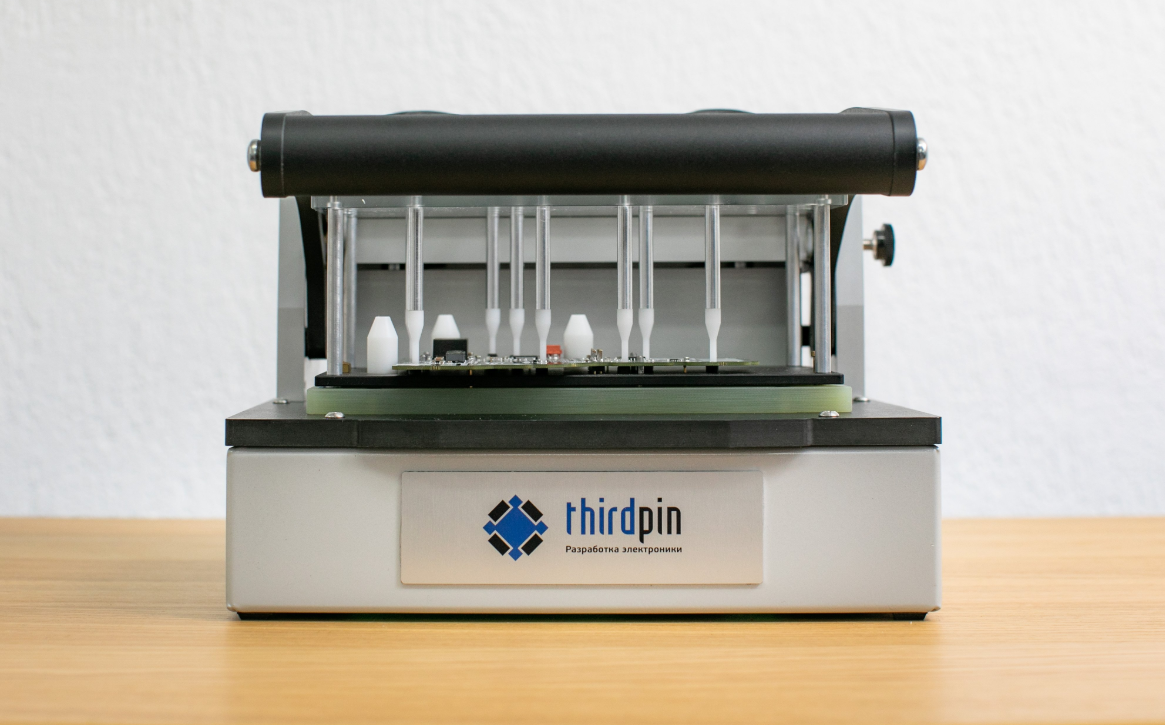

Testador de matriz Ingun MA 260 / F

As imagens do snap-in Ingun MA 260 / F adquirido e do PCB de mirtilo são mostradas nas figuras. A descrição do testador pode ser encontrada

aqui .

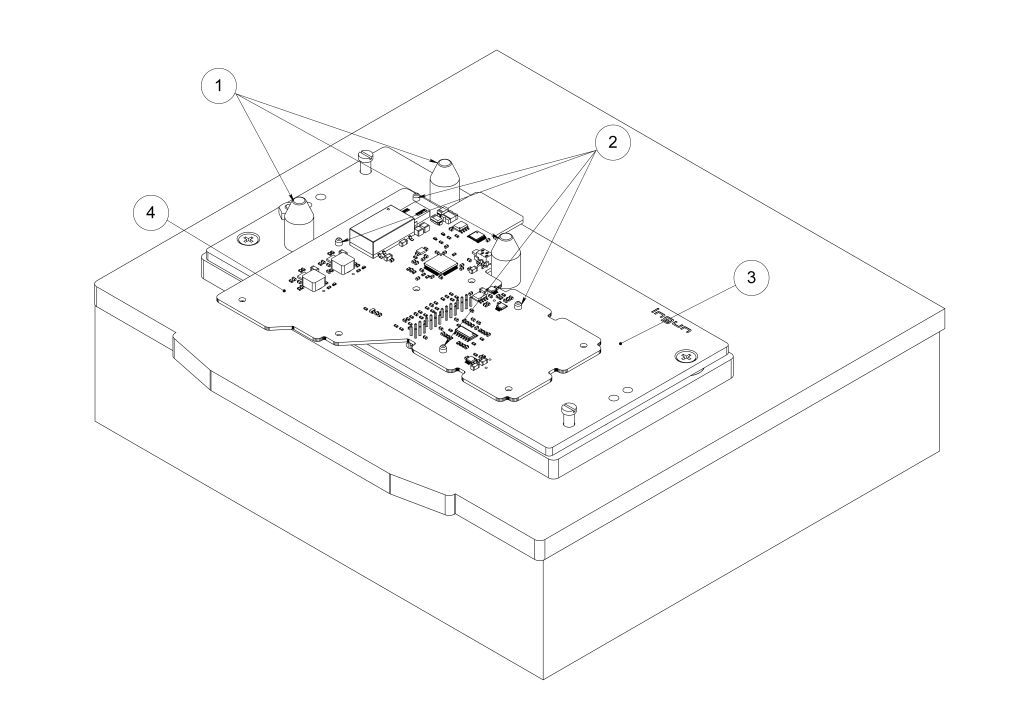

Vista em corte de um dispositivo acabado com uma placa:

No desenho, vemos: 1 - a placa de pressão, 2 - a haste de pressão (através da qual a parte superior do equipamento pressiona a placa), 3 - a placa de circuito impresso Blueberry testada, 4 - o painel móvel, 5 - a placa da sonda, 6 - a placa de teste, 7 - painel de sonda e 8 pinos de pogo. Para testar a placa “Blueberry”, finalizamos as peças de ferramentas fornecidas pela Ingun na forma de espaços em branco - uma placa de pressão, um painel móvel e um painel de sonda, e também desenvolvemos uma placa de sonda e uma placa de teste no Altium Designer.

Abaixo está uma imagem da placa Blueberry testada (item 4) em relação às hastes de posicionamento preliminar (item 1). A posição 3 nesta figura é um painel móvel e hastes de centralização da posição 2 (coletores de PCB). O instalador instala a placa de circuito impresso sem mirar até a parada das hastes de pré-posicionamento (pos. 1), depois libera a placa e pousa nas hastes de centragem mais precisas. É difícil instalar rapidamente a placa nas hastes centralizadoras sem posicionamento preliminar.

Para um posicionamento confiável da placa de circuito impresso no MT, a placa deve ter pelo menos três orifícios para posicionar os contatos (também chamados de pinos de montagem de precisão), dois dos quais devem ser colocados na diagonal. O diâmetro desses orifícios geralmente não é inferior a 3,25 mm. A distância entre a borda do contato de posicionamento e a borda do PP não é inferior a 3,18 mm e ao bloco de contato mais próximo - não inferior a 5 mm.

Os pinos do pogo devem ser selecionados de acordo com os tipos de pontos de controle na placa de circuito impresso e pedidos separadamente (eles não estão incluídos no kit do testador). Você pode variar a profundidade de aterrissagem dos pinos de pogo para componentes de altura não padrão, mas é aconselhável evitar isso (adicionando pontos de controle adicionais na placa de circuito impresso). A precisão de obter pinos de pogo nos pontos de controle (CT) é determinada com base na precisão do testador e nas tolerâncias dos tamanhos e formas das placas de testador modificadas. Os desenvolvedores de pinos de pogo dão algumas recomendações sobre tamanhos de tomografia computadorizada. Além disso, sobre a escolha dos tamanhos de TC está bem escrito

aqui .

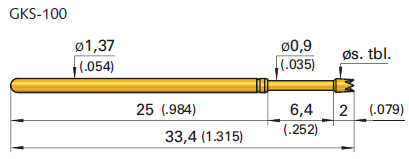

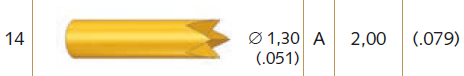

Pogopins usados (pogopins, contatos com mola)

Existem muitos tipos de pinos de pogo para testadores que diferem em tamanho, forma e relevo da superfície de contato (plana, em forma de coroa, em forma de agulha, cônica e outros), material e revestimento de pinos de pogo, garantindo sua resistência ao desgaste. A seleção correta de agulhas com cabeças correspondentes a um ponto de contato específico garante alta confiabilidade do contato durante o teste e a durabilidade dos próprios pinos pogo. Para facilitar a substituição, as sondas de contato geralmente são montadas em suportes.

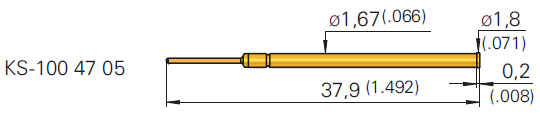

No MT para o software Chernik, são utilizados os pinos pogo Ingun GKS-100 314 130 A 1500 e os suportes KS-100 47 05 pino.

Pogo-pino GKS-100: Dica 14 pogo-pin GKS-100:

Dica 14 pogo-pin GKS-100: Suporte KS-100 para pogo GKS-100:

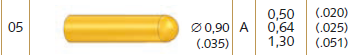

Suporte KS-100 para pogo GKS-100: Ponta 05 do suporte KS-100

Ponta 05 do suporte KS-100

Outros pogo-pins podem ser lidos nos links:

Ingun e

FEINMETALL .

Para diferentes pontos de controle no PP, diferentes tipos de pogo-pins são usados. Os pontos de controle podem ser: almofadas de contato (KP) na superfície do PP com a abertura da máscara de proteção (tipo KP para o componente smd), através de orifícios metalizados e pontas de pinos dos componentes soldados nos orifícios. Vale a pena notar que, como CT, podem ser usadas vias, incl. e mascarado.

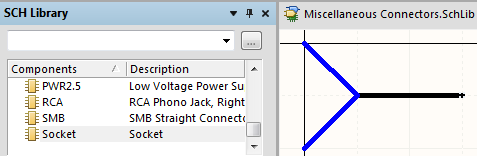

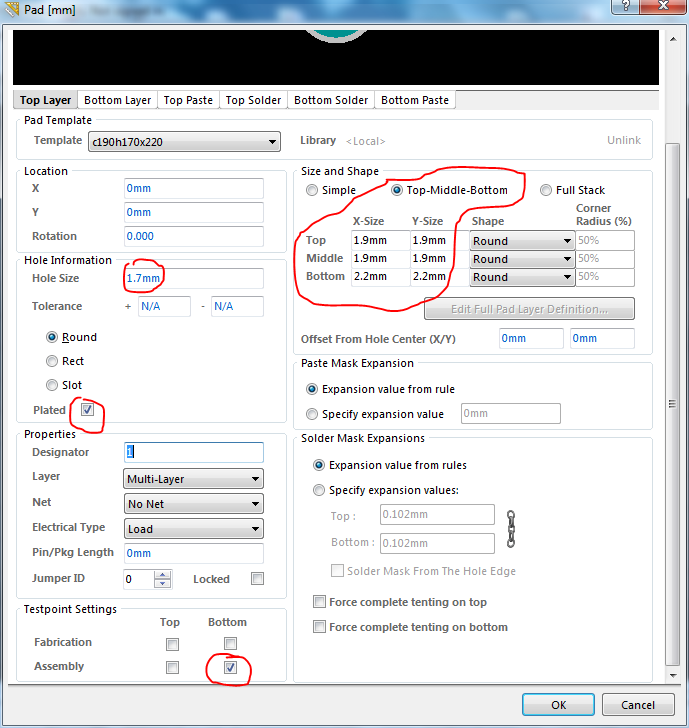

Um exemplo de criação de um ponto de controle na forma de um furo passante na placa

A criação de um CT na forma de um orifício passante no AD inclui:

1. Criando um elemento de circuito (UGO) na biblioteca .schlib. Freqüentemente, os CTs em um diagrama são representados como um soquete, e a biblioteca padrão MiscellaneousConnectors.schlib possui um elemento de circuito chamado Socket. Basta copiá-lo para sua biblioteca, dar um novo nome, alterar o parâmetro Designador Padrão, por exemplo, para KT e, para que os CTs não sejam incluídos na lista de elementos, é necessário especificar o tipo Padrão (Sem BOM).

2. É

2. É conveniente criar uma área de cobertura (na biblioteca .pcblib) usando o comando Pad. Para pogo KS-100 em laminado de fibra de vidro, a FR-4 Ingun recomenda o uso de um orifício com um diâmetro de 1,7 mm. Considere o exemplo do KP para PP de várias camadas. O tamanho do KP do lado do teste (para contato com o pog-pin) será 1,7 + 0,5 = 2,2 (onde 0,5 é a largura mínima do condutor dobrada de acordo com a classe de precisão 3). Criaremos um KP grande a partir de baixo, levando em consideração o fato de que, com mais frequência, os componentes dos pinos estão localizados na parte superior da placa e, portanto, os pinos usados durante o teste estarão na parte inferior. Nas demais camadas, o diâmetro da caixa de velocidades é de 1,9 mm. O furo deve ser metalizado. No canto inferior esquerdo, em frente ao conjunto inferior, colocamos uma marca.

3.

3. Em seguida, você precisa conectar a pegada ao elemento do circuito.

Adicionando pontos de interrupção no diagrama

No AD, é assumida a localização padrão do CT em todos os circuitos elétricos. Porém, para minimizar o número de pinos de pogo, os TCs são instalados apenas no circuito da fonte de alimentação e nos circuitos conectados às interfaces externas analógicas e digitais (exceto aquelas que podem ser testadas usando JTAG). Como já mencionado, os pinos de pogo podem entrar em contato com a caixa de engrenagens na superfície do PP, através de orifícios metalizados e condutores de pinos dos componentes soldados nos orifícios. Na fase de projeto do circuito, é possível prever o uso de condutores de pinos de componentes (soldados em orifícios) se o passo dos condutores das caixas de componentes eletrônicos (EC) corresponder à etapa de colocação dos pinos de pogo, e todos os ECs com terminais de pinos serão colocados de um lado (lado de teste). Mas isso nem sempre é conveniente, incluindo devido ao fato de que o tipo de caso às vezes é selecionado (ou alterado) durante o desenvolvimento da topologia. No estágio de desenvolvimento do esquema, recomenda-se estabelecer o número máximo necessário de TCs e, durante o desenvolvimento da topologia, remover o excesso de TCs.

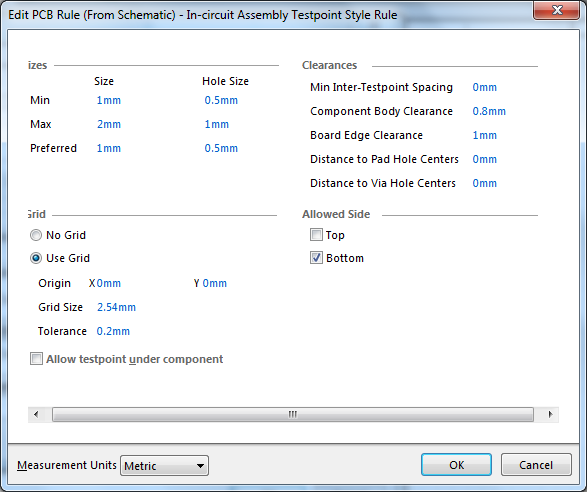

Para adicionar CT ao circuito, são usados métodos padrão para colocar um UGO. Para o projeto de ponta a ponta, podemos especificar regras de projeto no circuito (para verificação subsequente por meio da RDC). As regras para a localização dos TCs podem ser convenientemente definidas para a classe de circuitos elétricos (que incluem os circuitos testados). Em um circuito, uma classe de circuito pode ser criada usando a diretiva Place / Directive / Net Classes. A diretiva pode ser colocada em cada circuito (que deve ser incluído na classe), no barramento (mas para isso é necessário primeiro combinar todos os circuitos testados no barramento) e no cobertor. Uma manta é uma região poligonal (polígono) criada usando o comando Place / Directive / Blanket (selecionamos todas as cadeias da classe com um polígono). Não é necessário instalar uma diretiva no barramento - basta definir a opção Gerar classes líquidas para ônibus na guia Geração de classe nas opções do projeto. É mais conveniente criar classes na topologia de software, mas no AD há problemas com alterações automáticas (ao atualizar o esquema a partir da topologia) ao trabalhar com classes criadas na topologia, por isso criamos classes no esquema. Para criar uma regra para colocar o CT nas propriedades da classe (na diretiva Net Classes), clique no botão Adicionar como regra e, em seguida, no botão Editar valores da regra. Na categoria Ponto de teste, selecione Estilo do ponto de teste da montagem e clique em OK. Em seguida, defina as regras para a colocação do TC. No diagrama, o conjunto de regras para TC é um pouco menor do que na topologia - aqui você pode especificar o tamanho dos pontos, o espaçamento da grade dos pontos de teste (com tolerância), as lacunas e o lado da colocação. Como estamos considerando a preparação do teste na fase de projeto, é melhor colocar o TC na grade. Para suportes KS-100, a documentação mostra um passo de 2,54 mm. Defina a folga do corpo do componente (o espaço entre o ponto de controle e o corpo do componente) é definido como 0,8 mm e a folga da borda da placa é definida como 1 mm. As lacunas restantes não precisam ser especificadas se colocarmos o CT na grade.

Para que as classes de circuito criadas no circuito sejam transferidas para a topologia do software, a opção Gerar classes líquidas deve estar ativada na guia Geração de classe nas opções do projeto (geralmente é ativada por padrão).

Colocando pontos de controle no quadro

Colocamos os TCs antes do rastreamento, mas depois de colocar todos os outros componentes na placa. Antes de colocar, você precisa definir o espaçamento da grade do CT (no nosso caso, 2,54 mm).

Antes de colocar o CT, entraremos nas Regras de Design e lá veremos que existem 2 regras no conjunto de regras Estilo de ponto de teste de montagem: o Estilo esquemático de ponto de teste de montagem, definido no diagrama da classe, e a regra padrão AssemblyTestpoint, que se aplica a todas as cadeias. Nós removemos a regra padrão. Há uma diferença nas configurações da regra Estilo do ponto de teste da montagem na topologia (das configurações no diagrama) - aqui a opção Auxiliar do escopo da regra é exibida. No nosso caso, você precisa adicionar a marca de seleção Almofadas de orifício.

É melhor ativar a verificação de posicionamento on-line para CT em Ferramentas / Verificação de regra de projeto para controlar imediatamente as lacunas entre o CT e o gabinete CE e entre o CT e a borda da PCB. Você deve ativar o modo online especificamente para a regra Estilo do ponto de teste da montagem.

Para controlar o CT na topologia, é conveniente usar o Testpoint Manager (no menu Ferramentas). A descrição da interface pode ser encontrada

aqui .

Análise de teste de matriz

Para o teste, usamos: uma bancada de teste (como parte de um caso), um programador ST-Link / v2, um simulador de sistema de controle externo (interruptor de saída), um voltímetro de controle externo, uma fonte de alimentação de laboratório, um PC com Windows 10 e uma impressora de etiquetas adesivas.

O algoritmo de teste inclui:

- diagnóstico do sistema,

- obter a versão do software do simulador,

- fornecimento de energia e verificação do consumo de tensão e corrente,

- número de série do firmware,

- bloquear o número de série,

- firmware do carregador de inicialização,

- obtendo a versão do software do gerenciador de inicialização,

- firmware do programa principal,

- obter a versão do software do programa principal,

- tabelas de calibração da base do firmware,

- verificação nutricional,

- verificação das linhas de controle,

- verificar se a carga está ligada ou desligada,

- calibração da tensão de polarização do deslocador de fase,

- tabelas de calibração re-intermitentes,

- verificar a calibração do módulo,

- impressão de etiquetas.

Conclusão

Como resultado do teste de 1020 placas Blueberry, rejeitamos 77 placas. 44 deles não conseguiram desempenhar suas funções devido à nutrição inadequada. Como se viu, os problemas estavam relacionados às fontes de alimentação fornecidas em dois lotes separados. Em todas as diretorias rejeitadas, foram instaladas fontes pertencentes exclusivamente a uma das partes. Nossa análise mostrou que todas essas fontes durante pelo menos um teste mostraram desvios inaceitáveis dos parâmetros declarados pelo fabricante.

Além disso, foram identificados mais 33 defeitos, incluindo curtos-circuitos, pouca solda, etc. A taxa total de rejeição foi de 7,55%, o que é um bom indicador para o lote experimental. Os resultados do teste de cada produto são armazenados no banco de dados, o que permite identificar com precisão as causas das falhas.

A preparação do projeto de software Chernik para teste de matriz foi realizada na fase final do desenvolvimento da topologia, o que criou dificuldades ao adicionar blocos de contato. O tamanho da caixa de velocidades foi selecionado insuficiente (1x1mm); como resultado, houve problemas com o contato quando os pinos de engrenagem caíram além da caixa de velocidades. A proporção de tais falhas é insignificante.

Em nosso próximo projeto usando teste de matriz, colocamos a TC com antecedência.

Agora você pode conectar-se ao banco de dados do stand remotamente. O firmware do suporte possui proteção e suporta perfis com diferentes níveis de acesso às configurações, para que o suporte possa ser colocado em uma instalação de fabricação remota por contrato, que concluímos com êxito em Kaliningrado. Mas mais sobre isso em um artigo separado. thirdpin.io/testing

thirdpin.io/testing